模数转换器 (ADC)

最新课程

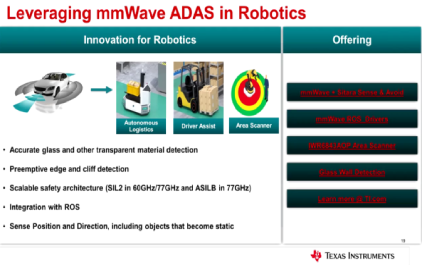

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

- 重新构想人工智能数据中心电源:从电网到终端的全链路方案

- 如何将 PurePath Console (PPC3) 用于 TI 音频转换器

- 为人形机器人提供安全高效运行的动力保障

- 《使用 C2000 IDE-Assist 从 F28x 迁移到 F29x》视频

热门课程

10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

大家好,欢迎观看 TI 高速数据转换器

实验,该实验将 帮助您了解数据

转换器采样率 与数据速率之间的

差异。

在该视频中,我们 将介绍这两个常用

术语之间的 差异,以及对

抽取和内插的 高层面说明,

由于这两项数字 数据处理技术,

可以降低或 提高转换器

数据速率。

该视频将涵盖 数据转换器输入

和样本数据 速率、将执行

抽取的数字 下变频器 -- 或 DDC --、

将执行

内插的数字上变频器 -- 或 DUC --、使用这些

功能的主要 优点和缺点、

对 JSED204B 串行器 /解串器速率的

简短介绍以及它们 如何与数据转换器

采样率和数据速率相关。

采样率是 ADC 数据转换器

对模拟输入进行采样 或 DAC 数据转换器发送

模拟输出的速度。

该速率通常 是向这些

转换器提供的 外部时钟速率。

不过,TI DAC38j84 和该系列中的

其他器件等 一些新的转换器

具有内部 PLL,它们 可以提供使用

较慢的输入时钟创建 高速采样时钟的选项。

当用户在我们的客户 EVM 使用的 GUI 中输入采样率

信息时,这有时会 使他们感到困惑。

数据速率是 ADC 的 数字输出数据的

速率 --

或 DAC 的数字 输入数据速率。

在许多情况下,这些速率与 采样时钟速率是不同的。

例如,如果用户 运行 ADS54J60 ADC

并以 1 千兆个 样本/秒的采样率

执行以二为模的 抽取,那么离开

器件的实际数据 速率将是 1 千兆个

样本/秒除以 2, 或 500 兆个样本/秒。

如果用户使用 以四为模的抽取,

那么该数据速率将 是 250 兆个样本/秒。

请记住,这是等效的 并行数据速率,而不是

该器件输出引脚的 串行器/解串器速率。

我们将在该视频的 稍后部分对此进行讨论。

如果使用新的采样率 更高的转换器,则需要

更高的数据速率。

在许多情况下,对于数据 转换器器件或将数据接收

或获取到数据 转换器中的 FPGA

ASIC 而言,这些速率太高。

另一个原因可能 是可用的 I/O 数量。

在任一情形中,通常 需要降低数据速率。

为此,使用了 内插和抽取。

在使用内插 或抽取时,

一条很好的 经验法则是,

选择可以支持信号 带宽的数据速率和

可以支持频谱 纯度的采样率。

在下一部分中,我们 将讨论抽取概念。

这将包括定义、 时间与频率的

比较、优点和 缺点以及一些

使用抽取的 示例 TI 器件。

抽取到底是什么?

在数字信号 处理中,抽取

是降低信号 采样率的过程。

术语降采样通常 指该过程中的

一个步骤,但 有时这些术语

可互换使用。

升采样或内插 可以增大采样率,

作为它们的 补充,抽取

是多速率 数字信号

处理系统中 采样率转换的

特定情况。

在对信号或其他 连续函数的样本

序列执行 抽取时,它

会产生通过 以较低速率

对信号进行采样 而获得的序列的

近似值。

这是通过从数据流中 删除一些样本来实现的。

抽取通常包括 一个数字低通或

抗混叠滤波器, 后跟抽取器。

该操作就像使用一个 模拟抗混叠滤波器,

其中心频率 等于采样率

除以抽取因子。

抽取因子 通常是大于

1 的整数或 有理分式。

采样率除以 该因子,或者

可以等效为将该 数值乘以输出数据

速率,以确定 ADC 使用的实际

采样率。

抽取用于将 采样率降低到

器件可以处理的 水平,允许使用高

采样率以实现 更灵活的频率规划,

以及提供具有更高 频谱性能的滤波。

在该幻灯片中, 在时域和频域中

展示了一个 抽取函数示例。

在执行抽取时, 会生成像 --

如频域 图所示。

在该示例中, 与采样率或

转换器相关的 信号或像将降至

采样率除以 2。

2Fs 处的信号 和像将降至 Fs,

依此类推。

然后,使用低通 滤波器来提供

抗混叠保护, 从而移除

这些像,允许以低得多的 数据速率实现干净的频谱。

数据表 通常包含显示

可用于 DDC 的 功能的方框图。

该幻灯片 显示了 TI 的

ADS54J60 ADC 中 可用的 DDC 功能示例。

正如您可以在 该图中看到的,

该器件提供 多种功能,

包括以二 为模的抽取、

以四为模的抽取、 混频器变化选项,

后跟采用四个 块的抽取和

DDC 旁路模式。

正如先前提到的, 抽取伴随着滤波,

可以在该方框 图中看到这一点。

该器件提供采用 以二为模的抽取的

低通滤波器或 高通滤波器选项。

在以四为模的 抽取中,它为

带通滤波器提供四种 不同的中心频率选项。

使用抽取具有优点, 也具有一些缺点。

优点是它可以 提供 SNR 处理增益,

信号的频率 视图保持恒定,

抽取滤波器可以 降低噪声功率,

SNR 性能会提高,此外, 由于对样本取平均值,

因此转换器的 总体噪声会降低。

不过,使用抽取是 要付出一些代价的。

缺点包括需要 更多的数字逻辑。

使用更多的数字逻辑 将消耗更大的功率,

并且总体信号 带宽容量将降低。

该幻灯片中显示了 一些具有内部抽取

功能的 TI 器件示例。

ADC32RF45 是双通道、 14 位、3 千兆个

样本/秒 ADC,具有 从 4 倍一直到 32

倍的多个抽取选项。

ADC12J4000 系列作为 单个转换器具有

从 4 倍到 32 倍的 选项,而 ADS54J60

系列仅提供 2 倍 和 4 倍的抽取。

在下一部分中,我们 将讨论内插概念。

这将包括定义、 时域视图、频域

视图、优点 和缺点以及

一些使用内插的 示例 TI 器件。

内插到底是什么?

在数字信号处理中, 内插 -- 或升采样 --

是在不影响 信号本身的

情况下增大信号 采样率的过程。

内插是一种 在一组离散的

已知数据点范围内 构建新数据点的方法。

一种用于执行内插的 典型方法如下所示 --

在每个样本之间 插入逻辑 0。

这称为零填充 或升采样。

对升采样 过程产生的

像进行滤波。

这将创建 2 倍的内插。

要实现 4 倍的内插, 请再次重复该过程。

要实现 8 倍,请再次重复,依此类推。

最好采用 该级联方法,

因为它可以提高 所需半带滤波器的

效率。

利用内插,可以 提高 DAC 输出速率。

可以进一步从 相关的频带中

消除像,从而 能够针对 DAC

实现更宽的 奈奎斯特区域

并保持合理的 数字数据速率。

该幻灯片显示了 时域中的内插

功能。

该示例显示了 在原始样本中

插入三个零。

添加零不会改变 信号的频谱内容,

它只会加重带宽的负担。

然后,使用滤波, 如低通滤波器,

可以调节 添加的样本,

以填充实际样本 之间的缺失电平,

如底部的图所示。

下一张幻灯片 显示内插的

频域视图。

顶部的图是向 原始数据添加零

之后,但在应用任何 滤波之前数字上变频

转换器的 典型输出。

第二个图 显示了 2 倍

内插低通 滤波器的效果。

该滤波器将用于对 F 数据的关联数据

像进行衰减。

通常,如果需要大于 二的抽取,则会在

多个级中完成它。

第三个图 显示了在

信号链中 使用的第二个

2 倍内插级以执行 4 倍内插的效果。

然后,第四个图 显示了第二个

级的第二个低通 滤波器之后的结果。

使用这两个 低通滤波器,

可以实现不变的 输出音调,

但具有高 得多的采样率 --

如底部的图所示。

现在,如果需要, 用户可以使用

数控振荡器或 NCO 转换到该

原始信号并 实现高得多的

中频,同时使得 性能下降极小。

数据表应 显示器件的内插

滤波器的 FIR 滤波器响应。

该幻灯片中的图 60 和图 61 显示了 DAC38J84

器件使用的 FIR0 和 FIR1 内插滤波器的

幅度频谱响应。

x 轴使用标准化标度 来表示 FIR 滤波器的

输入数据速率。

可以在数据表中 找到的其他图包含

整个级联中使用的 内插块处的复合

滤波器响应。

请注意,会产生 信号振幅损失,

因为相关的频率 接近滤波器的拐点,

从而导致 更低的 SNR。

此外,使用多个 FIR 滤波器会向数据

路径中添加延迟。

数据表中 通常会列出这些

延迟编号。

使用内插具有 优点,也具有

一些缺点。

优点是,它可以进一步 从相关的频带中消除像,

从而使对输出 进行滤波变得

更容易。

它允许更宽的 奈奎斯特区域

以实现灵活的 频率规划,

可降低噪声 频谱密度,

降低所需的 输入数据速率,

并实现更高的 输出采样率。

不过,使用内插 是要付出一些

代价的。

缺点包括需要 更多的数字逻辑,

使用更多的数字逻辑 将消耗更大的功率,

并增加延迟, 并且输入带宽

会受到内插 滤波器的限制。

TI 提供的具有 内部内插功能的

DAC 器件 示例之一

是 DAC38RF80。

如该幻灯片 所示,此功能

支持多种 不同的内插率。

该系列中的其他器件 实际上具有更多选项。

该表还向用户 展示了使用

哪些滤波器来 创建各个内插率。

接下来的这些 幻灯片将讨论

使用 JESD204B 标准的 较新高速数据

转换器的采样。

JESD204B 是数据 转换器和 FPGA

或 ASIC 等逻辑 器件之间的

标准化串行 接口,当今

开发的大多数新 高速数据转换器

都使用该接口。

在该新的标准下, JESD204B 器件能够

轻松地在千兆赫兹 范围内进行采样。

某些较新的 RFDAC 能够以 高达 9 千兆个样本/秒的

采样率进行采样。

以该采样率进行 采样具有一些缺点,

因为这要求每个 串行器/解串器

通道具有高达 90 千兆 位/秒的输入数据速率和范围。

由于 JESD204B 标准 只能支持最高

12,5 千兆个样本/秒的采样率, 因此必须降低数据速率。

为了实现该目的, 我们使用了内插。

许多 JESD DAC 具有多个

供选择的有关 内插因子的选项。

就选择用户需要 多少串行器/解串器

通道以及这些 通道将以多快的

速率运行而言,这会 向用户提供多个选项。

这对当前的 JSED204B ADC 转换器而言

不是个问题,因为它们不会 以如此快的速度进行采样。

但是,如果用户要 减少通道数,那么

这就成为一个问题, 需要使用抽取。

在该示例中, 我们展示将

使用全部 4 个 DAC、 8 个串行器/解串器

通道、内插因子 4 和最大 DAC 采样率 2,5 千兆

位/秒的 DAC38J83。

为了确定串行器 /解串器速率是否

会处于 JSED204B 标准规格之内,

我们将执行 以下计算。

首先,我们要将 JSED204B 中使用的

八位位组转换成位。

由于每个样本包含 两个八位位组,因此

对于每个 DAC,每个样本 将具有 12,500 兆个八位位组。

JSED204B 采用 8b/10b 编码, 每个八位位组将包含 10 个位。

因此这对应于 12,500 兆位/秒。

现在,总比特率 是 12,500 兆位/秒

乘以 4 个 DAC, 这等于 50

千兆位/秒。

为了使其低于 12,5 千兆位/秒,

我们选择 8 个串行器 /解串器通道,以使其降至

6,25 千兆位/秒。

另一个选项是使用 4 个通道, 这样我们就可以得到

12,5 千兆位/秒。

客户会在此处 做出折衷 --

使用较多的通道 和较低的速度,

或者使用较少的通道和较高的速率。

他们无法使用少于 4 个的通道,因为

这会超过 JSED204B 规格的 串行器/解串器数据速率。

在该幻灯片中, 您将看到一个表,

其中显示此 DAC 可以使用的最小

和最大采样率。

fData 是并行数据 离开 JSED204B 块

以及对 DAC 的数字输入 块进行馈送的速率。

fDAC 是 DAC 的 实际采样率。

fDAC 等于 fData 乘以内插因子。

由于串行器/解串器 输出使用内部 PLL,

因此它们具有最小 和最大的工作范围。

因此,JSED204B 数据转换器

具有相对较高的 最小采样率。

在许多情况下,要 使用最大采样率,

用户必须使用 某种内插,以使

串行器/解串器 速率降至 12,5 千兆

位/秒。

这是 JSED204B 标准 允许的最大采样率。

本视频到此结束。

谢谢观看。

-

未学习 1.1 数据转换器介绍 - 直流参数

未学习 1.1 数据转换器介绍 - 直流参数

-

未学习 1.2 数据转换器介绍 - 交流和直流参数

未学习 1.2 数据转换器介绍 - 交流和直流参数

-

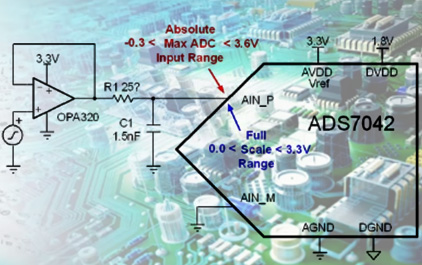

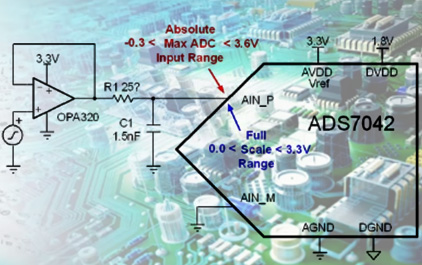

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

-

未学习 2.2.1 单端驱动电路分析

未学习 2.2.1 单端驱动电路分析

-

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

-

未学习 2.3.1 交越失真实验所需硬件软件

未学习 2.3.1 交越失真实验所需硬件软件

-

未学习 2.3.2 交越失真实验软件设置

未学习 2.3.2 交越失真实验软件设置

-

未学习 2.3.3 交越失真实验结果

未学习 2.3.3 交越失真实验结果

-

未学习 2.4.1 仪表放大器输入范围计算

未学习 2.4.1 仪表放大器输入范围计算

-

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

-

未学习 2.5.1 全差分放大器及失真

未学习 2.5.1 全差分放大器及失真

-

未学习 2.5.2 全差分驱动电路设计

未学习 2.5.2 全差分驱动电路设计

-

未学习 3.1 误差分析背后的统计学知识

未学习 3.1 误差分析背后的统计学知识

-

未学习 3.2 理解与校准ADC系统的偏移和增益误差

未学习 3.2 理解与校准ADC系统的偏移和增益误差

-

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

-

未学习 4.1 计算ADC系统的总噪声

未学习 4.1 计算ADC系统的总噪声

-

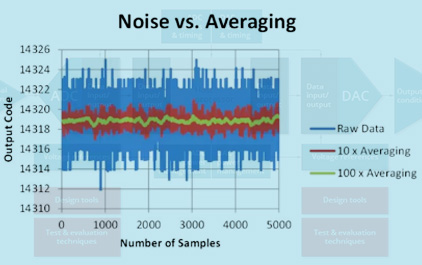

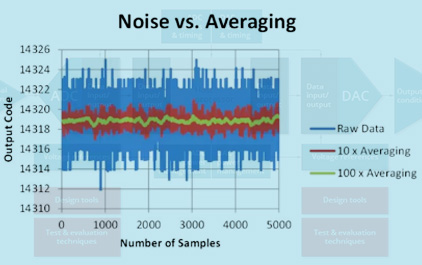

未学习 4.2 动手实验-ADC噪声

未学习 4.2 动手实验-ADC噪声

-

未学习 4.3 ADC 系统中的噪声

未学习 4.3 ADC 系统中的噪声

-

未学习 4.4 ADC 噪声测量、方法和参数

未学习 4.4 ADC 噪声测量、方法和参数

-

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

-

未学习 4.10 ADC 系统中的参考噪声简介

未学习 4.10 ADC 系统中的参考噪声简介

-

未学习 4.11 参考噪声对信号链性能的影响

未学习 4.11 参考噪声对信号链性能的影响

-

未学习 4.12 降低参考噪声

未学习 4.12 降低参考噪声

-

未学习 5.1 频域介绍

未学习 5.1 频域介绍

-

未学习 5.2 快速傅立叶变换及加窗函数

未学习 5.2 快速傅立叶变换及加窗函数

-

未学习 5.3 改善频率指标的方法:相干采样及滤波

未学习 5.3 改善频率指标的方法:相干采样及滤波

-

未学习 5.4 混叠及抗混叠滤波器

未学习 5.4 混叠及抗混叠滤波器

-

未学习 5.5 实验 - 混叠和抗混叠滤波器

未学习 5.5 实验 - 混叠和抗混叠滤波器

-

未学习 6.1 SAR ADC及其器件选型

未学习 6.1 SAR ADC及其器件选型

-

未学习 6.2 驱动放大器的选型和验证

未学习 6.2 驱动放大器的选型和验证

-

未学习 6.3 建立SAR ADC的仿真模型

未学习 6.3 建立SAR ADC的仿真模型

-

未学习 6.4 如何计算RC滤波器的值

未学习 6.4 如何计算RC滤波器的值

-

未学习 6.5 最终的仿真验证

未学习 6.5 最终的仿真验证

-

未学习 6.6 滤波器RC选型的理论计算方法

未学习 6.6 滤波器RC选型的理论计算方法

-

未学习 6.7 R-C组件选择背后的数学

未学习 6.7 R-C组件选择背后的数学

-

未学习 7.1 电压基准概述

未学习 7.1 电压基准概述

-

未学习 7.2 参考驱动器拓扑概述

未学习 7.2 参考驱动器拓扑概述

-

未学习 7.3 了解SAR参考输入模型

未学习 7.3 了解SAR参考输入模型

-

未学习 7.4 开发SAR输入参考模型

未学习 7.4 开发SAR输入参考模型

-

未学习 7.5 驱动参考实验

未学习 7.5 驱动参考实验

-

未学习 7.6 ADC:SAR 基准输入 - CDAC

未学习 7.6 ADC:SAR 基准输入 - CDAC

-

未学习 8.1 SAR ADC功率调节

未学习 8.1 SAR ADC功率调节

-

未学习 8.2 动手实验 - 系统功率调节

未学习 8.2 动手实验 - 系统功率调节

-

未学习 9.1 EOS和ESD

未学习 9.1 EOS和ESD

-

未学习 9.3 向TINA 导入二极管PSpice模型

未学习 9.3 向TINA 导入二极管PSpice模型

-

未学习 9.4 通过高压放大器保护低压ADC

未学习 9.4 通过高压放大器保护低压ADC

-

未学习 9.5 保护低压ADC-改进的解决方案

未学习 9.5 保护低压ADC-改进的解决方案

-

未学习 9.6 用TVS二极管保护ADC

未学习 9.6 用TVS二极管保护ADC

-

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 10.4 带宽与频率 - 子采样概念

未学习 10.4 带宽与频率 - 子采样概念

-

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)11.1 ADC 系统中的噪声

未学习 (中文)11.1 ADC 系统中的噪声

-

未学习 (中文)11.3 ADC 噪声测量、方法和参数

未学习 (中文)11.3 ADC 噪声测量、方法和参数

-

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

-

未学习 (中文)11.9 ADC 系统中的参考噪声简介

未学习 (中文)11.9 ADC 系统中的参考噪声简介

-

未学习 (中文)11.10 参考噪声对信号链性能的影响

未学习 (中文)11.10 参考噪声对信号链性能的影响

-

未学习 (中文)11.11 降低参考噪声

未学习 (中文)11.11 降低参考噪声

-

未学习 动手实验:放大器稳定和电荷桶滤波器设计

未学习 动手实验:放大器稳定和电荷桶滤波器设计

-

未学习 无需放大器即可驱动 SAR ADC

未学习 无需放大器即可驱动 SAR ADC

-

未学习 外部EOS保护装置

未学习 外部EOS保护装置

-

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

-

未学习 (中文)6.7 R-C组件选择背后的数学

未学习 (中文)6.7 R-C组件选择背后的数学

-

未学习 (中文)7.1 电压基准概述

未学习 (中文)7.1 电压基准概述

-

未学习 (中文)7.3 SAR 基准输入 - CDAC

未学习 (中文)7.3 SAR 基准输入 - CDAC

-

未学习 (中文)7.4 了解SAR参考输入模型

未学习 (中文)7.4 了解SAR参考输入模型

-

未学习 (中文)7.5 开发SAR输入参考模型

未学习 (中文)7.5 开发SAR输入参考模型

-

未学习 (中文)7.6 驱动参考实验

未学习 (中文)7.6 驱动参考实验

-

未学习 (中文)8.1 SAR ADC功率调节

未学习 (中文)8.1 SAR ADC功率调节

-

未学习 (中文)8.2 动手实验 - 系统功率调节

未学习 (中文)8.2 动手实验 - 系统功率调节

-

未学习 (中文)9.1 EOS和ESD

未学习 (中文)9.1 EOS和ESD

-

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

-

未学习 (中文)9.4 通过高压放大器保护低压ADC

未学习 (中文)9.4 通过高压放大器保护低压ADC

-

未学习 (中文)9.5 保护低压ADC-改进的解决方案

未学习 (中文)9.5 保护低压ADC-改进的解决方案

-

未学习 (中文)9.6 用TVS二极管保护ADC

未学习 (中文)9.6 用TVS二极管保护ADC

-

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 (中文)10.4 带宽与频率 - 子采样概念

未学习 (中文)10.4 带宽与频率 - 子采样概念

-

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)了解 ADC 系统中的电源噪声

未学习 (中文)了解 ADC 系统中的电源噪声

-

未学习 (中文)时钟噪声如何影响精密 ADC 测量

未学习 (中文)时钟噪声如何影响精密 ADC 测量

-

未学习 (中文)电源噪声降低技术

未学习 (中文)电源噪声降低技术

-

未学习 保护 Delta-Sigma ADC:RTD 概述

未学习 保护 Delta-Sigma ADC:RTD 概述

-

未学习 保护 Delta-Sigma ADC:输入保护电路操作

未学习 保护 Delta-Sigma ADC:输入保护电路操作

-

未学习 保护 Δ-Σ 元件选型

未学习 保护 Δ-Σ 元件选型

-

未学习 利用 TVS 保护 Δ-Σ:性能影响

未学习 利用 TVS 保护 Δ-Σ:性能影响

-

未学习 保护 Δ-Σ ADC:特殊输入范围

未学习 保护 Δ-Σ ADC:特殊输入范围

-

未学习 PCB 布线阻抗匹配

未学习 PCB 布线阻抗匹配

-

未学习 去耦电容

未学习 去耦电容

-

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

-

未学习 电磁兼容测试方法及标准

未学习 电磁兼容测试方法及标准

-

未学习 3线RTD系统的挑战

未学习 3线RTD系统的挑战

-

未学习 设计软件与硬件可配置的多 RTD 测量系统

未学习 设计软件与硬件可配置的多 RTD 测量系统

-

未学习 混叠和抗混叠滤波器

未学习 混叠和抗混叠滤波器