模数转换器 (ADC)

最新课程

- F29 实时 MCU

- 如何使用 Edge AI Studio 进行基于雷达的表面分类

- 介绍 1L 调制

- HSS Smart Configurator GUI 概述

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

热门课程

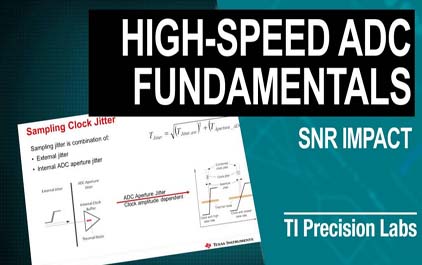

10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

大家好,欢迎观看 TI 高精度实验室视频,

其中讨论高速 数据转换器的

时钟抖动注意事项。

在本视频中,我们 将讨论什么是抖动,

它的来源,以及它 如何影响高速数据

转换器的噪声性能。

我们还将探究 如何计算抖动,

以及执行怎样的步骤以最大 程度地减小噪声性能下降。

在采样理论中, 高速 ADC 使用

外部时钟信号对 输入信号进行采样。

时钟边沿具有通常 称为抖动的时序

不确定性,这会降低 ADC 的噪声性能。

在采样过程中, 采样时钟边沿的

时序不确定性会 导致振幅误差。

对于给定量的 抖动,误差会

随着输入频率的 增大而变大。

因此,ADC 的 噪声或 SNR

性能下降对 抖动量和输入

信号的频率 都很敏感。

采样时钟抖动 包含两个分量,

即来自非理想 时钟源的外部

抖动和内部 ADC 孔径抖动。

ADC 孔径抖动 主要源自内部

时钟缓冲器的 热噪声,而孔径

抖动通常 取决于向

ADC 提供的时钟 信号振幅。

需要将外部抖动 和内部 ADC 孔径

抖动结合在 一起才能确定

ADC SNR 降低量。

系统设计人员 使用一个著名的

公式来估算时钟 抖动导致的噪声

性能下降。

SNR 抖动下降的 计算表达式为:

-20*log10[2π*输入频率*抖动]

。

正如先前 提到的,该

公式还证明 抖动导致的

SNR 下降主要 取决于输入

频率和抖动量。

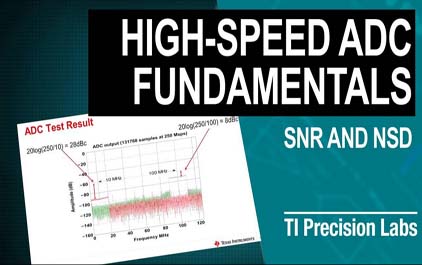

下面的示例图 显示了一个

具有大约 73dB 热 噪声的 14 位 ADC。

这是粉色的 水平线。

此外,我们可以 看到四条显示抖动

导致的 SNR 降低的迹线, 抖动时长分别为 50、

100、200 和 400 飞秒。

例如,对于 400 飞秒的 采样时钟抖动,

当输入频率从 10 兆赫兹更改为

100 兆赫兹时, 抖动导致的

SNR 会降低 20dB。

ADC 的本底噪声 由三个不同的

因素决定。

第一个因素是 ADC 量化噪声。

通常,选择 ADC 的 输出分辨率时

应满足以下 条件:量化噪声

不会使 ADC SNR 显著降低。

在高速 ADC 中, 有效位数

或 ENOB 通常 远低于

实际的 ADC 分辨率。

第二个因素是 ADC 热噪声。

热噪声是 ADC 的固有

本底噪声。

第三个因素是抖动降级。

这是时钟边沿时序 不确定性导致的噪声

增加。

返回到前面有关 14 位 ADC 的示例,

我们的 14 位 ADC 具有大约

73dB 的热噪声和 86dB 的量化噪声。

总采样时钟 抖动为 400 飞秒。

如下图所示, 在高达约 30

兆赫兹的输入 频率下,产生的

SNR 受约 73dB 的 热噪声限制。

86dB 的量化 大小完全

不会影响结果。

随着输入频率 不断增加,

抖动降级将占据 主导地位,并最终

完全限制它。

如果时钟从 400 飞秒提高

至 100 飞秒,那么 即使在 200 兆

赫兹的输入 频率下,抖动

影响一点儿也不明显。

对于射频采样 转换器,时钟

抖动降级是一个非常 重要的考虑因素。

外部时钟 信号的抖动

可以通过对其相位 噪声进行积分来计算。

要进行该计算, 必须设置积分

上限和积分下限。

积分下限通常 由应用程序

设置。

例如,如果应用

使用 FFT 处理, 那么下限由

FFT bin 大小 设置,如左侧的

图所示。

如果是电信 应用,那么下限

由频道间隔设置。

例如,在 GSM 通信中,频道

间隔是 200 千赫兹。

任何比这更接近的 相位噪声都是不相关的。

右侧的图 显示了积分

下限可能对总抖动 数有显著的影响,因此

正确设置积分 下限非常重要。

积分上限 取决于一些

不同的变量。

如果在时钟输入端 使用带通滤波器,

那么上限由滤波器 带宽进行设置。

如果未对时钟输入进行 滤波,那么从理论上而言,

需要将相位 噪声积分至

时钟速率两倍的 偏移频率。

但内部时钟输入 具有有限的带宽,

因此积分至时钟 速率的两倍是

最糟糕的情形。

正如在上面的 图中看到的,

外部本底噪声会显著 增加总时钟抖动数。

在 TI,只要可以,我们 就在 ADC 时钟输入端

使用带通滤波器,以 限制本底噪声降级。

作为一个简单的 实验,我向 ADS 5463 的

时钟输入添加了白噪声, 然后我使用不同的低通

滤波器来演示对 DC 宽本底噪声的影响。

底部的图展示了 相关结果。

不出所料,在不 使用滤波器时,

发生了最糟糕的 本底噪声降级。

随着我将时钟 输入端的低通

滤波器转角频率 从 300 兆赫兹

降低至 1 兆赫兹, 产生的总本底噪声

降级变得越来越好。

或许控制时钟 抖动导致的

本底噪声 降级的更佳

方法是在 频域中查看它。

在采样过程中, 会向输入信号

添加时钟信号相位 噪声,但时钟相位噪声

振幅也会以 20*log (输入频率/时钟频率) 的

因数进行缩放。

与时域分析中的 情况类似,如果

输入频率 增加 10 倍,

那么在添加到 ADC 的热噪声

之前,时钟相位噪声 振幅会增加 20dB。

很显然,固有时钟 噪声振幅越大,

这会直接导致 更高的抖动,

ADC 本底噪声 降级就越糟糕。

那么,为何时钟 抖动或相位噪声

对于接收器性能 而言如此重要?

典型的接收器 用例是阻断情况,

其中接收器需要 在存在高功率带内

干扰信号的情况下 检测微小的目标信号。

该干扰信号位于 所需的通带内,

因此无法 将其滤除。

由于我们无法对 ADC 输入进行过驱

或使其饱和,因此 高功率干扰信号会

限制可应用至微小 目标信号的前端增益量。

因此,ADC 本身的

本底噪声需要 尽可能低。

正如可以在 下面的图中

看到的,时钟相位 噪声被调制到

全功率干扰信号上, 然后该时钟相位

噪声开始直接限制 能够检测到多小的

目标信号。

随着输入频率 或时钟相位噪声

不断增大,ADC 的组合 本底噪声也会不断增大。

这样就使检测微小的 目标信号变得越来越难。

那么,可以采取什么措施 来最大程度地减小时钟

噪声对 ADC SNR 的影响呢?

系统设计 人员可以

在一些不同的 选项中进行选择。

首选,选择具有足够低的 抖动或相位噪声的

时钟源。

然后,使用具有 低插入损耗的

带通滤波器,从而 限制宽带噪声降级。

第三,确保 ADC 时钟 输入引脚上的时钟

振幅足够高,从而 不会降低 ADC 孔径

抖动。

本视频到此结束。

谢谢观看。 175

-

未学习 1.1 数据转换器介绍 - 直流参数

未学习 1.1 数据转换器介绍 - 直流参数

-

未学习 1.2 数据转换器介绍 - 交流和直流参数

未学习 1.2 数据转换器介绍 - 交流和直流参数

-

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

-

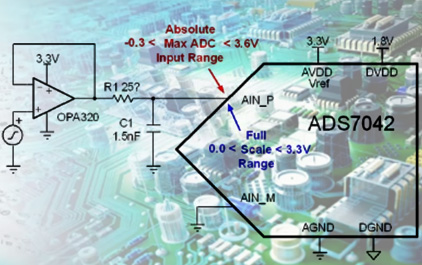

未学习 2.2.1 单端驱动电路分析

未学习 2.2.1 单端驱动电路分析

-

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

-

未学习 2.3.1 交越失真实验所需硬件软件

未学习 2.3.1 交越失真实验所需硬件软件

-

未学习 2.3.2 交越失真实验软件设置

未学习 2.3.2 交越失真实验软件设置

-

未学习 2.3.3 交越失真实验结果

未学习 2.3.3 交越失真实验结果

-

未学习 2.4.1 仪表放大器输入范围计算

未学习 2.4.1 仪表放大器输入范围计算

-

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

-

未学习 2.5.1 全差分放大器及失真

未学习 2.5.1 全差分放大器及失真

-

未学习 2.5.2 全差分驱动电路设计

未学习 2.5.2 全差分驱动电路设计

-

未学习 3.1 误差分析背后的统计学知识

未学习 3.1 误差分析背后的统计学知识

-

未学习 3.2 理解与校准ADC系统的偏移和增益误差

未学习 3.2 理解与校准ADC系统的偏移和增益误差

-

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

-

未学习 4.1 计算ADC系统的总噪声

未学习 4.1 计算ADC系统的总噪声

-

未学习 4.2 动手实验-ADC噪声

未学习 4.2 动手实验-ADC噪声

-

未学习 4.3 ADC 系统中的噪声

未学习 4.3 ADC 系统中的噪声

-

未学习 4.4 ADC 噪声测量、方法和参数

未学习 4.4 ADC 噪声测量、方法和参数

-

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

-

未学习 4.10 ADC 系统中的参考噪声简介

未学习 4.10 ADC 系统中的参考噪声简介

-

未学习 4.11 参考噪声对信号链性能的影响

未学习 4.11 参考噪声对信号链性能的影响

-

未学习 4.12 降低参考噪声

未学习 4.12 降低参考噪声

-

未学习 5.1 频域介绍

未学习 5.1 频域介绍

-

未学习 5.2 快速傅立叶变换及加窗函数

未学习 5.2 快速傅立叶变换及加窗函数

-

未学习 5.3 改善频率指标的方法:相干采样及滤波

未学习 5.3 改善频率指标的方法:相干采样及滤波

-

未学习 5.4 混叠及抗混叠滤波器

未学习 5.4 混叠及抗混叠滤波器

-

未学习 5.5 实验 - 混叠和抗混叠滤波器

未学习 5.5 实验 - 混叠和抗混叠滤波器

-

未学习 6.1 SAR ADC及其器件选型

未学习 6.1 SAR ADC及其器件选型

-

未学习 6.2 驱动放大器的选型和验证

未学习 6.2 驱动放大器的选型和验证

-

未学习 6.3 建立SAR ADC的仿真模型

未学习 6.3 建立SAR ADC的仿真模型

-

未学习 6.4 如何计算RC滤波器的值

未学习 6.4 如何计算RC滤波器的值

-

未学习 6.5 最终的仿真验证

未学习 6.5 最终的仿真验证

-

未学习 6.6 滤波器RC选型的理论计算方法

未学习 6.6 滤波器RC选型的理论计算方法

-

未学习 6.7 R-C组件选择背后的数学

未学习 6.7 R-C组件选择背后的数学

-

未学习 7.1 电压基准概述

未学习 7.1 电压基准概述

-

未学习 7.2 参考驱动器拓扑概述

未学习 7.2 参考驱动器拓扑概述

-

未学习 7.3 了解SAR参考输入模型

未学习 7.3 了解SAR参考输入模型

-

未学习 7.4 开发SAR输入参考模型

未学习 7.4 开发SAR输入参考模型

-

未学习 7.5 驱动参考实验

未学习 7.5 驱动参考实验

-

未学习 7.6 ADC:SAR 基准输入 - CDAC

未学习 7.6 ADC:SAR 基准输入 - CDAC

-

未学习 8.1 SAR ADC功率调节

未学习 8.1 SAR ADC功率调节

-

未学习 8.2 动手实验 - 系统功率调节

未学习 8.2 动手实验 - 系统功率调节

-

未学习 9.1 EOS和ESD

未学习 9.1 EOS和ESD

-

未学习 9.3 向TINA 导入二极管PSpice模型

未学习 9.3 向TINA 导入二极管PSpice模型

-

未学习 9.4 通过高压放大器保护低压ADC

未学习 9.4 通过高压放大器保护低压ADC

-

未学习 9.5 保护低压ADC-改进的解决方案

未学习 9.5 保护低压ADC-改进的解决方案

-

未学习 9.6 用TVS二极管保护ADC

未学习 9.6 用TVS二极管保护ADC

-

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

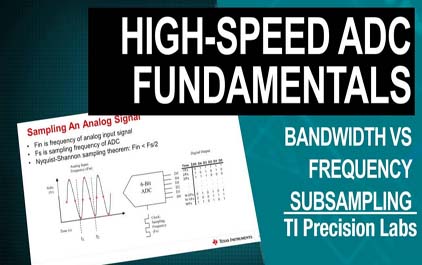

未学习 10.4 带宽与频率 - 子采样概念

未学习 10.4 带宽与频率 - 子采样概念

-

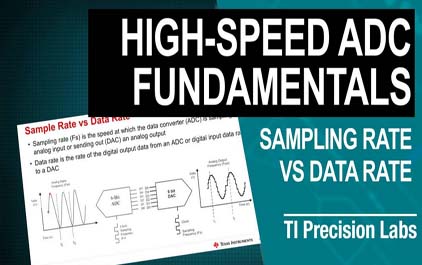

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)11.1 ADC 系统中的噪声

未学习 (中文)11.1 ADC 系统中的噪声

-

未学习 (中文)11.3 ADC 噪声测量、方法和参数

未学习 (中文)11.3 ADC 噪声测量、方法和参数

-

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

-

未学习 (中文)11.9 ADC 系统中的参考噪声简介

未学习 (中文)11.9 ADC 系统中的参考噪声简介

-

未学习 (中文)11.10 参考噪声对信号链性能的影响

未学习 (中文)11.10 参考噪声对信号链性能的影响

-

未学习 (中文)11.11 降低参考噪声

未学习 (中文)11.11 降低参考噪声

-

未学习 动手实验:放大器稳定和电荷桶滤波器设计

未学习 动手实验:放大器稳定和电荷桶滤波器设计

-

未学习 无需放大器即可驱动 SAR ADC

未学习 无需放大器即可驱动 SAR ADC

-

未学习 外部EOS保护装置

未学习 外部EOS保护装置

-

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

-

未学习 (中文)6.7 R-C组件选择背后的数学

未学习 (中文)6.7 R-C组件选择背后的数学

-

未学习 (中文)7.1 电压基准概述

未学习 (中文)7.1 电压基准概述

-

未学习 (中文)7.3 SAR 基准输入 - CDAC

未学习 (中文)7.3 SAR 基准输入 - CDAC

-

未学习 (中文)7.4 了解SAR参考输入模型

未学习 (中文)7.4 了解SAR参考输入模型

-

未学习 (中文)7.5 开发SAR输入参考模型

未学习 (中文)7.5 开发SAR输入参考模型

-

未学习 (中文)7.6 驱动参考实验

未学习 (中文)7.6 驱动参考实验

-

未学习 (中文)8.1 SAR ADC功率调节

未学习 (中文)8.1 SAR ADC功率调节

-

未学习 (中文)8.2 动手实验 - 系统功率调节

未学习 (中文)8.2 动手实验 - 系统功率调节

-

未学习 (中文)9.1 EOS和ESD

未学习 (中文)9.1 EOS和ESD

-

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

-

未学习 (中文)9.4 通过高压放大器保护低压ADC

未学习 (中文)9.4 通过高压放大器保护低压ADC

-

未学习 (中文)9.5 保护低压ADC-改进的解决方案

未学习 (中文)9.5 保护低压ADC-改进的解决方案

-

未学习 (中文)9.6 用TVS二极管保护ADC

未学习 (中文)9.6 用TVS二极管保护ADC

-

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 (中文)10.4 带宽与频率 - 子采样概念

未学习 (中文)10.4 带宽与频率 - 子采样概念

-

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)了解 ADC 系统中的电源噪声

未学习 (中文)了解 ADC 系统中的电源噪声

-

未学习 (中文)时钟噪声如何影响精密 ADC 测量

未学习 (中文)时钟噪声如何影响精密 ADC 测量

-

未学习 (中文)电源噪声降低技术

未学习 (中文)电源噪声降低技术

-

未学习 保护 Delta-Sigma ADC:RTD 概述

未学习 保护 Delta-Sigma ADC:RTD 概述

-

未学习 保护 Delta-Sigma ADC:输入保护电路操作

未学习 保护 Delta-Sigma ADC:输入保护电路操作

-

未学习 保护 Δ-Σ 元件选型

未学习 保护 Δ-Σ 元件选型

-

未学习 利用 TVS 保护 Δ-Σ:性能影响

未学习 利用 TVS 保护 Δ-Σ:性能影响

-

未学习 保护 Δ-Σ ADC:特殊输入范围

未学习 保护 Δ-Σ ADC:特殊输入范围

-

未学习 PCB 布线阻抗匹配

未学习 PCB 布线阻抗匹配

-

未学习 去耦电容

未学习 去耦电容

-

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

-

未学习 电磁兼容测试方法及标准

未学习 电磁兼容测试方法及标准

-

未学习 3线RTD系统的挑战

未学习 3线RTD系统的挑战

-

未学习 设计软件与硬件可配置的多 RTD 测量系统

未学习 设计软件与硬件可配置的多 RTD 测量系统

-

未学习 混叠和抗混叠滤波器

未学习 混叠和抗混叠滤波器