模数转换器 (ADC)

最新课程

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

- 重新构想人工智能数据中心电源:从电网到终端的全链路方案

- 如何将 PurePath Console (PPC3) 用于 TI 音频转换器

- 为人形机器人提供安全高效运行的动力保障

- 《使用 C2000 IDE-Assist 从 F28x 迁移到 F29x》视频

热门课程

2.4.2 使用软件验证仪表放大器输入共模范围

欢迎参加 TI 高精密实验室

本节将讨论使用仪表放大器

驱动 SAR 型 ADC 的设计考虑

下面我们讨论如何使用软件

来得到任意条件下的共模和摆幅的关系

软件的界面如图所示

这个软件可以计算不同条件下

仪表放大器的输出范围

首先选择你使用的放大器

然后输入供电电压、增益和参考电压

点击绘制按钮

然后输入共模电压

注意到共模电压为纵坐标轴

而输出电压为横坐标轴

而输出电压为横坐标轴

选择的共模电压为一条绿色的水平线

输出摆幅的限制就是绿色的线条和

红色与白色线条的交点

并且这个交点的值也会显示在

输出最大和最小两个文本框里面

可以看到输出摆幅是 -14.8 到 14.2V

这个范围大于 ±10V

所以设计不会有摆幅的限制

通常 INA 电路遇到最多的问题

就是摆幅限制的问题

所以设计的时候

使用这个软件工具确认一下

非常有帮助

非常有帮助

我们换一种单极性输入的电压模式来讨论

例如 1mV 到 20mV 的输入范围

需要使用仪表放大器转换为 ±50V

通过仪表放大器的输入输出关系公式

输入差分电压为 20mV

输出最大电压

最小为 20V 的峰峰值

所以增益还是 1000

那么问题来了

输入 21mV 的电压

放大 1000 倍

输出将会是 21V

而我们需要 10V

所以通过调节参考电压来实现

通过分析计算发现

参考电压为 -11V 的时候

可以调节到 ±10V 的范围

-11V 的基准电压

可以通过电阻分压器和运放

缓冲器来实现

为啥要用缓冲器呢

因为 INA 的 REF 端为低阻抗节点

直接使用分压器会产生误差

再来看一个违反共模限制的例子

这个电路的目的是将 0 到 10mV 的信号

转换为 0 到 10V

电路的应用测量是

12V 电源轨的高边电流

将输入条件输入到软件中发现

当共模电压为 12 V的时候

输出摆幅仅仅为 ±6.4V

所以这样的配置

放大器得不到 0 到 10V 的输出摆幅范围

可能需要重新选择其他的 INA 实现

前面讨论了使用 INA 驱动带有 PGA 的

SAR 型 ADC 的方法

因为 PGA 本身就是一个高速的缓冲器

使用 INA 驱动没有问题

但是如果 INA 驱动

低成本高精度的开关电容输入型的 SAR 型 ADC

就需要级联一个额外的高速缓冲器

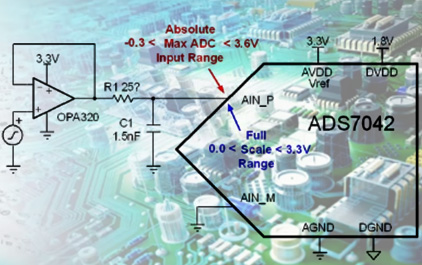

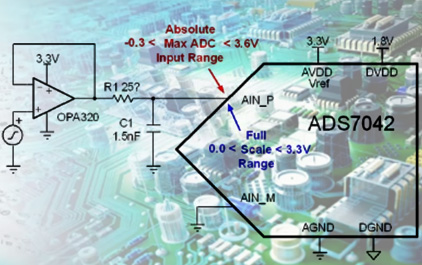

这里使用了 OPA320

这个高速缓冲器是为

内部的采样保持电路服务的

后面我们会做进一步的讨论

是关于如何选择缓冲器和 RC 电路

好的,本章节就到这里

你也可以通过检测题来提高您对本章节的理解

-

未学习 1.1 数据转换器介绍 - 直流参数

未学习 1.1 数据转换器介绍 - 直流参数

-

未学习 1.2 数据转换器介绍 - 交流和直流参数

未学习 1.2 数据转换器介绍 - 交流和直流参数

-

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

-

未学习 2.2.1 单端驱动电路分析

未学习 2.2.1 单端驱动电路分析

-

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

-

未学习 2.3.1 交越失真实验所需硬件软件

未学习 2.3.1 交越失真实验所需硬件软件

-

未学习 2.3.2 交越失真实验软件设置

未学习 2.3.2 交越失真实验软件设置

-

未学习 2.3.3 交越失真实验结果

未学习 2.3.3 交越失真实验结果

-

未学习 2.4.1 仪表放大器输入范围计算

未学习 2.4.1 仪表放大器输入范围计算

-

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

-

未学习 2.5.1 全差分放大器及失真

未学习 2.5.1 全差分放大器及失真

-

未学习 2.5.2 全差分驱动电路设计

未学习 2.5.2 全差分驱动电路设计

-

未学习 3.1 误差分析背后的统计学知识

未学习 3.1 误差分析背后的统计学知识

-

未学习 3.2 理解与校准ADC系统的偏移和增益误差

未学习 3.2 理解与校准ADC系统的偏移和增益误差

-

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

-

未学习 4.1 计算ADC系统的总噪声

未学习 4.1 计算ADC系统的总噪声

-

未学习 4.2 动手实验-ADC噪声

未学习 4.2 动手实验-ADC噪声

-

未学习 4.3 ADC 系统中的噪声

未学习 4.3 ADC 系统中的噪声

-

未学习 4.4 ADC 噪声测量、方法和参数

未学习 4.4 ADC 噪声测量、方法和参数

-

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

-

未学习 4.10 ADC 系统中的参考噪声简介

未学习 4.10 ADC 系统中的参考噪声简介

-

未学习 4.11 参考噪声对信号链性能的影响

未学习 4.11 参考噪声对信号链性能的影响

-

未学习 4.12 降低参考噪声

未学习 4.12 降低参考噪声

-

未学习 5.1 频域介绍

未学习 5.1 频域介绍

-

未学习 5.2 快速傅立叶变换及加窗函数

未学习 5.2 快速傅立叶变换及加窗函数

-

未学习 5.3 改善频率指标的方法:相干采样及滤波

未学习 5.3 改善频率指标的方法:相干采样及滤波

-

未学习 5.4 混叠及抗混叠滤波器

未学习 5.4 混叠及抗混叠滤波器

-

未学习 5.5 实验 - 混叠和抗混叠滤波器

未学习 5.5 实验 - 混叠和抗混叠滤波器

-

未学习 6.1 SAR ADC及其器件选型

未学习 6.1 SAR ADC及其器件选型

-

未学习 6.2 驱动放大器的选型和验证

未学习 6.2 驱动放大器的选型和验证

-

未学习 6.3 建立SAR ADC的仿真模型

未学习 6.3 建立SAR ADC的仿真模型

-

未学习 6.4 如何计算RC滤波器的值

未学习 6.4 如何计算RC滤波器的值

-

未学习 6.5 最终的仿真验证

未学习 6.5 最终的仿真验证

-

未学习 6.6 滤波器RC选型的理论计算方法

未学习 6.6 滤波器RC选型的理论计算方法

-

未学习 6.7 R-C组件选择背后的数学

未学习 6.7 R-C组件选择背后的数学

-

未学习 7.1 电压基准概述

未学习 7.1 电压基准概述

-

未学习 7.2 参考驱动器拓扑概述

未学习 7.2 参考驱动器拓扑概述

-

未学习 7.3 了解SAR参考输入模型

未学习 7.3 了解SAR参考输入模型

-

未学习 7.4 开发SAR输入参考模型

未学习 7.4 开发SAR输入参考模型

-

未学习 7.5 驱动参考实验

未学习 7.5 驱动参考实验

-

未学习 7.6 ADC:SAR 基准输入 - CDAC

未学习 7.6 ADC:SAR 基准输入 - CDAC

-

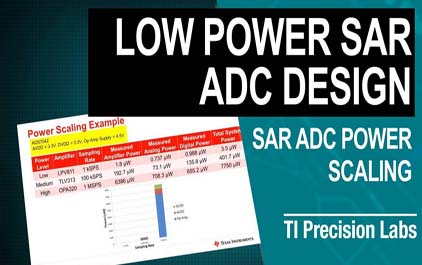

未学习 8.1 SAR ADC功率调节

未学习 8.1 SAR ADC功率调节

-

未学习 8.2 动手实验 - 系统功率调节

未学习 8.2 动手实验 - 系统功率调节

-

未学习 9.1 EOS和ESD

未学习 9.1 EOS和ESD

-

未学习 9.3 向TINA 导入二极管PSpice模型

未学习 9.3 向TINA 导入二极管PSpice模型

-

未学习 9.4 通过高压放大器保护低压ADC

未学习 9.4 通过高压放大器保护低压ADC

-

未学习 9.5 保护低压ADC-改进的解决方案

未学习 9.5 保护低压ADC-改进的解决方案

-

未学习 9.6 用TVS二极管保护ADC

未学习 9.6 用TVS二极管保护ADC

-

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 10.4 带宽与频率 - 子采样概念

未学习 10.4 带宽与频率 - 子采样概念

-

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)11.1 ADC 系统中的噪声

未学习 (中文)11.1 ADC 系统中的噪声

-

未学习 (中文)11.3 ADC 噪声测量、方法和参数

未学习 (中文)11.3 ADC 噪声测量、方法和参数

-

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

-

未学习 (中文)11.9 ADC 系统中的参考噪声简介

未学习 (中文)11.9 ADC 系统中的参考噪声简介

-

未学习 (中文)11.10 参考噪声对信号链性能的影响

未学习 (中文)11.10 参考噪声对信号链性能的影响

-

未学习 (中文)11.11 降低参考噪声

未学习 (中文)11.11 降低参考噪声

-

未学习 动手实验:放大器稳定和电荷桶滤波器设计

未学习 动手实验:放大器稳定和电荷桶滤波器设计

-

未学习 无需放大器即可驱动 SAR ADC

未学习 无需放大器即可驱动 SAR ADC

-

未学习 外部EOS保护装置

未学习 外部EOS保护装置

-

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

-

未学习 (中文)6.7 R-C组件选择背后的数学

未学习 (中文)6.7 R-C组件选择背后的数学

-

未学习 (中文)7.1 电压基准概述

未学习 (中文)7.1 电压基准概述

-

未学习 (中文)7.3 SAR 基准输入 - CDAC

未学习 (中文)7.3 SAR 基准输入 - CDAC

-

未学习 (中文)7.4 了解SAR参考输入模型

未学习 (中文)7.4 了解SAR参考输入模型

-

未学习 (中文)7.5 开发SAR输入参考模型

未学习 (中文)7.5 开发SAR输入参考模型

-

未学习 (中文)7.6 驱动参考实验

未学习 (中文)7.6 驱动参考实验

-

未学习 (中文)8.1 SAR ADC功率调节

未学习 (中文)8.1 SAR ADC功率调节

-

未学习 (中文)8.2 动手实验 - 系统功率调节

未学习 (中文)8.2 动手实验 - 系统功率调节

-

未学习 (中文)9.1 EOS和ESD

未学习 (中文)9.1 EOS和ESD

-

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

-

未学习 (中文)9.4 通过高压放大器保护低压ADC

未学习 (中文)9.4 通过高压放大器保护低压ADC

-

未学习 (中文)9.5 保护低压ADC-改进的解决方案

未学习 (中文)9.5 保护低压ADC-改进的解决方案

-

未学习 (中文)9.6 用TVS二极管保护ADC

未学习 (中文)9.6 用TVS二极管保护ADC

-

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 (中文)10.4 带宽与频率 - 子采样概念

未学习 (中文)10.4 带宽与频率 - 子采样概念

-

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)了解 ADC 系统中的电源噪声

未学习 (中文)了解 ADC 系统中的电源噪声

-

未学习 (中文)时钟噪声如何影响精密 ADC 测量

未学习 (中文)时钟噪声如何影响精密 ADC 测量

-

未学习 (中文)电源噪声降低技术

未学习 (中文)电源噪声降低技术

-

未学习 保护 Delta-Sigma ADC:RTD 概述

未学习 保护 Delta-Sigma ADC:RTD 概述

-

未学习 保护 Delta-Sigma ADC:输入保护电路操作

未学习 保护 Delta-Sigma ADC:输入保护电路操作

-

未学习 保护 Δ-Σ 元件选型

未学习 保护 Δ-Σ 元件选型

-

未学习 利用 TVS 保护 Δ-Σ:性能影响

未学习 利用 TVS 保护 Δ-Σ:性能影响

-

未学习 保护 Δ-Σ ADC:特殊输入范围

未学习 保护 Δ-Σ ADC:特殊输入范围

-

未学习 PCB 布线阻抗匹配

未学习 PCB 布线阻抗匹配

-

未学习 去耦电容

未学习 去耦电容

-

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

-

未学习 电磁兼容测试方法及标准

未学习 电磁兼容测试方法及标准

-

未学习 3线RTD系统的挑战

未学习 3线RTD系统的挑战

-

未学习 设计软件与硬件可配置的多 RTD 测量系统

未学习 设计软件与硬件可配置的多 RTD 测量系统

-

未学习 混叠和抗混叠滤波器

未学习 混叠和抗混叠滤波器