模数转换器 (ADC)

最新课程

- 高级门驱动学习课程

- TAS2020EVM 入门

- F29 实时 MCU

- 如何使用 Edge AI Studio 进行基于雷达的表面分类

- 介绍 1L 调制

- HSS Smart Configurator GUI 概述

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

热门课程

10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

大家好,歡迎收看 TI 精密實驗室,我們將討論

高速類比轉數位轉換器 以及

數位轉類比轉換器裝置的架構。

首先,我們將討論快閃型 類比轉數位轉換器階段的

基本架構,接著說明

如何在更複雜的 類比轉數位轉換器架構中

運用此基本階段作為核心架構,

例如在管線化 類比轉數位轉換器中。

交錯式類比轉數位轉換器 以及

連續漸進式類比轉數位轉換器 也都在討論範圍內。

最後則會說明基本的 數位轉類比轉換器

核心架構。

類比轉數位轉換器 最基本的要素

是追蹤與保持階段, 有時又稱為

取樣與保持,隨後則是 快閃型轉換器階段。

最基本的追蹤與保持階段 包含

由取樣時脈與取樣電容 所控制的開關,

以維持需數位化的數值。

當時脈為低邏輯時, 在取樣時脈期間,

開關會關閉,讓輸入的類比訊號

出現 在取樣電容上。

電容電壓會 在低時脈期間

追蹤輸入訊號,

接著在取樣時脈轉為 高邏輯時,

開關就會開啟。

如此可隔離取樣電容與 輸入類比訊號,

以在開關開啟之際

維持電容的電壓,

所以才會稱之為 追蹤與保持電路。

當取樣電容上的 輸入訊號凍結時,

數位器階段有 半個時脈期間,

可在開關再次關閉 且裝置再度進入追蹤階段前,

將電容電壓轉換為

數位碼。

此圖例所示為 3 位元的快閃型轉換階段。

若要將訊號數位化為 3 位元碼,

將需要 2 的 n 次方減 1 個 電壓比較器

也就是 7 個比較器。

電壓比較器 配置為

一系列的 臨界電壓,

且電壓會轉換為輸入至

各個比較器。

如果類比輸入電壓大於 最低的臨界電壓,

此時比較器輸出就會啟動。

如果電壓大於 第二臨界電壓,

則其比較器就會啟動。

如果電壓大於 第三臨界電壓,

則其比較器就會啟動, 以此類推。

在 7 個比較器之後, 則是

比較器共 7 項的 1 組結果, 通常稱為

溫度計碼。

這是因為隨著輸入電壓升降,

啟動的輸出數量 也會升降,

有如溫度計一樣。

此時,溫度計碼

是以數位方式呈現輸入訊號,

不過較普遍的作法 是利用數位邏輯

將溫度計碼轉換為算術碼。

最後還有一項作業, 就是將算術碼鎖存至

取樣時脈下降沿的暫存器中,

藉此在電容保持的訊號 再次開始變更前,

先行取得樣本。

快閃型轉換器

需要 2 的 n 次方減 1 個 電壓比較器,

就解析度為 5 或 6 位元的 資料轉換器來說

為合理範圍。

6 位元的 類比轉數位轉換器

需要 63 個電壓比較器。

對擴充至 12 或 14 位元的 類比轉數位轉換器而言,

前述概念就不甚實際了。

14 位元的 類比轉數位轉換器會需要

16,535 個電壓比較器。

即使這在晶片上可以實作,

相鄰的臨界電壓之間的 差異

可能會小於比較器的 固有偏移誤差電壓,

導致出現核心線性 或甚至

遺失輸出碼。

如果快閃式 類比轉數位轉換器階段

限制為 5 或 6 位元, 則可在管線階段採用

較高精確度的資料轉換器。

此處圖例為在 3 管線階段 實作

14 位元類比轉數位轉換器。

第一個類比轉數位轉換器 階段為 5 位元快閃階段,

會產生 5 位元的 取樣解析度。

但是當此 5 位元取樣 鎖存時,

5 位元碼就會由配對的 內部 5 位元數位轉類比轉換器

轉換回類比電壓。

此時,實際輸入電壓的

5 位元碼代表

該電壓與對應 5 位元碼的

理想電壓。

實際輸入電壓與 指派至該代碼的

理想電壓之間的差異

稱為實際電壓 與理想電壓之間的

殘值或量化誤差。

如果在 5 位元類比轉數位階段後,

將此殘值乘以 32,

則殘值即會擴大至 類比轉數位轉換器的

原始全幅範圍。

隨後此殘值可進一步由第二個 快閃型類比轉數位轉換器

進行量化, 以獲得更精準的

取樣。

理論上, 這種管線階段的串接

可無限延伸 以獲得無限制的

取樣解析度。

但實際上,不同的 類比轉數位轉換器階段、

DAC 階段與殘值放大器之間的 不匹配與增益,

皆會導致誤差累積,

通常 3 或 4 個管線階段 是可行的方式,

不過須視所有個別元件的

公差修整精度而定。

最後,通常在管線階段中

會設計 1 位元重疊,

讓類比轉數位轉換器階段 與後續 DAC 階段之間的

輕微不匹配情況

不會導致輸出碼 發生跳變,

這類跳變可能大於 最終碼的

一個最低有效位元。

利用算術邏輯可解決 重疊位元的情況,

因為個別階段的各部分

會結合為 一份完整的取樣。

在此例中, 第一個階段

提供 5 位元解析度, 第二個階段則提供

額外的 4 位元解析度,

而最終階段提供 額外的 5 位元解析度,

所以最終取樣為 14 位元。

另一種提高解析度轉換的方式,

則是採用連續漸進式 類比轉數位轉換器。

在此架構中, 類比輸入訊號也會在

取樣與保持電路,或稱 追蹤與保持電路中凍結

如同在快閃式或管線化 類比轉數位轉換器中時使用一樣,

但是在追蹤與保持電路 保持輸入訊號後,

將此電壓轉換為 數位碼的方式

就有所不同。

在此方法中, 類比轉數位轉換器會

反覆地在每次反覆作業中 增加 1 位元,

直到獲得所需的位元數為止。

此處使用單一比較器,但具有 數位轉類比轉換器階段,

以反覆產生連續的

臨界電壓。

第一個臨界電壓通過比較 輸入電壓

高於或是低於中幅,

来判定取樣的最高有效位元。

如果高於中幅, 最高有效位元為一,

且數位轉類比轉換器 會繼續移動至

下一個臨界電壓,

其介於中幅 與全幅兩者中間。

在獲得所需的位元數後,

會將取樣與結束轉換的訊號 一併輸出。

此方法的缺點之一

在於最大轉換率受到

數位轉類比轉換器 與比較器的速度相加之後,

除以必須執行之位元 反覆作業次數

所得的結果限制。

因此,此架構最常

用於速度與功率相對較低, 但是解析度較高的

類比轉數位轉換器。

一般會實作至 16 或 18 位元, 或甚至更高的位元。

若為單一管線化 類比轉數位轉換器,

快閃類比轉數位轉換器階段 達穩定的時間

會大幅限制最大取樣率,

且其輸出 會於半個時脈週期中鎖存。

達到較高取樣率的一種常用方法

是採用多個 類比轉數位轉換器階段並聯,

且時脈延遲並交錯。

如此的好處是 針對特定製程節點,

可達到的取樣率大幅高於 單一類比轉數位轉換器

可達到的取樣率。

缺點則包含需要 將輸入訊號分配至

所有交錯式類比轉數位轉換器,

且沒有偏斜 或振幅不匹配的情況,

且類比輸入訊號 與時脈分配的

負載與分配負擔

亦會提高。

時脈或類比訊號分配 若有不匹配的情況,

會導致取樣資料失真

且失去應有效能。

交錯式類比轉數位轉換器的 常見誤差來源

包含偏移不匹配、振幅不匹配,

以及時脈相位不匹配。

偏移不匹配 與增益不匹配

較易於修正,只要透過於取樣資料流 運算的數位邏輯即可修正,

前述取樣資料流是接續在

交錯式 子類比轉數位轉換器之後。

並且可設計數位邏輯, 以根據

每個交錯式子類比轉數位轉換器的 取樣資料

得出偏移不匹配 和/或增益不匹配的

估計值。

接著可利用算術邏輯,

即時從取樣資料中

扣除估計的偏移誤差。

以此類推, 也可利用乘法邏輯

將估計的增益誤差用於

即時補償取樣資料。

相位誤差補償

較難即時修正。

造成偏移誤差的原因 是因為設計中不同的

交錯式類比轉數位轉換器 核心具有不同的

DC 偏移電壓。

在此例中, 紅色波形

是一個交錯式 類比轉數位轉換器核心產生的波形,

綠色波形則是另一個

交錯式類比轉數位轉換器 產生的波形。

針對未修正的偏移誤差, 誤差的結果

看來會是鋸齒狀,

蓋過理想的取樣模式,

且取樣的值最終 會高於或低於理想值。

就頻域而言 ,這

看起來像在Nyquist 率或双向交錯式采樣率下超過2

產生的FFT頻譜中的突波

或四向交錯式為 取樣率

除以 4 後的倍數。

造成增益誤差的原因 是因為設計中的

交錯式 類比轉數位轉換器核心

有不同的增益值。

在此例中, 紅色波形

是一個交錯式 類比轉數位轉換器核心產生的波形,

綠色波形則是另一個

交錯式類比轉數位轉換器 產生的波形。

未修正增益誤差 也會導致

取樣資料看來為鋸齒狀,

就像偏移誤差一樣, 但是

在跨越中幅時, 誤差的方向

會相反。

在上方範例中, 紅色波形增益降低時,

在高於中幅之處,

取樣低於理想代碼, 低於中幅時

取樣則高於理想代碼。

如此會導致頻譜 比單純偏移誤差的頻譜複雜,

因為會依據

輸入訊號頻率出現

重複影像。

在所示的頻譜圖中, 顯示了輸入訊號的重複影像

以及輸入訊號

第二個諧波的 重複影像。

有數種選項可用於處理 交錯式系統中的

不匹配情況。

若應用要求較高取樣率,

但是較不重視效能,

可能適用仰賴 外部因素匹配的交錯方式,

例如佈線至 類比轉數位轉換器的

訊號佈線長度。

為了在訊噪比方面保有 AC 效能

或諧波效能,

可能需要採行某些 交錯式修正行動。

這通常包含某些

可估計不匹配幅度的方式, 隨後則需

採取修正不匹配的措施。

修正行動可施作於 取樣前的類比訊號,

或以數位方式施作於 轉換後的

取樣資料。

若溫度等環境條件 造成的飄移中

不會考量估計值,

則可在初始期間 執行估計函數,

除非會在特定間隔

執行重新校準。

在類比轉數位轉換器正常運作期間,

可在取樣資料的順滑時段中

持續執行估計函數。

大多數用於估計 增益或偏移不匹配的

估計演算法具有一項缺點,

就是採用的估計演算法 可能

有執行不當的

異常輸入模式。

數位轉類比轉換器的 轉換並非只是

與類比轉數位轉換器 相反而已。

數位轉類比轉換器 最簡單的架構為

電流引導電路。

數位轉類比轉換器 設計為可將

特定電流量移入或移出負載。

根據歐姆定律,此電流與 輸出電壓相關。

在此例中,如果 數位轉類比轉換器的

全幅輸出為 30 毫安輸入 50 歐姆的負載,

那麼上方範例中的 全幅輸入電壓

在單端下為 1.5 伏特,

或在峰間差分下為 3.0 伏特。

電流引導式 數位轉類比轉換器

可為電流汲極 或電流源極類型。

差異在於 數位轉類比轉換器的電流來源

是來自 DAC 電源 並經由負載電阻至接地,

或是來自外部上拉電源

並經由負載電阻, 然後

再經由數位轉類比 轉換器後汲入至接地。

電流源極式 數位轉類比轉換器

一般設計為具備 適用於電流源極的

P 通道裝置, 而電流同步式

數位轉類比轉換器 一般則設計為具備

N 通道電晶體。

無論為哪一種, 輸出電壓

皆根據歐姆定律 由流經負載電阻的

電流量決定。

無論為電流源極 或電流同步式,

都可將數位轉類比轉換器 輸出階段實作為

並聯結合 電流式驅動器,

且每個驅動器的電流能力

為根據相鄰驅動器 電流能力的 2 倍

進行調整。

在這個簡單的 3 位元範例中,

最高有效位元的驅動器 電流能力為

500 微安培, 下一個位元的能力

為 250 微安培, 最低有效位元則為

125 微安培。

全幅輸出為三個驅動器 皆啟用

達到正負 875 微伏特的 電流。

此方法的優點在於

針對 N 位元的解析度, 僅需設計

N 個輸出驅動器 並聯輸出。

缺點則是 若位元數較多,

就難以使輸出驅動器 達到匹配,

因為最高有效位元的公差

可能超過 最低有效位元所需的

解析度。

除非從最高有效位元 到最低有效位元的

公差能適當維持為相差 2 倍,

否則數位轉類比轉換器的

線性就會發生問題。

另一種數位轉類比轉換器 電流輸出的方式,

則是使輸出驅動器的 電流能力匹配。

這種方法 較易於保持

輸出驅動器的公差,

讓驅動器與下個驅動器間 達到良好的匹配,

但是這麼一來,針對 N 位元 解析度就需要

2 的 N 次方減 1 個輸出驅動器。

此處所示範例的 3 位元數位轉類比轉換器

需要 7 個 電流能力相同的

輸出驅動器。

全幅輸出需要所有驅動器

並聯啟用。

在此例中, 輸入取樣碼

會從算術碼 轉換為

溫度計碼,且每位元的 溫度計碼

皆控制個別的 輸出驅動器。

此結構中的 輸出驅動器之間

可達到較佳的匹配, 但對於高解析度取樣而言,

需實作的驅動器數量 就變得十分龐大。

14 位元的數位轉類比轉換器 會需要 16,535 個輸出驅動器

並聯。

若要讓數位轉類比 轉換器的解析度更高,

可結合採用二進制 數位轉類比轉換器

以及溫度計碼式 數位轉類比轉換器。

在本例中,6 位元 數位轉類比轉換器

可使用上方 3 個取樣位元

控制溫度計碼式 數位轉類比轉換器,

因此只需要並聯 7 個匹配的 電流驅動器。

接著下方 3 位元 可用於

控制另外 3 個電流驅動器 ,且其大小

為相鄰的 2 倍。

如此一來, 電流調整的匹配

只需要在 2 的 4 次方內。

較高解析度的 類比轉數位轉換器,

例如 14 或 16 位元, 較可能利用

這種混合編碼形式 實作。

例如若為 16 位元 數位轉類比轉換器,

上方 6 個取樣位元

可轉換為 63 位元溫度計碼,

驅動 63 個匹配的 電流源極。

同時, 較低的 10 個取樣位元

則直接用於驅動 10 個經調整的電流源極,

且其也與 63 個匹配 電流源極並聯。

因此,電流驅動器的總數為 73 個,

而經調整的二進制 電流驅動器匹配

必須在 2 的 11 次方中 達到良好匹配。

也就是 10 個二進制驅動器 調整為在 2 的 10 次方內,

而溫度計碼式驅動器

則皆為經調整之最大驅動器的

2 倍。

本影片內容至此結束。

謝謝收看。

-

未学习 1.1 数据转换器介绍 - 直流参数

未学习 1.1 数据转换器介绍 - 直流参数

-

未学习 1.2 数据转换器介绍 - 交流和直流参数

未学习 1.2 数据转换器介绍 - 交流和直流参数

-

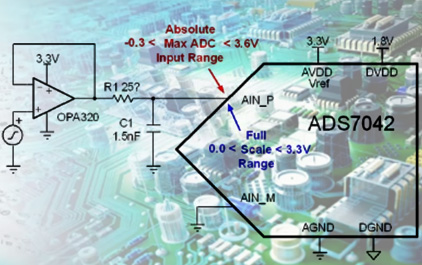

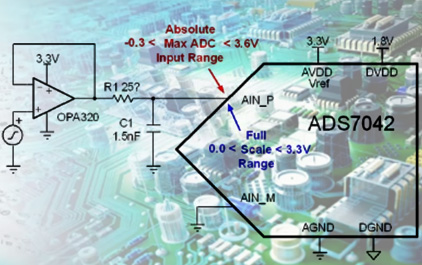

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

未学习 2.1 数据转换器介绍 - SAR型ADC输入类型

-

未学习 2.2.1 单端驱动电路分析

未学习 2.2.1 单端驱动电路分析

-

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

未学习 2.2.2 反向配置与轨对轨放大器的交越失真

-

未学习 2.3.1 交越失真实验所需硬件软件

未学习 2.3.1 交越失真实验所需硬件软件

-

未学习 2.3.2 交越失真实验软件设置

未学习 2.3.2 交越失真实验软件设置

-

未学习 2.3.3 交越失真实验结果

未学习 2.3.3 交越失真实验结果

-

未学习 2.4.1 仪表放大器输入范围计算

未学习 2.4.1 仪表放大器输入范围计算

-

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

未学习 2.4.2 使用软件验证仪表放大器输入共模范围

-

未学习 2.5.1 全差分放大器及失真

未学习 2.5.1 全差分放大器及失真

-

未学习 2.5.2 全差分驱动电路设计

未学习 2.5.2 全差分驱动电路设计

-

未学习 3.1 误差分析背后的统计学知识

未学习 3.1 误差分析背后的统计学知识

-

未学习 3.2 理解与校准ADC系统的偏移和增益误差

未学习 3.2 理解与校准ADC系统的偏移和增益误差

-

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

未学习 3.3 使用蒙特卡罗SPICE工具进行误差统计分析

-

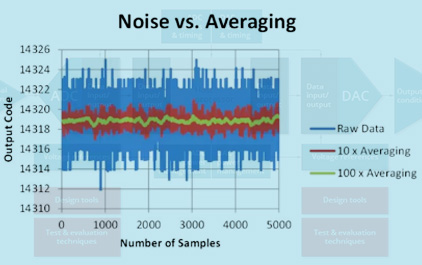

未学习 4.1 计算ADC系统的总噪声

未学习 4.1 计算ADC系统的总噪声

-

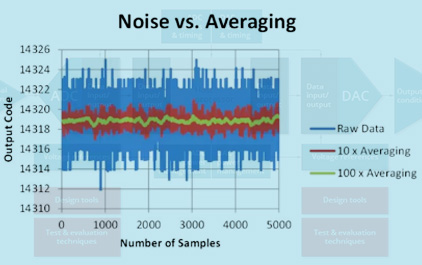

未学习 4.2 动手实验-ADC噪声

未学习 4.2 动手实验-ADC噪声

-

未学习 4.3 ADC 系统中的噪声

未学习 4.3 ADC 系统中的噪声

-

未学习 4.4 ADC 噪声测量、方法和参数

未学习 4.4 ADC 噪声测量、方法和参数

-

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

未学习 4.5 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 4.6 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 4.7 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

未学习 4.8 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

未学习 4.9 计算放大器 + ADC 总噪声:设计示例

-

未学习 4.10 ADC 系统中的参考噪声简介

未学习 4.10 ADC 系统中的参考噪声简介

-

未学习 4.11 参考噪声对信号链性能的影响

未学习 4.11 参考噪声对信号链性能的影响

-

未学习 4.12 降低参考噪声

未学习 4.12 降低参考噪声

-

未学习 5.1 频域介绍

未学习 5.1 频域介绍

-

未学习 5.2 快速傅立叶变换及加窗函数

未学习 5.2 快速傅立叶变换及加窗函数

-

未学习 5.3 改善频率指标的方法:相干采样及滤波

未学习 5.3 改善频率指标的方法:相干采样及滤波

-

未学习 5.4 混叠及抗混叠滤波器

未学习 5.4 混叠及抗混叠滤波器

-

未学习 5.5 实验 - 混叠和抗混叠滤波器

未学习 5.5 实验 - 混叠和抗混叠滤波器

-

未学习 6.1 SAR ADC及其器件选型

未学习 6.1 SAR ADC及其器件选型

-

未学习 6.2 驱动放大器的选型和验证

未学习 6.2 驱动放大器的选型和验证

-

未学习 6.3 建立SAR ADC的仿真模型

未学习 6.3 建立SAR ADC的仿真模型

-

未学习 6.4 如何计算RC滤波器的值

未学习 6.4 如何计算RC滤波器的值

-

未学习 6.5 最终的仿真验证

未学习 6.5 最终的仿真验证

-

未学习 6.6 滤波器RC选型的理论计算方法

未学习 6.6 滤波器RC选型的理论计算方法

-

未学习 6.7 R-C组件选择背后的数学

未学习 6.7 R-C组件选择背后的数学

-

未学习 7.1 电压基准概述

未学习 7.1 电压基准概述

-

未学习 7.2 参考驱动器拓扑概述

未学习 7.2 参考驱动器拓扑概述

-

未学习 7.3 了解SAR参考输入模型

未学习 7.3 了解SAR参考输入模型

-

未学习 7.4 开发SAR输入参考模型

未学习 7.4 开发SAR输入参考模型

-

未学习 7.5 驱动参考实验

未学习 7.5 驱动参考实验

-

未学习 7.6 ADC:SAR 基准输入 - CDAC

未学习 7.6 ADC:SAR 基准输入 - CDAC

-

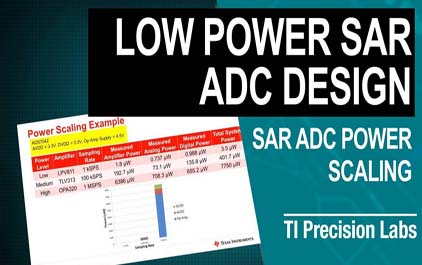

未学习 8.1 SAR ADC功率调节

未学习 8.1 SAR ADC功率调节

-

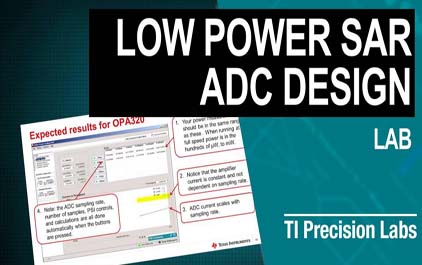

未学习 8.2 动手实验 - 系统功率调节

未学习 8.2 动手实验 - 系统功率调节

-

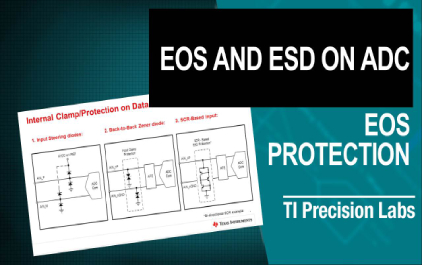

未学习 9.1 EOS和ESD

未学习 9.1 EOS和ESD

-

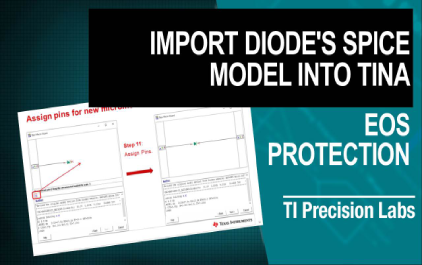

未学习 9.3 向TINA 导入二极管PSpice模型

未学习 9.3 向TINA 导入二极管PSpice模型

-

未学习 9.4 通过高压放大器保护低压ADC

未学习 9.4 通过高压放大器保护低压ADC

-

未学习 9.5 保护低压ADC-改进的解决方案

未学习 9.5 保护低压ADC-改进的解决方案

-

未学习 9.6 用TVS二极管保护ADC

未学习 9.6 用TVS二极管保护ADC

-

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

未学习 9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 10.3了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 10.4 带宽与频率 - 子采样概念

未学习 10.4 带宽与频率 - 子采样概念

-

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)11.1 ADC 系统中的噪声

未学习 (中文)11.1 ADC 系统中的噪声

-

未学习 (中文)11.3 ADC 噪声测量、方法和参数

未学习 (中文)11.3 ADC 噪声测量、方法和参数

-

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

未学习 (中文)11.4 低速 Δ-Σ ADC 的系统噪声性能

-

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

未学习 (中文)11.5 分析和计算 ADC 系统中的噪声带宽——多级滤波器

-

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

未学习 (中文)11.6 分析和计算 ADC 系统中的噪声带宽——数字滤波器

-

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

未学习 (中文)11.7 增益对噪声、ADC FSR 和动态范围的影响

-

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

未学习 (中文)11.8 计算放大器 + ADC 总噪声:设计示例

-

未学习 (中文)11.9 ADC 系统中的参考噪声简介

未学习 (中文)11.9 ADC 系统中的参考噪声简介

-

未学习 (中文)11.10 参考噪声对信号链性能的影响

未学习 (中文)11.10 参考噪声对信号链性能的影响

-

未学习 (中文)11.11 降低参考噪声

未学习 (中文)11.11 降低参考噪声

-

未学习 动手实验:放大器稳定和电荷桶滤波器设计

未学习 动手实验:放大器稳定和电荷桶滤波器设计

-

未学习 无需放大器即可驱动 SAR ADC

未学习 无需放大器即可驱动 SAR ADC

-

未学习 外部EOS保护装置

未学习 外部EOS保护装置

-

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

未学习 (中文)5.5 实验 - 混叠和抗混叠滤波器

-

未学习 (中文)6.7 R-C组件选择背后的数学

未学习 (中文)6.7 R-C组件选择背后的数学

-

未学习 (中文)7.1 电压基准概述

未学习 (中文)7.1 电压基准概述

-

未学习 (中文)7.3 SAR 基准输入 - CDAC

未学习 (中文)7.3 SAR 基准输入 - CDAC

-

未学习 (中文)7.4 了解SAR参考输入模型

未学习 (中文)7.4 了解SAR参考输入模型

-

未学习 (中文)7.5 开发SAR输入参考模型

未学习 (中文)7.5 开发SAR输入参考模型

-

未学习 (中文)7.6 驱动参考实验

未学习 (中文)7.6 驱动参考实验

-

未学习 (中文)8.1 SAR ADC功率调节

未学习 (中文)8.1 SAR ADC功率调节

-

未学习 (中文)8.2 动手实验 - 系统功率调节

未学习 (中文)8.2 动手实验 - 系统功率调节

-

未学习 (中文)9.1 EOS和ESD

未学习 (中文)9.1 EOS和ESD

-

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

未学习 (中文)9.3 向TINA 导入二极管PSpice模型

-

未学习 (中文)9.4 通过高压放大器保护低压ADC

未学习 (中文)9.4 通过高压放大器保护低压ADC

-

未学习 (中文)9.5 保护低压ADC-改进的解决方案

未学习 (中文)9.5 保护低压ADC-改进的解决方案

-

未学习 (中文)9.6 用TVS二极管保护ADC

未学习 (中文)9.6 用TVS二极管保护ADC

-

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

未学习 (中文)9.7 用TVS二极管保护ADC –改进的解决方案

-

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

未学习 (中文)10.1 了解和比较高速模数(ADC)和数模转换器(DAC)转换器架构

-

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

未学习 (中文)10.2 抖动对高速模数转换器(ADC)信噪比(SNR)的影响

-

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

未学习 (中文)10.3 了解高速数据转换器中的信噪比(SNR)和噪声频谱密度(NSD)

-

未学习 (中文)10.4 带宽与频率 - 子采样概念

未学习 (中文)10.4 带宽与频率 - 子采样概念

-

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

未学习 (中文)10.5 高速数据转换器中的采样率与数据速率,抽取(DDC)和插值(DUC)概念

-

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

未学习 (中文)10.6 频率和采样率规划:了解高速ADC中的采样,奈奎斯特区,谐波和杂散性能

-

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

未学习 (中文)10.7 高速数据转换器信号处理:真实和复杂的调制

-

未学习 (中文)了解 ADC 系统中的电源噪声

未学习 (中文)了解 ADC 系统中的电源噪声

-

未学习 (中文)时钟噪声如何影响精密 ADC 测量

未学习 (中文)时钟噪声如何影响精密 ADC 测量

-

未学习 (中文)电源噪声降低技术

未学习 (中文)电源噪声降低技术

-

未学习 保护 Delta-Sigma ADC:RTD 概述

未学习 保护 Delta-Sigma ADC:RTD 概述

-

未学习 保护 Delta-Sigma ADC:输入保护电路操作

未学习 保护 Delta-Sigma ADC:输入保护电路操作

-

未学习 保护 Δ-Σ 元件选型

未学习 保护 Δ-Σ 元件选型

-

未学习 利用 TVS 保护 Δ-Σ:性能影响

未学习 利用 TVS 保护 Δ-Σ:性能影响

-

未学习 保护 Δ-Σ ADC:特殊输入范围

未学习 保护 Δ-Σ ADC:特殊输入范围

-

未学习 PCB 布线阻抗匹配

未学习 PCB 布线阻抗匹配

-

未学习 去耦电容

未学习 去耦电容

-

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

未学习 SAR 和 Δ-Σ:噪声和驱动注意事项

-

未学习 电磁兼容测试方法及标准

未学习 电磁兼容测试方法及标准

-

未学习 3线RTD系统的挑战

未学习 3线RTD系统的挑战

-

未学习 设计软件与硬件可配置的多 RTD 测量系统

未学习 设计软件与硬件可配置的多 RTD 测量系统

-

未学习 混叠和抗混叠滤波器

未学习 混叠和抗混叠滤波器