通用运算放大器

最新课程

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

- 重新构想人工智能数据中心电源:从电网到终端的全链路方案

- 如何将 PurePath Console (PPC3) 用于 TI 音频转换器

- 为人形机器人提供安全高效运行的动力保障

- 《使用 C2000 IDE-Assist 从 F28x 迁移到 F29x》视频

热门课程

11.1 TI 高精度实验室 - 静电释放 (ESD)

大家好

欢迎来到 TI Precision Labs

德州仪器高精度实验室

本次课程我们将讨论

Electrostatic Discharge

静电释放的话题

本节课程将介绍

ESD 是如何损坏半导体元器件的

并且详细介绍半导体器件中的

ESD 保护电路的设计

最后我们将介绍

ESD 性能指标是如何测定的

以帮助更好的理解器件的 ESD 性能

很多常见的物体会积累静电

特别是绝缘体

很容易积累大量的静电

一些物体倾向于带正电

另外一些物体则倾向于带负电

当两个电荷不同的物体

靠到一起的时候

两个物体之间

会产生一个瞬时电流

称为 ESD 静电释放

ESD 电压经常能达到几千伏

产生可见的电火花

对于半导体器件来说

ESD 是最常见的损坏原因

上面的这个表格罗列了一些

生活中常见动作所产生的静电电压

注意到静电电压和相对湿度有关

相对湿度较低的时候

产生的静电电压更高

下面的表格展示了

人体对静电放电的感受程度

注意到当您看到电火花的时候

静电电压已经非常高了

在 8000V 以上

不同类型的器件

对 ESD 的耐受值也不一样

一些器件比如 MOS 管

在很低的电压时就会损坏

后面我们将会看到

而大部分的芯片中

采用的 ESD 保护电路

能够提升器件的 ESD 性能

在增加了 ESD 保护电路以后

MOS 器件的 ESD 耐压值

可以从 10V 提升到几千伏

我们来详细地观察一下

ESD 是怎样损坏半导体器件的

假如当一个幅值很高的静电

或者电压加到运放的反相端

和负电源端

这就会在输入 MOS 管的栅极

和源极之间产生一个很高的电压

这个电压会击穿栅氧化层损坏器件

值得注意的是

MOS 管栅极氧化层的厚度

通常只有几个纳米

在这种电压下非常容易被损坏

针对 ESD 事件

有两种主要的分类方法

在电路组装前

即芯片未焊接到 PCB 上之前

ESD 会造成器件损坏

这可能发生在生产

工厂测试和组装的过程中

一般来说

工厂测试和生产工艺在设计的时候

就考虑到最小化 ESD 事件的发生

电路组装后的 ESD 指的是

在一个组装好的 pcb

或者终端产品上发生的 ESD 事件

这种情况下产品的包装设计

以及器件本身的抗 ESD 性能

决定了产品的 ESD 特性

器件内部的 ESD 保护电路

是为了防止器件在电路组装前的

ESD 事件中损坏

我们可以采取一些基本的预防措施

来最小化 ESD 对器件和产品的损坏

一般来说

这些预防措施采用电阻性材料

来释放静电

比如图中所示的抗静电手环

能够让人体上的静电

可控地释放到大地上

这些抗静电材料的阻值

一般在兆欧的级别

值得注意的是

图中所示的抗静电包装

抗静电盒以及抗静电工作平台

同样都包含了电阻性材料

它能够缓慢地释放静电

在半导体器件最初的生产过程中

芯片的 ESD 防护性能参数就已经确定了

首先大量的芯片样片经过自动化测试

一般来说

芯片数据手册上的大部分参数

都是在这个自动化测试中测量出来的

然后一个专门的 ESD 测试系统

对器件进行 ESD 脉冲仿真测试

这个 ESD 脉冲的参数

是由测试硬件控制的

比如我们可以选择脉冲的幅度

和 ESD 模型

我们将在后文中

讨论多种不同的 ESD 模型

简单来说

ESD 模型通过设置电容电感

和 ESD 电流等参数

来模拟现实中的 ESD 现象

在测试过程中

ESD 脉冲加到芯片的多个引脚

和引脚的不同组合上

同样的

我们采用不同级别的 ESD 脉冲

对芯片进行测试

比如 1000 伏 2000 伏 3000 伏等

最后根据这个复杂的 ESD 测试流程

对芯片进行反复的测试

芯片的 ESD 等级

是由这一批样片均能通过测试的

最高值决定的

这个数值

就是芯片数据手册上的 ESD 绝对最高值

我们采用三种不同的模型

来产生 ESD 脉冲

人体模型是 ESD 测试中最常用的模型

这个模型是用来模拟

当人体碰触到芯片时产生的 ESD

典型的人体模型电压值范围

从 1000 伏到 5000 伏

机器模型也被称作零欧姆模型

因为它是用来仿真

一个阻抗非常低的 ESD 到地的释放情形

机器模型是用来仿真金属壁

或自动化组装设备的 ESD 事件

在大部分情况下

机器模型都被带电器件模型所替代

带电器件模型

用来精确仿真测试环境

和组装环境中的 ESD 事件

比如当器件从传送管道上滑下时

会产生静电累积

带电模型的典型电压值

从几百伏到几千伏

带电器件模型的电流

比人体模型的电流要高很多

因为带电器件模型的限流电阻很小

在这部分我们介绍一下芯片内部

常用的 ESD 保护设计

在这里我们采用运放作为示例

其他器件中采用的 ESD 保护也是类似的

注意一下

这里的 ESD 保护是用来保护器件

还未组装到电路中的 ESD 事件

也就是说这些结构

是用来防护器件

在测试组装和加工过程中的 ESD 现象

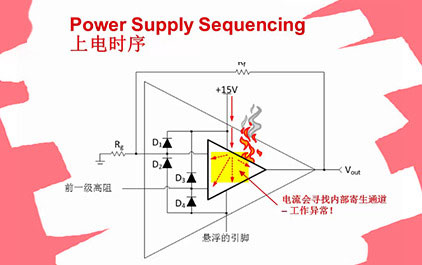

在未上电的系统中

这些 ESD 保护同样有效

但是在上电系统中

它们也可能造成栓锁效应

这一点我们将在

有关芯片过压的视频课程中做详细介绍

芯片内部中一般有三种

ESD 保护结构

分别是串联电阻

导流二极管和吸收器件

导流二极管引导 ESD 脉冲电流

到吸收器件上

避免损坏其他电路

吸收器件能够吸收 ESD 脉冲能量

限制电压值来保护电路

串联电阻限制了输入和输出的电流

是值得注意的是

大的串联电阻能够提供更好的保护

但是也会使芯片的噪声

或者最大输出电流等等指标变差

因为有这些限制

串联电阻会影响到某些器件上的 ESD 性能

我们来测试一下 ESD 保护

是怎样工作的

在这个示例中

一个 ESD 脉冲加到运放芯片的

同相输入端引脚和负电压引脚之间

比如在一个没有静电保护的

工作台上组装 PCB

就可能产生这种情况

注意一下

在这个例子中

D3 二极管变成正向偏置

引导 ESD 脉冲到吸收器件上

吸收器件是用来限制电压值

吸收 ESD 脉冲的能量的

如果 ESD 脉冲加到不同的芯片引脚上

不同的二极管会导通

并引导 ESD 脉冲

到吸收器件上

同样的输入电阻 R2

限制了 ESD 脉冲的输入电流

大阻值 R2 会让芯片的 ESD 性能更好

但是会因为偏置电流的影响而引入误差

还会影响噪声性能和芯片的频率响应

这些参数让我们对 ESD 二级管的性能

有一个基本的了解

实际情况下

二极管性能由设计和工艺来决定

很重要的一点是

二极管导通压降为 0.7 伏时

导通电流很大

对应于 ESD 脉冲的情形

这种二极管能够保护芯片

免受几纳秒的安培级别的

脉冲电流的损害

但如果是持续的电流

则只有约 10mA

这些二极管还会引入反方向的漏电流

在室温下漏电流只有几纳安或者更小

但在高温时漏电流可以达到几百纳安

实际上 CMOS 器件的输入偏置电流

大部分都是由 ESD 二极管的漏电流造成的

最后大家还需要记住

ESD 二极管还会引入几皮法的寄生电容

在这里我们来看一下

两种运放芯片中 ESD 二极管的 IV 曲线

可以看到

低电流时二极管的正向压降约为 0.7V

大电流时导通压降增加到了 1V

理解 ESD 二极管特性

可以帮助更好的理解

后续课程中的电气过压问题

在前面的章节中

我们粗略的讨论了下吸收器件

这里的吸收器件

是一个由衬底引入的寄生三极管

在正常情况下这个三极管是反偏的

所以不会有衬底电流

当加到三极管上的电压升高

接近集电极发射极的击穿区时

加大处于击穿区的三极管上的电压

电流会急剧增大

集电极的电流会增加

直到进入一个称为 snap back

回跳点的区域

在超过这个区域之后

电流会持续快速地增加

如果在三极管的电流通路上

没有一个电阻来限制电流

电流过大会造成芯片过热

直到三极管烧坏

这时候通常情况下

发射极电流会停止升高

并和集电极之间形成一个永久的短路

吸收器件是用来钳制供电电压

避免芯片在未安装到电路

之前损坏而设计的

当 ESD 结束后

因为没有电压加到器件上

一般几个纳秒以后吸收器件就会关闭

另一方面

如果芯片被安装到电路中以后

发生 ESD 事件吸收器件会持续开通

并保持一个低阻的状态

直到电源电压关掉

因此在芯片过压时

不能让吸收装置开启

这个话题我们将在后面的课程中

进一步的探讨

芯片数据手册中的最大额定值

是指在最坏的情况下

不让芯片损坏的数值

表格中给出了最大供电电压

输入电压输入电流温度等等指标

注意到

最大输入电流是正负 10mA

对于大多数器件来说

这都是一个极限值

这个值是根据 ESD 二级管

所能承受的最大持续电流值得来的

同样表格中也给出了

芯片的 ESD 指标

在这个例子中

ESD 人体模型的额定值是 4000 伏

带电器件模型是 1000 伏

不同的器件根据测试结果

ESD 性能指标会略有不同

以上就是本次视频的内容

谢谢您的观看

请准备好下面的一个小测试

看看您是否已经掌握了本次课程的内容

-

未学习 1.1 TI 高精度实验室 - 介绍

未学习 1.1 TI 高精度实验室 - 介绍

-

未学习 1.2 TI 高精度实验室 - 国家仪器虚拟测试仪概述

未学习 1.2 TI 高精度实验室 - 国家仪器虚拟测试仪概述

-

未学习 2.1 TI 高精度实验室 - 输入失调电压与输入偏置电流

未学习 2.1 TI 高精度实验室 - 输入失调电压与输入偏置电流

-

未学习 2.2 TI 高精度实验室 - 输入失调电压与输入偏置电流 实验

未学习 2.2 TI 高精度实验室 - 输入失调电压与输入偏置电流 实验

-

未学习 3.1 TI 高精度实验室 - 输入输出限制

未学习 3.1 TI 高精度实验室 - 输入输出限制

-

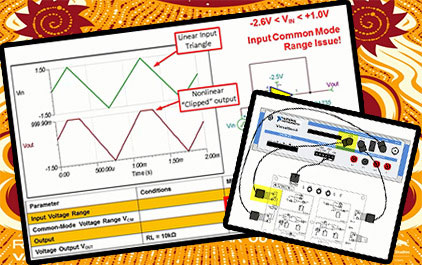

未学习 3.2 输入和输出限制 2

未学习 3.2 输入和输出限制 2

-

未学习 3.3 输入和输出限制 3

未学习 3.3 输入和输出限制 3

-

未学习 3.4 TI 高精度实验室 - 输入输出限制 实验

未学习 3.4 TI 高精度实验室 - 输入输出限制 实验

-

未学习 4.1 功率与温度

未学习 4.1 功率与温度

-

未学习 5.1 TI 高精度实验室 - 带宽 1

未学习 5.1 TI 高精度实验室 - 带宽 1

-

未学习 5.2 TI 高精度实验室 - 带宽 2

未学习 5.2 TI 高精度实验室 - 带宽 2

-

未学习 5.3 TI 高精度实验室 - 带宽 3

未学习 5.3 TI 高精度实验室 - 带宽 3

-

未学习 5.4 TI 高精度实验室 - 带宽 4

未学习 5.4 TI 高精度实验室 - 带宽 4

-

未学习 5.5 TI 高精度实验室 - 带宽 实验

未学习 5.5 TI 高精度实验室 - 带宽 实验

-

未学习 6.1 TI 高精度实验室 - 压摆率 1

未学习 6.1 TI 高精度实验室 - 压摆率 1

-

未学习 6.2 TI 高精度实验室 - 压摆率 2

未学习 6.2 TI 高精度实验室 - 压摆率 2

-

未学习 6.3 TI 高精度实验室 - 压摆率 3

未学习 6.3 TI 高精度实验室 - 压摆率 3

-

未学习 6.4 TI 高精度实验室 - 压摆率 实验

未学习 6.4 TI 高精度实验室 - 压摆率 实验

-

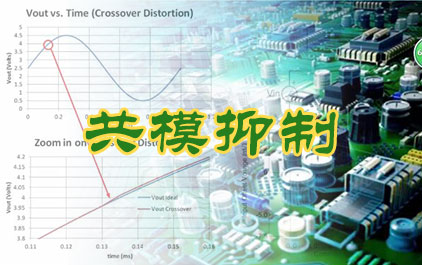

未学习 7.1 共模抑制

未学习 7.1 共模抑制

-

未学习 7.2 电源抑制

未学习 7.2 电源抑制

-

未学习 8.1 TI 高精度实验室 - 噪声 1

未学习 8.1 TI 高精度实验室 - 噪声 1

-

未学习 8.2 TI 高精度实验室 - 噪声 2

未学习 8.2 TI 高精度实验室 - 噪声 2

-

未学习 8.3 TI 高精度实验室 - 噪声 3

未学习 8.3 TI 高精度实验室 - 噪声 3

-

未学习 8.4 TI 高精度实验室 - 噪声 4

未学习 8.4 TI 高精度实验室 - 噪声 4

-

未学习 8.5 TI 高精度实验室 - 噪声 5

未学习 8.5 TI 高精度实验室 - 噪声 5

-

未学习 8.6 TI 高精度实验室 - 噪声 6

未学习 8.6 TI 高精度实验室 - 噪声 6

-

未学习 8.7 TI 高精度实验室 - 噪声 7

未学习 8.7 TI 高精度实验室 - 噪声 7

-

未学习 8.8 TI 高精度实验室 - 噪声 8

未学习 8.8 TI 高精度实验室 - 噪声 8

-

未学习 8.9 TI 高精度实验室 - 噪声 实验

未学习 8.9 TI 高精度实验室 - 噪声 实验

-

未学习 9.1 低失真运算放大器的设计-1

未学习 9.1 低失真运算放大器的设计-1

-

未学习 9.2 低失真运算放大器的设计-2

未学习 9.2 低失真运算放大器的设计-2

-

未学习 9.3 低失真运算放大器的设计-3

未学习 9.3 低失真运算放大器的设计-3

-

未学习 9.4 低失真运算放大器的设计-4

未学习 9.4 低失真运算放大器的设计-4

-

未学习 10.1 TI 高精度实验室 - 运算放大器:稳定性分析 1

未学习 10.1 TI 高精度实验室 - 运算放大器:稳定性分析 1

-

未学习 10.2 TI 高精度实验室 - 运算放大器:稳定性分析 2

未学习 10.2 TI 高精度实验室 - 运算放大器:稳定性分析 2

-

未学习 10.3 TI 高精度实验室 - 运算放大器:稳定性分析 3

未学习 10.3 TI 高精度实验室 - 运算放大器:稳定性分析 3

-

未学习 10.4 TI 高精度实验室 - 运算放大器:稳定性分析 4

未学习 10.4 TI 高精度实验室 - 运算放大器:稳定性分析 4

-

未学习 10.5 TI 高精度实验室 - 运算放大器:稳定性分析 5

未学习 10.5 TI 高精度实验室 - 运算放大器:稳定性分析 5

-

未学习 10.6 TI 高精度实验室 - 运算放大器:稳定性分析 6

未学习 10.6 TI 高精度实验室 - 运算放大器:稳定性分析 6

-

未学习 10.7 TI 高精度实验室 - 运算放大器:稳定性 - 实验

未学习 10.7 TI 高精度实验室 - 运算放大器:稳定性 - 实验

-

未学习 11.1 TI 高精度实验室 - 静电释放 (ESD)

未学习 11.1 TI 高精度实验室 - 静电释放 (ESD)

-

未学习 12.1 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 1

未学习 12.1 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 1

-

未学习 12.2 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 2

未学习 12.2 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 2

-

未学习 12.3 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 3

未学习 12.3 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 3

-

未学习 12.4 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 4

未学习 12.4 TI 高精度实验室 - 运算放大器:电气过应力 (EOS) 4

-

未学习 13.1 电流反馈型运算放大器

未学习 13.1 电流反馈型运算放大器

-

未学习 13.2 电流反馈运放

未学习 13.2 电流反馈运放

-

未学习 14.1 如何分析合成器相位噪声

未学习 14.1 如何分析合成器相位噪声

-

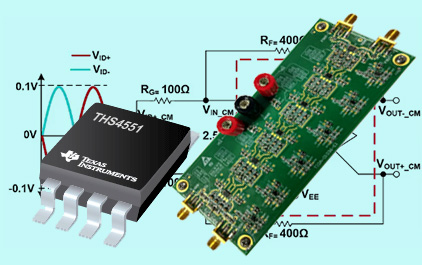

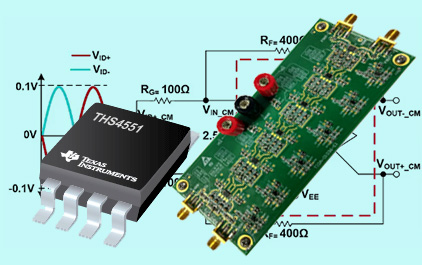

未学习 15.1 全差分放大器 — 差分信号和FDA的介绍

未学习 15.1 全差分放大器 — 差分信号和FDA的介绍

-

未学习 15.2 全差分放大器 — FDA的输入输出和共模

未学习 15.2 全差分放大器 — FDA的输入输出和共模

-

未学习 15.3 全差分放大器 — FDA的稳定性和相位裕量

未学习 15.3 全差分放大器 — FDA的稳定性和相位裕量

-

未学习 15.4 全差分放大器 — FDA的噪声和噪声控制

未学习 15.4 全差分放大器 — FDA的噪声和噪声控制

-

未学习 15.5 全差分放大器 — 设计用于驱动差分输入ADC的前端电路

未学习 15.5 全差分放大器 — 设计用于驱动差分输入ADC的前端电路

-

未学习 (中文)3.2 输入和输出限制 2

未学习 (中文)3.2 输入和输出限制 2

-

未学习 (中文)14.3 电流反馈型运算放大器 Spice 仿真

未学习 (中文)14.3 电流反馈型运算放大器 Spice 仿真

-

未学习 (中文)15.5 设计用于驱动差分输入ADC的前端电路

未学习 (中文)15.5 设计用于驱动差分输入ADC的前端电路

-

未学习 运算放大器失真:简介

未学习 运算放大器失真:简介

-

未学习 (中文)反相输入电容

未学习 (中文)反相输入电容

-

未学习 (中文)断开差分放大器上的环路

未学习 (中文)断开差分放大器上的环路

-

未学习 (中文)带宽 - 波特图截止频率

未学习 (中文)带宽 - 波特图截止频率

-

未学习 (中文)带宽 - 增益和 GBW

未学习 (中文)带宽 - 增益和 GBW

-

未学习 (中文)带宽 - 同相增益和极点

未学习 (中文)带宽 - 同相增益和极点

-

未学习 (中文)带宽 - AOL 增益转换率

未学习 (中文)带宽 - AOL 增益转换率

-

未学习 (中文)带宽 - 实验

未学习 (中文)带宽 - 实验

-

未学习 (中文)转换率介绍

未学习 (中文)转换率介绍

-

未学习 (中文)稳定时间

未学习 (中文)稳定时间

-

未学习 (中文)信号响应

未学习 (中文)信号响应

-

未学习 (中文)运算放大器失真:简介

未学习 (中文)运算放大器失真:简介

-

未学习 (中文)输入级

未学习 (中文)输入级

-

未学习 (中文)光谱密度

未学习 (中文)光谱密度

-

未学习 (中文)计算 RMS 噪声

未学习 (中文)计算 RMS 噪声

-

未学习 (中文)计算总噪声

未学习 (中文)计算总噪声

-

未学习 (中文)简化计算

未学习 (中文)简化计算

-

未学习 (中文)噪声spice模拟

未学习 (中文)噪声spice模拟

-

未学习 (中文)验证噪声模型

未学习 (中文)验证噪声模型

-

未学习 (中文)测量系统噪声

未学习 (中文)测量系统噪声

-

未学习 (中文)1/F 噪声

未学习 (中文)1/F 噪声

-

未学习 (中文)噪声 - 实验

未学习 (中文)噪声 - 实验

-

未学习 理想的无源元件

未学习 理想的无源元件