电机驱动

最新课程

- CCStudio™ Edge AI Studio for Time Series - 概述

- ADS9327系列精密ADC

- TI 增强型 MSPM0C MCU 系列,可简化系统设计

- 高级门驱动学习课程

- TAS2020EVM 入门

- F29 实时 MCU

- 如何使用 Edge AI Studio 进行基于雷达的表面分类

- 介绍 1L 调制

- HSS Smart Configurator GUI 概述

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

热门课程

C2837x入门指南(十三) — DMA模块(下)

假设在这次转换中

Burst size配置成5个word

transfer size 配置称3个 bursts

完成一个transfer

然后配置原地址的起始位ADC

让ADC的结果计算器0xF000

误差为1

transfer的步程为-4

这里配置-4的原因是需要对ADC的结果计算器

进行循环传输

所以在完成一件Burst事件后

指针会指到0xF004的位置

所以此时必须回到0xb00的位置

重新传输 目标地址是GS3的

0XF3000地址

误差是3 因为每个ADC的结果需要放三次

所以为了达到三个数据 一个间隔的目的

这地方设置为3 transfer size设置为-11

这里设置负数的原因和原地址一样

需要回到固定的地址 进行传输

比如一次传输完以后

应该只在CH4这个地方 下一次传输需要回到

0xF000这地方 所以必须把

0xF000减去11 才能回到0xF000的位置

这样配置 才能完成前一页讲的方法

前一页要求的ADC传输的方法

最右边是ADC传输完成的结果图

和前一页所需要的目标达成一致

再举一个ping-pong模式的例子

目标是需要将ADC SOC0里面的数据

采样50次 然后放在0xC140的位置

接着触发DMA中断 重新配置DMA的原地址和目标地址

把ADCLOC1的数据采样50次

存储在紧挨着上一个地址

所以这个例子需要配置ADC 从PWSOC触发

然后burst尺寸为0 即一次burst只传输一个word

transfer的尺寸是0x31 即50个触发事件

采集了50个CDC值

完成50次burst事件 才算完成一次transfer

原地址还是0xB00

原地址的burst步长是0

这里可以不配置

因为反复读取ADCLOC0的结果

寄存器 ADC的result是0

默认值就是0 transfer的步长是0

所以每次在同一个地方 开始新的boost

对于目标地址而言 目标地址的地址指针

应该在0xc140

burst的步长同样是0

每次burst事件都是一个word结束

transfer的步长要设置成1

因为一次burst事件以后 就需要把数据存到

下一个地址中

这样完成一次transfer后

会触发一次中断

中断会重新初始化EMA

就会配置同样完成一次SOC的50次采样结果存储

这样ping pong来回采样 但是

要完成这样的一个DMA设置

就需要设置continue等于1

就是配置为连续传输模式

即每次完成一次transfer以后

都会出发中断

然后重新初始化DMA

就可以

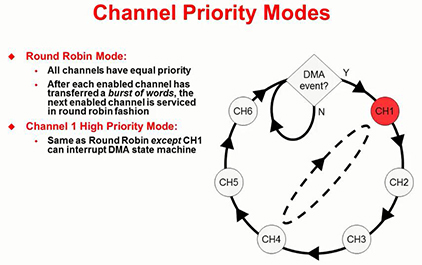

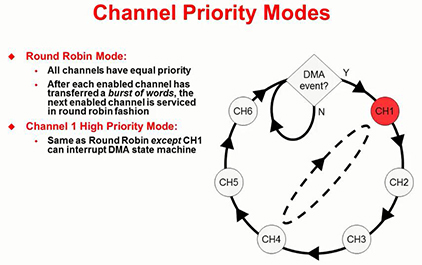

DMA的六个通道优先级等同于ADCLOC run 优先级

通道1可以在特殊设置中拥有high priority模式

可以打断其他通道传输的一个过程

然后完成一次burst后 把权限还给CH4 CH5 CH6

这个框图是CH1如何设置为high priority模式

就可以中断其他通道的burst事件

在这个点 打断其他通道的数据读取传输

但是如果没有设置 CH1的high priority模式

就只能在完成一次transfer之后

才打断其他通道的一个事件

DMA传输一个word需要4个系统时钟

MCBSP例外 需要5个

每次启动一个新的burst事件

会有一个系统时钟延时

如果设置了通道1的优先级模式

会占用一个系统时钟 从通道1的占用中

返回 如果是32位数据传输 那花费的时间比16位少一半

当然MSBSP还是除外 因为它不支持32位的word传输

举个例子 一个128位的word

如果把它分成8个burst传输的话

每个burst传输16个word

就会花费520个系统时钟的时间

但如果把两个16位数据当成一个32位数据传输的话

那同样的传输 少了一半的时间 是264个cycle

DMA和CPU之间 会在一定的情况下 占用相同的地址

如果CPU正在访问 DMA就会等待CPU当前访问结束后

再去访问

并且紧接着读写数据

同时CPU读取数据信息时 也不会和DMA冲突

它们会错开 分别读取原地址和目标地址的数据

下面简单看看DMA的寄存器

主要分成两个部分

一个是所有通道一个同样的寄存器

CTRL寄存器 和优先级寄存器

另外就是每个通道独立拥有的寄存器

所有通道共同拥有的control寄存器

主要是控制DMA的硬件复位

以及DMA状态机的一个复位

优先寄存器就是刚才提到的

可以设置通道1的优先级模式是否使能

对于单独的DMA通道的寄存器

比较重要的是模式寄存器 可以在其中设置

是否使能中断

传输数据是16位还是32位

是否使能重复DMA

传输模式 就是continue mode

以及每次burst之后是否需要出发新的burst事件

还是oneshot模式 以及中断的触发点

是在transfer之前还是结束后

是否触发外设中断

是否使能中断溢出功能

以及外设中断的中断源

和触发源一样后面会有详细的表格介绍

外设触发源寄存器 可以选择每个通道的触发源

最多可以选择256个通道的触发源

如果是两键触发 就可以在每个位上设置0

这页是所有触发源的列表

最后是每个通道的控制寄存器

高8位是状态寄存器 主要是当前DMA通道

是否溢出

是否在运行 是否在burst模式

以及是否已经完成一个transfer事件

以及是否被外设中断触发的一个标志

低8位是控制寄存器

用于清除同步事件 外设中断标志

强制触发一次外设中断事件

软件复位

以及软件挂起和运行功能

-

未学习 C2837x入门指南(一) — 概述

未学习 C2837x入门指南(一) — 概述

-

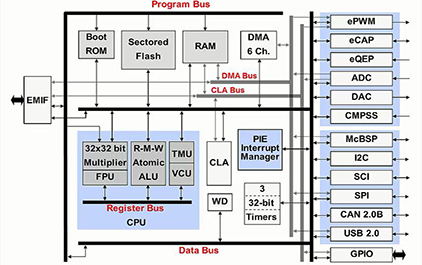

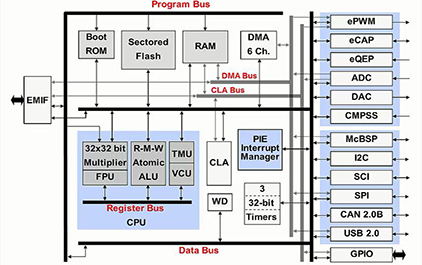

未学习 C2837x入门指南(二) — 芯片架构

未学习 C2837x入门指南(二) — 芯片架构

-

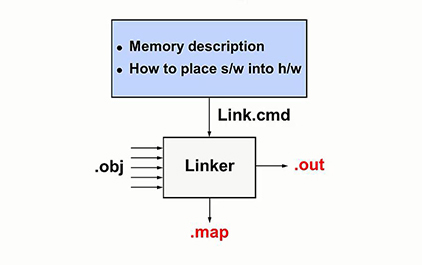

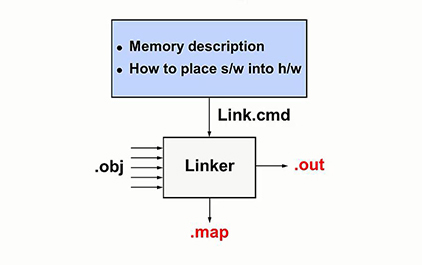

未学习 C2837x入门指南(三) — 开发环境

未学习 C2837x入门指南(三) — 开发环境

-

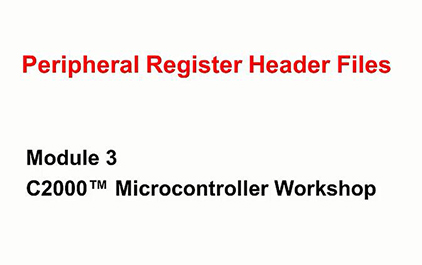

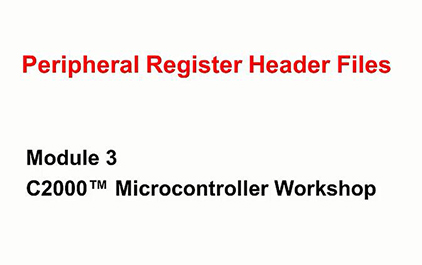

未学习 C2837x入门指南(四) — 外设寄存器操作

未学习 C2837x入门指南(四) — 外设寄存器操作

-

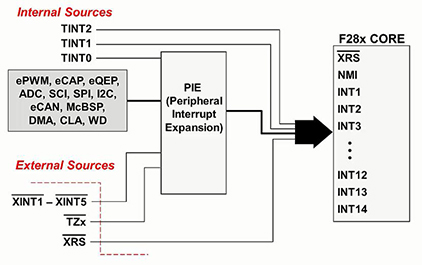

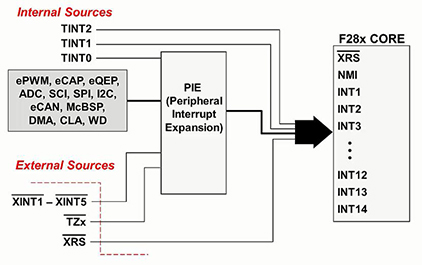

未学习 C2837x入门指南(五) — 复位和中断

未学习 C2837x入门指南(五) — 复位和中断

-

未学习 C2837x入门指南(六) — 系统初始化

未学习 C2837x入门指南(六) — 系统初始化

-

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

-

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

-

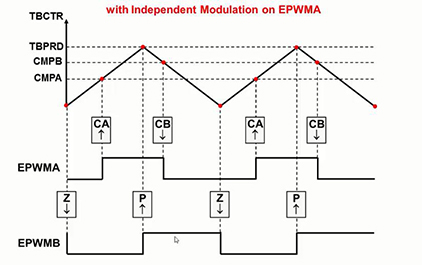

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

-

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

-

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

-

未学习 C2837x入门指南(十二) — DMA模块(上)

未学习 C2837x入门指南(十二) — DMA模块(上)

-

未学习 C2837x入门指南(十三) — DMA模块(下)

未学习 C2837x入门指南(十三) — DMA模块(下)

-

未学习 C2837x入门指南(十四) — CLA模块

未学习 C2837x入门指南(十四) — CLA模块

-

未学习 C2837x入门指南(十五)—系统设计之调试仿真

未学习 C2837x入门指南(十五)—系统设计之调试仿真

-

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

-

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

-

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

-

未学习 C2837x入门指南(十九)—双内核之间的通信

未学习 C2837x入门指南(十九)—双内核之间的通信

-

未学习 C2837x入门指南(二十)—通信系统之SPI

未学习 C2837x入门指南(二十)—通信系统之SPI

-

未学习 C2837x入门指南(二十一)—通信系统之SCI

未学习 C2837x入门指南(二十一)—通信系统之SCI

-

未学习 C2837x入门指南(二十二)—通信系统之McBSP

未学习 C2837x入门指南(二十二)—通信系统之McBSP

-

未学习 C2837x入门指南(二十三)—通信系统之IIC

未学习 C2837x入门指南(二十三)—通信系统之IIC

-

未学习 C2837x入门指南(二十四)—通信系统之USB

未学习 C2837x入门指南(二十四)—通信系统之USB

-

未学习 C2837x入门指南(二十五)—通信系统之CAN

未学习 C2837x入门指南(二十五)—通信系统之CAN

-

未学习 C2837x入门指南(二十六)—开发工具汇总

未学习 C2837x入门指南(二十六)—开发工具汇总

-

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

-

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)