电机驱动

最新课程

- CCStudio™ Edge AI Studio for Time Series - 概述

- ADS9327系列精密ADC

- TI 增强型 MSPM0C MCU 系列,可简化系统设计

- 高级门驱动学习课程

- TAS2020EVM 入门

- F29 实时 MCU

- 如何使用 Edge AI Studio 进行基于雷达的表面分类

- 介绍 1L 调制

- HSS Smart Configurator GUI 概述

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

热门课程

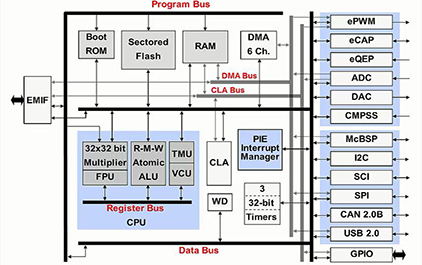

C2837x入门指南(五) — 复位和中断

大家好 本章节我们讨论的是

复位和中断

我们先了解F28x系列芯片复位以后流程是怎么样的

然后讨论F28x的中断架构

首先 F28X芯片存在五种复位源

看门狗复位 升电复位

休眠复位 XRS引脚本身电频变化引起的外部复位

以及检测到时钟丢失的复位

其中 时钟丢失复位 仅仅是芯片本身和外设

并不会在XRS复位引脚上产生电频

其他四种都会在XRS复位引脚上产生电频

另外 CPU1的看门狗复位

会复位CPU1和CPU2两个内核

但CPU2的看门狗复位 仅仅复位CPU2一个内核

reset cause register RESC寄存器只会记录最后一次复位的源是什么

芯片复位以后会进入boot引导模式

双核CPU引导的流程是

CPU1新执行自己的boot ROM

并一直控制的boot流程

而CPU2一直处于复位状态

除非CPU2配置到flash启动

从CPU1的控制下执行自己的boot ROM

并且决定如何启动

在此期间

双核之间是通过IPC核间通讯的寄存器实现信息的交互

boot ROM里面具体会做哪些事情

我们以CPU1内核为例来讲解

复位之后全级中断是关闭的

PIE也被禁止

复位相量找到boot ROM里面地址开始执行boot的代码

第一件事情就是检测

是否有仿真器连接

区分是进入仿真模式还是脱机模式

这个检测仅检测芯片上TRST广角上电频的高低

高电频表示是仿真模式

低电频是脱机模式

在仿真模式下 Boot会查看 EMU boot control计算器的wait

EMU_KEY的值是不是0x5A

不是的话 就进入等待模式

否则会继续查看 EMU Boot control计算器的wait

EMU Bmode的值是不是0xFE

是根据默认的GPIO72和84的状态决定

往哪里引导

否则查看EMU BMODE的值是不是0xFF

是就表明用户更改了默认的 GPIO boot的引脚模式和引导模式

否则继续查看BMODE的值

根据不同的组合决定 引导到内存

或者通信外设

如果它等于0x03

进入get mode

还需要查看OTP KEY值是否为0x5A

来决定引导到flash 或内存或通信外设

在脱机模式下

boot会查看两个GPIO引脚

GPIO72和GPIO84的状态

以及ZXOTP Bootcontrol计算器的wait

OTP key和OTP Bmode的值决定

引导内存或者通信外设

大致流程与仿真模型类同

因此 总的来看

复位以后 芯片进入boot ROM去执行代码

先判断是进入仿真还是脱机模式

然后根据EMU control计算器

两个GPIO管脚 GPIO72和GPIO84的状态 和ZXOTP bootcontrol计算器的值决定

来决定引导内存或通讯外设

进行运行

那如果是引导了flash

我们的应用程序最终是如何经过main函数的呢

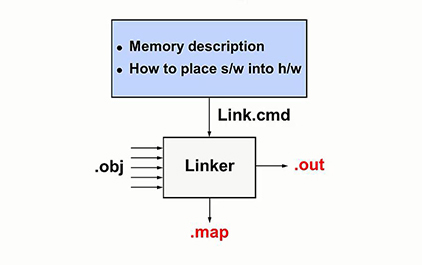

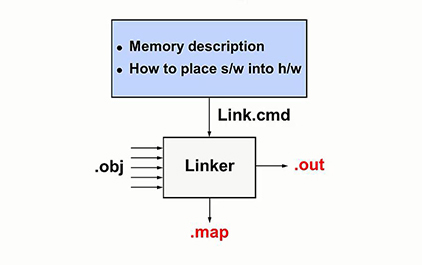

简单来说 在应用程序中

你需要设定一个codestart

然后让这个段执行一个

C_int00的函数

这个函数是TI提供的库函数

它会执行建立编译环境

建立C语言运行环境 和进行内存清理的工作

在完成这些工作后

它就自动调用lin函数

然后就进入了应用程序的控制范围

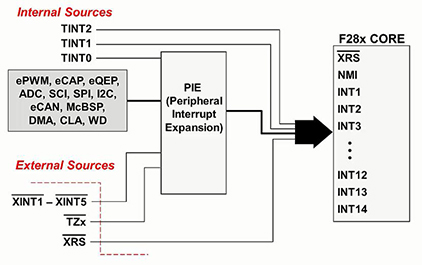

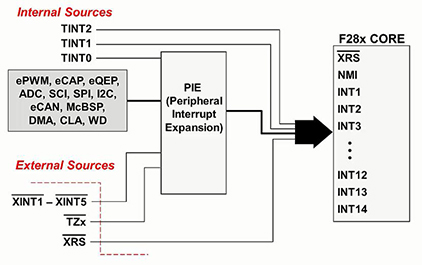

接下来 我们介绍中断

中断源本身跟之前芯片没有很大差别

只是增加了新的外设

同样都是进入PIE进行管理

然后它既有内部中断 也有外部中断

在可屏蔽中断的处理上

首先有一个全局中断开关

由INTM控制

只有当它被使能 可屏蔽中断才能被接收

并响应

其次 它将中断分成了14组

每组有一个中断使能位进行控制

同理 只有该组所在为被使能

该组包含的中断 才可能被接受并响应

同时 它还有一个标志位

无论是否使能IER 只要该组有中断发生

就会置位

这是IFR计算器的未定义

它可以被手动置位或清零

原始操作可以保证它在置位或清零的时候

不会被打断

IER计算器 是实现使能或禁能的功能

它和IFR一样 不能像外设寄存器一样

对未进行寄存器里操作

而必须使用Mask处理

置位表示使能 清零表示禁能

全局中断使能位 在ST1计算器中的定义

复位后的1表示禁能

它只能通过汇编语言进行操作

asm CLRC INTM是使能

asm SETC INTM是禁能

外设中断 总共分为12组

最多支持为扩展以后

为192个 每组16个

每组里面的每个中断 有自己的标志位和使能位

比如第一组是PIEFR1 和FIEIER1

只有当标志位置起 使能位被打开

才能让后一个IER和IFR等待响应

这个是所有中断的分配表

先是12组的低位八个

然后是12组的高位八个

可以看到 其实还有很多空位是预留的

具体到一组的PIE的计算器

从PIEFR到PIEIER PIEACK

到PIE control

中断信号理由大致是外设先产生中断

对应的INT X.Y会置位PIEFR

此时 如果PITIER对应的位被使能

内核的FR就会置位

如果此时IER对应位被使能

就会进入检查全局中断位INTM是否使能

如果使能 PIE就会根据

NTX.Y查找对应的中断相量表

然后响应相应的中断函数

对于双核F2837XD芯片来说

由于多了一个CPU 因此它多了一个PIE

所有这些外设中断 都可以进入任何一个PIE

当然 由于加入核间通信 它的中断可以被两个内核响应

最后是中断响应的硬件时序

首先 硬件上会自动保存14个CPU寄存器

不需要用户干预

然后 中断延迟

根据内外中断不同

会有两个cycle的差别

最小延迟对于外部中断来说

是16个cycles 对内部中断是14个cycles

最大延迟取决于等待状态和全机中断的状态

本章 我们主要讲解了复位和中断

了解了引导模式的工作流程和PIE是如何工作的

接下来我们继续介绍芯片的系统配置和初始化

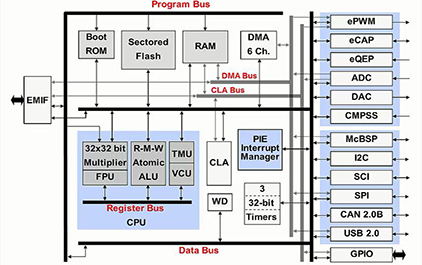

之后就可以开始了解和使用各种控制外设和通信外设

开始设计自己的终端产品了

-

未学习 C2837x入门指南(一) — 概述

未学习 C2837x入门指南(一) — 概述

-

未学习 C2837x入门指南(二) — 芯片架构

未学习 C2837x入门指南(二) — 芯片架构

-

未学习 C2837x入门指南(三) — 开发环境

未学习 C2837x入门指南(三) — 开发环境

-

未学习 C2837x入门指南(四) — 外设寄存器操作

未学习 C2837x入门指南(四) — 外设寄存器操作

-

未学习 C2837x入门指南(五) — 复位和中断

未学习 C2837x入门指南(五) — 复位和中断

-

未学习 C2837x入门指南(六) — 系统初始化

未学习 C2837x入门指南(六) — 系统初始化

-

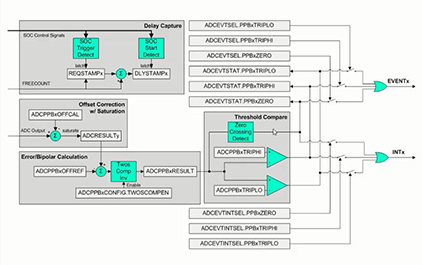

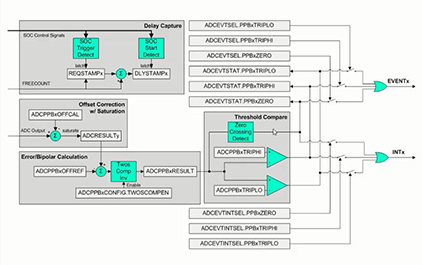

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

-

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

-

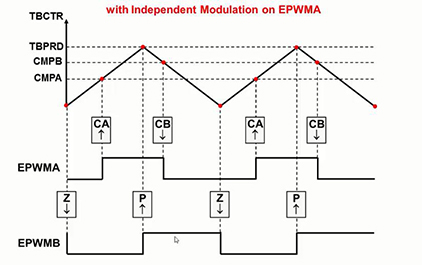

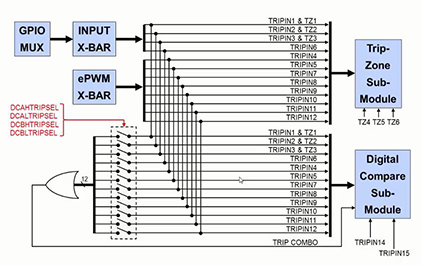

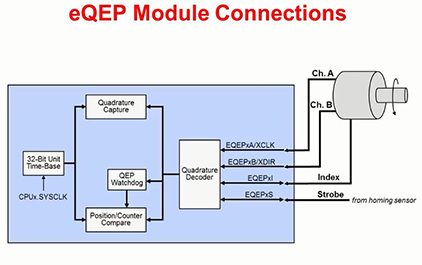

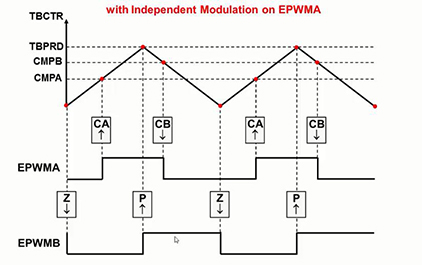

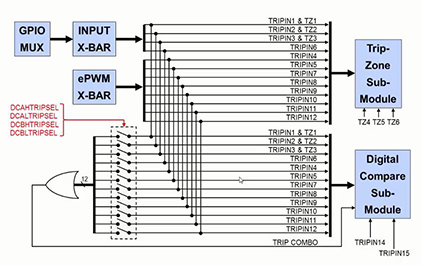

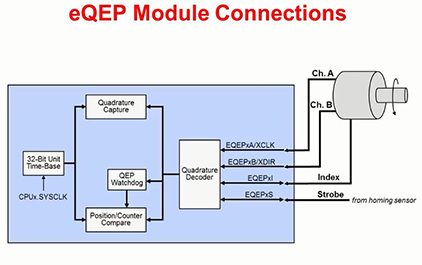

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

-

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

-

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

-

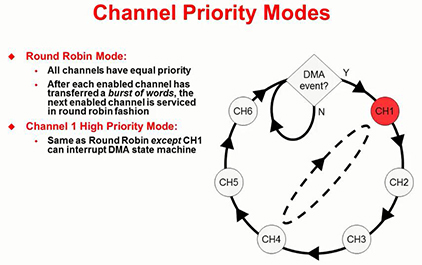

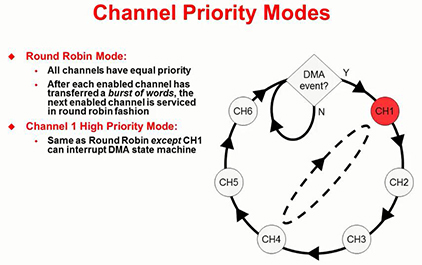

未学习 C2837x入门指南(十二) — DMA模块(上)

未学习 C2837x入门指南(十二) — DMA模块(上)

-

未学习 C2837x入门指南(十三) — DMA模块(下)

未学习 C2837x入门指南(十三) — DMA模块(下)

-

未学习 C2837x入门指南(十四) — CLA模块

未学习 C2837x入门指南(十四) — CLA模块

-

未学习 C2837x入门指南(十五)—系统设计之调试仿真

未学习 C2837x入门指南(十五)—系统设计之调试仿真

-

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

-

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

-

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

-

未学习 C2837x入门指南(十九)—双内核之间的通信

未学习 C2837x入门指南(十九)—双内核之间的通信

-

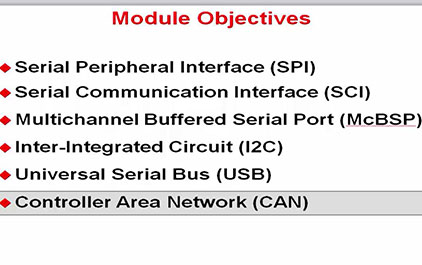

未学习 C2837x入门指南(二十)—通信系统之SPI

未学习 C2837x入门指南(二十)—通信系统之SPI

-

未学习 C2837x入门指南(二十一)—通信系统之SCI

未学习 C2837x入门指南(二十一)—通信系统之SCI

-

未学习 C2837x入门指南(二十二)—通信系统之McBSP

未学习 C2837x入门指南(二十二)—通信系统之McBSP

-

未学习 C2837x入门指南(二十三)—通信系统之IIC

未学习 C2837x入门指南(二十三)—通信系统之IIC

-

未学习 C2837x入门指南(二十四)—通信系统之USB

未学习 C2837x入门指南(二十四)—通信系统之USB

-

未学习 C2837x入门指南(二十五)—通信系统之CAN

未学习 C2837x入门指南(二十五)—通信系统之CAN

-

未学习 C2837x入门指南(二十六)—开发工具汇总

未学习 C2837x入门指南(二十六)—开发工具汇总

-

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

-

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)