电机驱动

最新课程

- CCStudio™ Edge AI Studio for Time Series - 概述

- ADS9327系列精密ADC

- TI 增强型 MSPM0C MCU 系列,可简化系统设计

- 高级门驱动学习课程

- TAS2020EVM 入门

- F29 实时 MCU

- 如何使用 Edge AI Studio 进行基于雷达的表面分类

- 介绍 1L 调制

- HSS Smart Configurator GUI 概述

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

热门课程

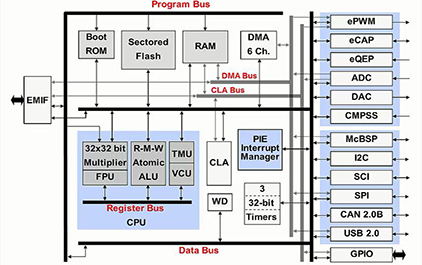

C2837x入门指南(二) — 芯片架构

本章节我们将要讨论的是整个芯片的系统架构

C28x主cpu及其相关的硬件加速器等

我们会先了解F28x7x器件的结构框图和芯片特性

描述其总线连接和内存分配

然后区分其片上各种不同类型的内存

最后确定不同器件上不同外设的配置情况

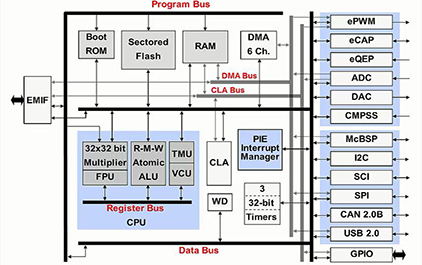

首先F28x7x器件的结构框图

在根本上和以往的C28x系列芯片的结构框图

没有大的差别

它的每个CPU都有自己的运算单元

程序和数据总线

可以访问到片上的所有外设

只是增加了DMA总线和CLA协处理器的总线

而在内部总线结构上

根据程序数据和外设的不同

他们可以分别通过不同的总线

访问到不同的区域

并统一协调工作

由于有独立的程序和数据的地址读写总线

并且都是32位的

其运行效率可以大幅提高

在处理器方面

除了32位的C28x主cpu

还有支持32位单精度浮点数运算的FPU

支持 viterbi 解码复数运算

和硬件CRC校验的VCU单元

支持单周期执行浮点三角运算的 TMU

和独立的32位浮点运算的CLA协处理器

用于并行处理控制算法和实时任务

除此之外还可以支持更加快速的中断响应

和单周期读改写操作指令等等

单周期读改写操作指令指的是

C28x内核支持的一种原子操作

它可以在一个指令执行周期内

完成一个操作数的读取修改和重新写入

更加简化代码和提高效率

因为其代码量可以更少

并且不会被打断

C28x采用的是八级流水线

在顺序执行的实时控制运行里

可以更大的发挥它的优势

从而保证它的运行效率

并且不需要用户担心其结果的异常

而之前提到的 FPU VCU 和 TMU

都是和C28主cpu共享流水线的

从第二解码开始

后面的读取和真正执行需要分时处理

但可以由汇编器和编译器

来检测到资源的冲突

并防止其发生

而且通常可以在指令间插入不冲突的指令

来利用这些等待空闲

从而提高程序的执行效率

在外设方面

我们提供了写读保护

以确保写入优先

比如控制位生效后再读取状态位

对于相同地址的寄存器

CPU的流水线会保证写入优先

然后对于在同一个大区域

但是不同地址的寄存器

写读保护就可以同样地保证这一点

对应的就是在芯片外设部分

我们设立了两个外设组

分别实施写读保护

在内存方面我们可以看到简化后的内存分配图

跟传统的C28x芯片一样

前端是 RAM 区

然后是 LS 需要的 RAM

和 GS 需要的 RAM

当然中间还包括两个主CPU之间交互的

MSG RAM和CPU和它自己的CLA交互的 MSG RAM

然后是用户的OTP和闪存Flash

最后是 Boot ROM

其中 GS 需要的 RAM 的任意一个段

都可以分配给任意一个主28CPU

但默认都是由CPU1控制

同理LS 需要的 RAM任意一个段

都可以分配给cpu和他自己的CLA

但默认也是由CPU本身来控制

在安全方面

加密模块由固定地址128位

密码保护所有的Flash

和绝大部分 RAM 改变成了现在的双加密模块DCSM

每个cpu可以设置两个不同的密码

并且由用户自己决定

哪个密码保护哪一段Flash和RAM或者是不保护

然后将该密码放置到OTP区域

以后每更换一次配置或者密码

就可以移动一次位置

增加了破解的难度

即便在200兆赫兹主频下

以八个周期

枚举一个密码的方式

至少也需要4.3乘以十的二十三次方年

才可能枚举出

所有可能的组合

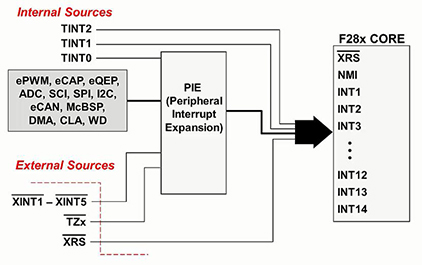

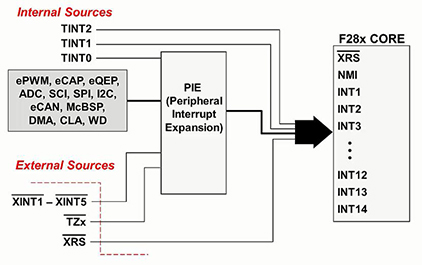

在中断部分基本上和原来的保持一致

会由cpu自动进行现场保护

和恢复相关的14个CPU寄存器和状态标志

不需要用户通过软件干预

然后经由PIE管理

从外设级到IAR级和cpu级

不同的是由于外设的中断个数的增加

2837xD的中断个数

由原来的96个扩展为两倍192个

在硬件加速单元的部分

VCU 主要是通过硬件

来实现一些在电力载波通讯应用中

需要编解码的算法

当然也可以独立使用

进行复数运算和CRC校验

而TMU这是在单周期内

完成基本的三角运算和除法运算

从而可以大幅提升相关变换执行的效率

当然所有这些运算都是支持浮点

除此之外在芯片本身的安全上面

从内存到时钟

从外设的读写和访问保护

再到引脚上的外部异常信号

都可以保证芯片运行在

更加安全和可靠的环境里

总之本章节我们首先是在

高层面上讨论了芯片的特性

接下来我们将会依次展开

进行更加细节的分析和探讨

-

未学习 C2837x入门指南(一) — 概述

未学习 C2837x入门指南(一) — 概述

-

未学习 C2837x入门指南(二) — 芯片架构

未学习 C2837x入门指南(二) — 芯片架构

-

未学习 C2837x入门指南(三) — 开发环境

未学习 C2837x入门指南(三) — 开发环境

-

未学习 C2837x入门指南(四) — 外设寄存器操作

未学习 C2837x入门指南(四) — 外设寄存器操作

-

未学习 C2837x入门指南(五) — 复位和中断

未学习 C2837x入门指南(五) — 复位和中断

-

未学习 C2837x入门指南(六) — 系统初始化

未学习 C2837x入门指南(六) — 系统初始化

-

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

-

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

-

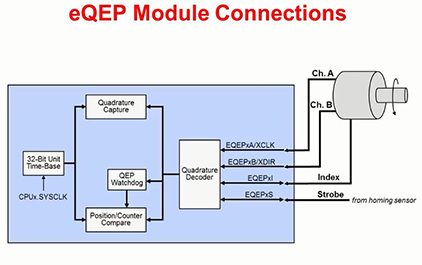

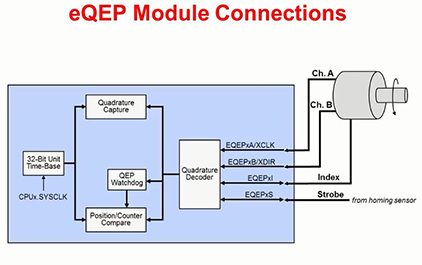

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

-

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

-

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

-

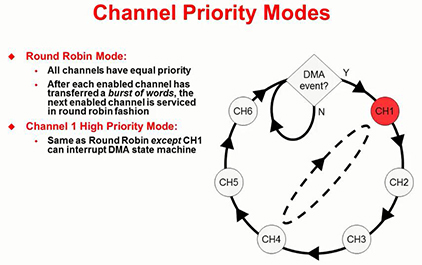

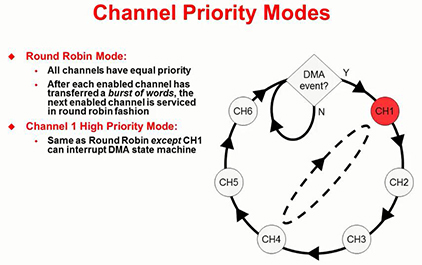

未学习 C2837x入门指南(十二) — DMA模块(上)

未学习 C2837x入门指南(十二) — DMA模块(上)

-

未学习 C2837x入门指南(十三) — DMA模块(下)

未学习 C2837x入门指南(十三) — DMA模块(下)

-

未学习 C2837x入门指南(十四) — CLA模块

未学习 C2837x入门指南(十四) — CLA模块

-

未学习 C2837x入门指南(十五)—系统设计之调试仿真

未学习 C2837x入门指南(十五)—系统设计之调试仿真

-

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

-

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

-

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

-

未学习 C2837x入门指南(十九)—双内核之间的通信

未学习 C2837x入门指南(十九)—双内核之间的通信

-

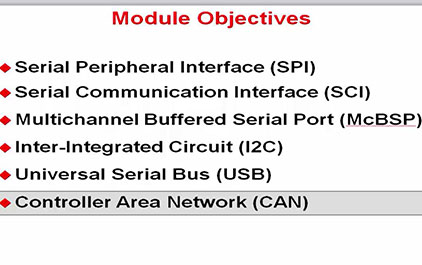

未学习 C2837x入门指南(二十)—通信系统之SPI

未学习 C2837x入门指南(二十)—通信系统之SPI

-

未学习 C2837x入门指南(二十一)—通信系统之SCI

未学习 C2837x入门指南(二十一)—通信系统之SCI

-

未学习 C2837x入门指南(二十二)—通信系统之McBSP

未学习 C2837x入门指南(二十二)—通信系统之McBSP

-

未学习 C2837x入门指南(二十三)—通信系统之IIC

未学习 C2837x入门指南(二十三)—通信系统之IIC

-

未学习 C2837x入门指南(二十四)—通信系统之USB

未学习 C2837x入门指南(二十四)—通信系统之USB

-

未学习 C2837x入门指南(二十五)—通信系统之CAN

未学习 C2837x入门指南(二十五)—通信系统之CAN

-

未学习 C2837x入门指南(二十六)—开发工具汇总

未学习 C2837x入门指南(二十六)—开发工具汇总

-

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

-

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)