电机驱动

最新课程

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

- 重新构想人工智能数据中心电源:从电网到终端的全链路方案

- 如何将 PurePath Console (PPC3) 用于 TI 音频转换器

- 为人形机器人提供安全高效运行的动力保障

- 《使用 C2000 IDE-Assist 从 F28x 迁移到 F29x》视频

热门课程

C2837x入门指南(二十三)—通信系统之IIC

我们来看看I2C模块 I2C是一个非常通用的总线

我们2837X的I2C 支持的是飞利浦的2.1的模式

支持的数据传输速率是从10kbps到400kbps

那我们要注意 我们不支持高速的模式

那么I2C总线的话

其实它和之前的SPI USB等等不同

它是有一个特定的主机的

I2C总线上的每个器件都有可能作为主机

或者是从机 在某个时刻

主要是具体是哪个器件作为主机的话

是根据总线的某个器件

发起的数据传输以及生成了时钟 同时占据了数据总线

这个器件就作为数据总机

那被它所寻址的那个器件 就作为从机

也比如说 这个器件发起了数据

它产生了时钟信号 它是主机

它寻址 需要沟通的是这个器件的话

这个被沟通的器件 被通讯的器件

就作为从机

而且I2C是支持多主机的模式的

I2C的数据发生主要是两种模式

第一是标准模式 就是说我的是比较精准的发送

标准的器件 这数据的格式 写的字节

是更精确的

还有一个是repeat模式 也就是我不断发送

软件产生一个停止信号 或者新的启动条件成立的时候

启动的时候 才会停下来

这个是一种repeat的模式

重复的模式

那下面这图是I2C总线的一个框图

我们可以看到 在总线上必须通过两个上拉电阻

拉到VDD

最主要的作用是需要让总线在没有数据发送时

让总线保持高电平的状态

每个器件只需要SDA和SCL两根线就可以挂到总线上

SDA主要是作为数据中心 数据交换

SCL主要是作为产生磁通用

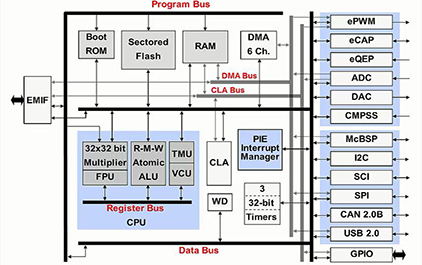

我们看看I2C模块的系统框图

它这个系统框图 非常方便 对外只需要两根线

一个是SDA数据线 一个是SCL时钟线

SDA作为数据线 数据接收和发送主要是靠

12C的移位 发送移位寄存器和接收移位寄存器 和自己的数据结构结合

以及相对应的16位的FIFO

来构成

那么I2C总线上的某个器件 每个器件工作模式的主要有四种

一个是从机接收模式

一个是从机的发送模式

一个是主机的接收模式 一个是主机的发送模式

那么每个器件只能处在四个工作模式中的一种

我们先来看看 数据发送从最开始

主机 然后到从机的状态是如何切换的

首先作为一个主机的话 首先是触动主机的发送状态

首先发送出去 并产生时钟

来控制总线 首先是发出了这个数据

包括通讯的设备的从机地址 它是要读数据还是写数据等等这些

是作为主机的发送模式

这个时刻 从机所有的器件首先 都会接收到这个广播信号一样的

然后分别进行地址识别

假如 某个器件识别到了它的地址和自己的地址

是相互吻合的 那么这个器件就变成从机的发送模式

接收模式

它会根据主机发送的指令

是否需要发送数据 假如需要发送数据给主机的话

它会进入到从机的发送模式

将指定的地址和数据发送给主机

那么这时候主机就会 从主机的发送模式切换为主机的接收模式

来接收从机发送过来的数据

在四种状态之间 是可以切换的

器件从主机的发送模式会进入到主机的接收模式

从机的接收模式变成从机的发送模式

这个方向是单向的

我们看看I2C的数据格式

I2C数据主要是包括有7种模式

3种模式

一个是7位的地址模式

10位的地址模式 一个是自由的模式

7位的地址模式 是启动时将7位的从机地址发送出去

然后pin给出读写指令

然后所需要操作的数据和一些应答位

在这个里面的 一个R/W的读写控制位的话

假如说这个位等于0的时候 主机将数据写入到从机的地址中

假如说这个地方是1的话 主机会把这个数据

从从机这个指定的地址读取回来 那10位的地址格式

跟7位是一样的

不过我的地址是10位的

首先地址是发高位

高的两位先发出去

其他地方有11110来填充

然后紧接着是低位的地址 8位的信号

然后是数据

自由的话 就没有地址在线

每个数据之间都会加入ACK应答信号

这个地方的S和P指的是

从启动到停机

启动主要用的是 SAR在有效传导时候

SDA从无效变成低电平 从高电平变成低电平

启动信号 同样是停止的话

是从低电平到高电平

这时候会停止信号

那么我们再来看 I2C的仲裁

I2C的仲裁主要是用于什么地方

如果总线有多个组发送器 同时开始发送数据

总线上的数据肯定会产生冲突

这个时候需要I2C的仲裁机制介入

仲裁遵循的一个原则是 程序中的竞争

发送器发送使SDA提供的数据能够

SDA被拉低

的那个占据优先权 占据数据优先权

这个比较拗口 我们解释就是说

这个是一个时钟信号

假设有2个 device1和device2都发送数据的话

第1个点全部是高电平

在SDA上保持高电平

然后第二个它们都变成低电平

第三个的时候 第三个clock上升点的时候

device1会拉高 device2继续保持0

这个时候就device2占据了总线

因为它需要的能耗比较小

低电平 device1的话

就失去了对总线的一个控制权

总线控制丢失的话 在芯片内部

会产生总线丢失的一个错误中断

客户可以在这个中断里面进行相应的处理

这个是I2C的仲裁

其实I2C通讯总线 我们做一个总结归纳

它主要是支持飞利浦I2C 2.1的版本

地址寻位是7位和10位的

发送数据时候是从10kbps到40kbps

等等

然后它也支持接收和发送FIFO

同时这里的接收和发送FIFO能产生

接收和发送的中断

-

未学习 C2837x入门指南(一) — 概述

未学习 C2837x入门指南(一) — 概述

-

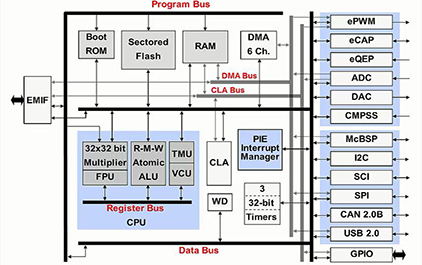

未学习 C2837x入门指南(二) — 芯片架构

未学习 C2837x入门指南(二) — 芯片架构

-

未学习 C2837x入门指南(三) — 开发环境

未学习 C2837x入门指南(三) — 开发环境

-

未学习 C2837x入门指南(四) — 外设寄存器操作

未学习 C2837x入门指南(四) — 外设寄存器操作

-

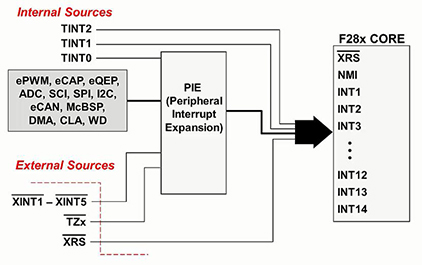

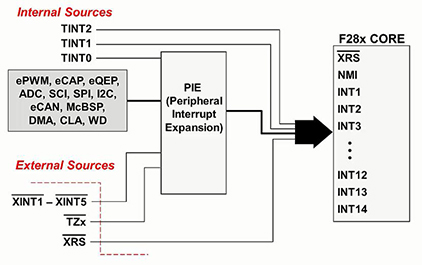

未学习 C2837x入门指南(五) — 复位和中断

未学习 C2837x入门指南(五) — 复位和中断

-

未学习 C2837x入门指南(六) — 系统初始化

未学习 C2837x入门指南(六) — 系统初始化

-

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

-

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

-

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

-

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

-

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

-

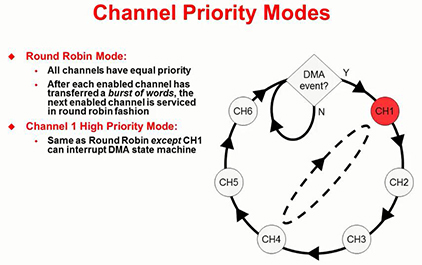

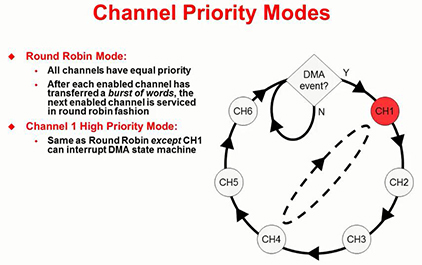

未学习 C2837x入门指南(十二) — DMA模块(上)

未学习 C2837x入门指南(十二) — DMA模块(上)

-

未学习 C2837x入门指南(十三) — DMA模块(下)

未学习 C2837x入门指南(十三) — DMA模块(下)

-

未学习 C2837x入门指南(十四) — CLA模块

未学习 C2837x入门指南(十四) — CLA模块

-

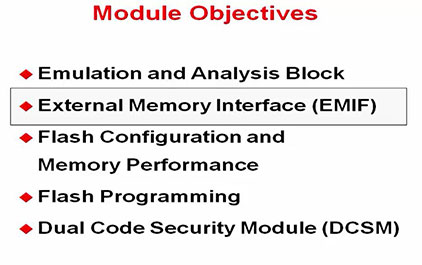

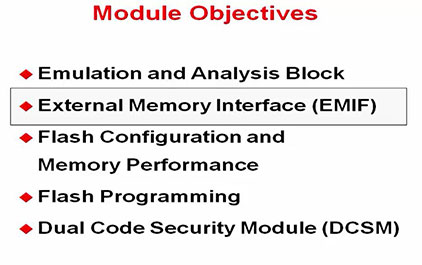

未学习 C2837x入门指南(十五)—系统设计之调试仿真

未学习 C2837x入门指南(十五)—系统设计之调试仿真

-

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

-

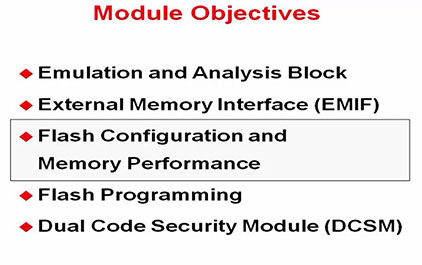

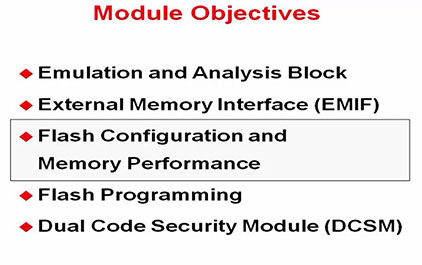

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

-

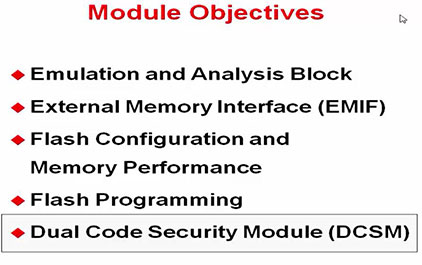

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

-

未学习 C2837x入门指南(十九)—双内核之间的通信

未学习 C2837x入门指南(十九)—双内核之间的通信

-

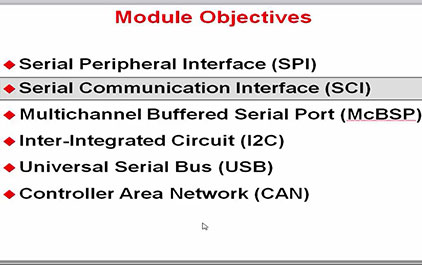

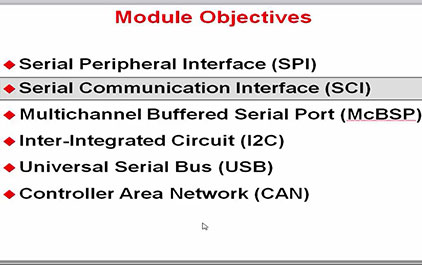

未学习 C2837x入门指南(二十)—通信系统之SPI

未学习 C2837x入门指南(二十)—通信系统之SPI

-

未学习 C2837x入门指南(二十一)—通信系统之SCI

未学习 C2837x入门指南(二十一)—通信系统之SCI

-

未学习 C2837x入门指南(二十二)—通信系统之McBSP

未学习 C2837x入门指南(二十二)—通信系统之McBSP

-

未学习 C2837x入门指南(二十三)—通信系统之IIC

未学习 C2837x入门指南(二十三)—通信系统之IIC

-

未学习 C2837x入门指南(二十四)—通信系统之USB

未学习 C2837x入门指南(二十四)—通信系统之USB

-

未学习 C2837x入门指南(二十五)—通信系统之CAN

未学习 C2837x入门指南(二十五)—通信系统之CAN

-

未学习 C2837x入门指南(二十六)—开发工具汇总

未学习 C2837x入门指南(二十六)—开发工具汇总

-

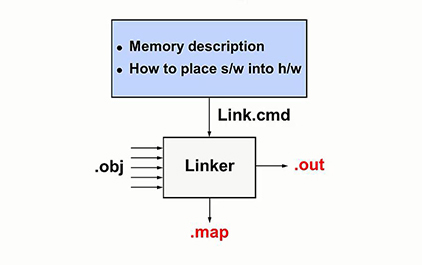

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

-

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)