掌握高压门驱动器设计的艺术和基础

Loading the player...

将在30s后自动为您播放下一课程

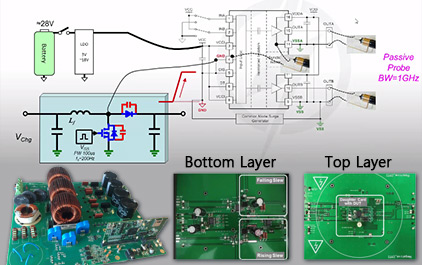

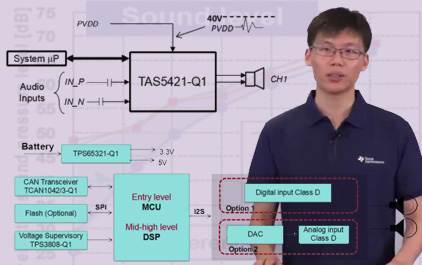

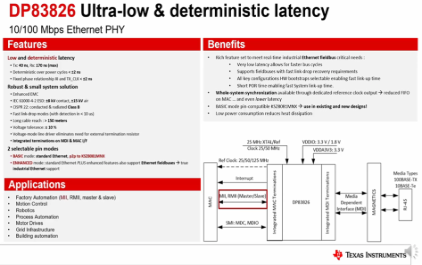

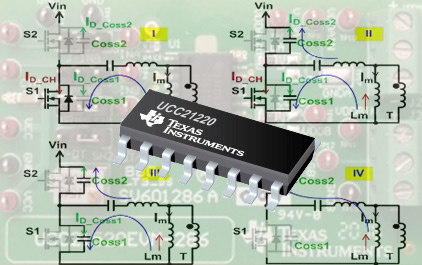

大家好! 我叫张伟(音译)。 是 TI 的系统 应用工程师。 本次培训服务 将探讨 专为 UPS、电信 和服务器等 各种应用中的 MOSFET、IGBT 和 宽带隙器件(例如 碳化硅和氮化镓) 设计的高压栅极驱动器。 本次培训将 涵盖哪些内容? 我们将介绍栅极 驱动器应用, 并说明低侧 驱动器、高侧和 低侧驱动器以及 隔离式栅极驱动器。 我们还将深入 探讨栅极驱动器的 设计注意事项,包括 寄生效应、硬软开关、 高 dv/dt 和 di/dt 以及 隔离式栅极驱动器注意事项, 以介绍如何最大 限度地提高栅极 驱动器的性能。 本演示所使用的 器件包括 UCC2751、 52 和 x24 低侧 驱动器 以及 600 伏 驱动器,即 2771x。 此外,还包括隔离式栅极 驱动器系列, 即 2152x、2122x 和 UCC53 系列。 有关更多详细信息, 请参阅 TI.com 上的 其他参考设计。 在这个培训系列中, 我们将介绍 栅极驱动器应用以及 低侧栅极驱动器、 高侧/低侧栅极 驱动器及 隔离式栅极驱动器的基本知识。 我们会深入 讨论并利用 TI 参考设计 帮助您了解栅极 驱动器的设计 注意事项,还将 介绍相应的关键波形。 栅极驱动器的 应用非常广泛, 我在这里举几个例子, 比如便携式设备的 电池管理系统、直流电源 适配器、服务器/电信/UPS、 电动汽车充电器 以及电机驱动器和 D 类音频。 此外还包括厨房、 可再生能源和 固态照明领域中的应用。 总而言之, 栅极驱动器 无处不在,用于实现 高效的电源转换。 我们来看看服务器/电信设备的 典型电源 [听不清], 它的前端与公用电网连接, 并进行功率因数 校正,建立 400 伏直流 总线,后跟隔离式直流 /直流转换器和 [听不清] 电平砖型总线转换器 以及负载点。 在示例电路中,我 挑选了两个通道, 交错升压用于 PFC,IOC 用于 隔离直流/直流转换器, 全桥用于 总线转换器。 总共有大约 10 到 20 个开关, 用于几百瓦的简单 前端转换器。 利用常用的图腾柱 PFC,您可以期待 通过更多有源器件 实现更佳的性能。 重要的是,每个开关 都需要栅极驱动器。 单通道或双通道 低侧栅极驱动器、高侧 和低侧栅极驱动器 (用于高桥), 既可以是 100 伏, 用于 48 伏总线, 也可以是 600 伏,用于 400 伏总线。 对于隔离栅,可以 根据系统安全要求 使用单通道或双通道 隔离式栅极驱动器。 对于双向电动 汽车充电器, 所有高压开关 和电机会 驱动电动汽车 以及由电池供电的工具。 高侧和低侧半桥 驱动器更为流行。 再说一次,如果控制器 位于不同的接地 参考,则 应使用单通道 或双通道隔离式 栅极驱动器。 现代电力电子装置 以开关模式 电源转换为主。 常用的器件,包括 MOSFET、IGBT 以及 碳化硅和氮化镓 等新技术, 都会使用高 开关频率。 栅极端子会控制 MOSFET 和 IGBT 的导通和关断。 要导通通常关断 的器件, 需要施加一个高于 此阈值的器件电压。 要将其关断, 您可以将栅极 下拉至 0,或者使用 负电压关断。 栅极是一个电容输入, 具有高阻抗以及 栅极至漏极 (即 CGD)和栅极 至栅源 (即 CGX)寄生电容。 这里展示了一些 常用的功率半导体, 包括碳化硅 IGBT、碳化硅 MOSFET 和氮化镓器件。 它们是不同的。 对于硅 MOSFET,在将其 驱动至高电压时, 通常 为 10 伏至 15 伏。 对于低压 MOSFET,它可以 使用 5 伏至 7 伏的 电压驱动。 IGBT 可能具有更高的 阈值,也会被驱动至 [听不清] 以上, 通常使用的是 15 伏的驱动电压。 碳化硅 MOSFET 稍微 有所不同, 在器件完全导通时, 某些器件可能需要 更高的电压。 需要使用 20 伏的电压 使其完全导通。 对于 IGBT 和 碳化硅, 在严苛的条件下,您可能需要使用 负电压来关断器件, 以确保噪声不会 意外地使器件 导通。 对于氮化镓 器件,此处的 示例展示了对于 采用增强模式的 GaN 器件,完全 导通电压 (例如 5 伏) 与绝对最大 电压(大约为 6 至 7 伏) 之间非常小的裕量。 所以,当我们驱动 不同的开关时, 需要谨慎 选择栅极驱动器, 在设计栅极驱动器 电路时 也是如此。 例如,在服务器和 电信电源应用中, 低侧栅极驱动器 可用于驱动 PFC 级 中的有源开关。 也可以用于 为总线转换器级 驱动同步整流, 因为电源开关 都是接地基准开关。 低侧驱动器能够 以分立的方式 实现,其中采用大量的 低电压晶体管,用于 电平转换器和 图腾柱 [听不清] 级。 由于大量的 分立器件、 组件尺寸、PCB 布局 以及非音频封装 和 PCB 迹线引入的 寄生效应,缺点 是 [听不清]。 所有这些分立器件 可以轻松为智能芯片 集成可靠性保护 功能优化以及 驱动器性能,例如 峰值驱动电流、 极小的 传播延迟、 更好的脉宽失真度 和极小的 [听不清] 电流消耗。 对于低侧栅极 驱动器,您可以 选择单通道 和双通道。 单通道和 双通道都是同相输入。 如左下角的 示例中所示, 器件具有两个 输入引脚,可以 分别连接两个输入, 因此对同相和反相 输入来说是通用的。 此外,可以 拆分输出引脚, 用于编程 不同的导通和关断, 因此在需要加快关断速度时 可以减少所需的外部组件。 与上一页中 介绍的 低侧驱动器类似, 半桥配置中的低侧 栅极驱动器 相对简单、直观。 输入和输出 具有传播延迟。 由于高侧 驱动器 不以接地端为基准, 需要使用电平 [听不清] 电路 来连接 接地基准输入。 要为高侧驱动器 供电,最常用的 方法是使用自举 配置,在底部 FET 导通时为自举 电容器充电。 如幻灯片中所示,您具有 以接地端为基准的输入。 但输出电压 以 100 伏至 700 伏的 开关模式为基准。 HO 与 HS 之间的差值 是高侧栅极驱动器 电压,它通常是 BDD 减去自举二极管的 满量程压降。 某些应用甚至集成了 自举二极管,从而方便 客户使用。 利用输入滤波器 和分离开/关, 它通常展示了 用于高侧和 低侧驱动器的 全功能电路。 下面是前面页面中讨论的 关键规格的 简短总结。 我们提到的 用于驱动各种 FET 的 欠压锁定和 VDD 事件最大值, 对于增强模式 GaN, 事件最大值可以低至 7 伏, 对于碳化硅,事件 最大值可以高达 35 伏。 为了满足不同的 导通和关断 要求,峰值拉电流 和灌电流可以是 对称的,也可以 不对称。 多种输入逻辑、 TTL 和 CMOS 输入 允许从控制器输入, 控制器的电压通常 低于 3.3 伏。 CMOS 输入 要求 50% 以上的 VDD 才能导通 器件,这可带来 更强的抗噪能力。 但它可能需要为 TSP 或 FPGA 控制器配备一个缓冲器。 采用自举配置 的高侧和低侧 栅极驱动器 具有一个 电平转换器, 总线电压为 48 伏时, 转换器最高电压为 100 伏, 总线电压为 400 伏时, 转换器最高电压为 700 伏。 动态参数 包括导通和 关断传播延迟、 上升时间 和下降时间、 延迟匹配 以及最小导通和关断脉冲。 所有这些动态 参数都很重要—— 瞬态响应、 开关损耗和 高频运行。 此外,封装 也很重要。 TI 支持 典型 SOIC 封装, 也支持 2 x 2 的 小型封装。 安全合规性也是 一个重要因素, 因为电源可能会 与公用电网连接 安全操作员也会接触到它。 对于次级侧 控制架构, 不仅应在通常是 电源变压器的 功率级中实现 隔离,还应在控制器 和驱动电路中 实现隔离。 这里列出了 IEC 标准, 增强型隔离 需要 3kV 以上、 最高 5kV 的隔离电压。 那么,我们应该如何 在栅极驱动器上 实现此隔离呢? 栅极驱动器变压器 是可实现此隔离的 一种传统、常用的方法。 在顶部开关栅极 驱动的示例中, 低侧栅极驱动器 利用补偿电路 (包括 C4、C6 和 D1、D2) 提供驱动信号 放大器和栅极 驱动器变压器输入。 栅极驱动器变压器 不但会提供 信号,还会提供 从输入至输出的电源隔离。 这种配置的缺点是, 不仅需要使用 两个庞大的栅极 驱动器变压器,还需要具备 波段瞬变性能, 以支持脉宽 失真控制策略。 这里我们来比较一下 两种常用的方法, 栅极驱动变压器作为 A 类型,数字式振荡器 加高侧和低侧 驱动器作为 B 类型。 比较这两种解决方案。 从传播延迟的角度而言, 栅极驱动变压器表现 出色,它还传输 信号和电源。 B 类型具有 不确定的 更大传播延迟,需要 用于次级复位的电源。 不过,为了具有 干净的驱动信号, A 类型需要 大量的辅助电路, 并要求相对大的 输入和输出电容和漏电感, 因此,预计会 产生更大的过冲。 还要考虑尺寸, 这里有一个示例。 对于增强型 隔离下的尺寸比较, 此仅考虑关键参数, 其中包含 PCB 面积 和体积。 B 类型可以节省 几乎一半的 PCB [听不清] 尺寸 空间,由于变压器的 尺寸尴尬,它能够 节省多得多的 体积。 另一种类型的 驱动器在一个 被称为 ISO 驱动器的 芯片中集成了隔离器 和驱动器,这个芯片具有超过 每纳秒 100 伏的 CMTI 和 5kV 的 增强型隔离。 关系。传播延迟 仅为 19 纳秒, 脉宽失真 小于 5 纳秒。 重要的是,尺寸仅为 B 解决方案的一半, 与 A 类型相比可以节省 75% 以上的尺寸。 UCC21520 系列栅极 驱动器是业界最快的 5.7kV 隔离式双通道 栅极驱动器。 它还在 TI 的栅极驱动器 产品线中引进了 一个新的隔离系列。 集成式组件(包括 高级保护功能 和经过优化的 开关性能) 使得这款驱动器 能够用作 低侧栅极驱动器、高侧栅极驱动器、 低侧栅极驱动器上的 高侧栅极驱动器或者半桥栅极驱动器。 除了这些优势以外, 我们将讨论 具有 6A 和 4A 灌电流 和拉电流峰值的 栅极驱动器变压器,并将其 与 UCC21520 系列 进行比较。 它还支持 3 伏至 18 伏的 宽输入电压范围, 同时支持 6.5 伏至最高 30 伏的 宽输出电压 范围。 它还具有支持重叠和互锁 功能的可编程延迟 以及 0 纳秒至 5 微秒的 死区时间。 输出利用有源下拉 电路实现了失效防护。 此外,还提供了三个 欠压锁定选项—— 5 伏、8 伏和 12 伏, 用于驱动 各种 MOSFET、IGBT 和碳化硅 MOSFET。 好了,我们介绍了 所有基础 知识,看起来 一点儿也不难。 它就是一个驱动器而已, 有一个输入, 有一个输出。 不过,让我们保持 一颗好奇心,来看看 它对栅极驱动器 性能的系统级 影响,例如寄生效应、 软硬开关差异、 非线性输出电容和 CMTI、dv/dt、di/dt 以及非音频 PCB 布局。 我们来更深入地 探讨一下。 我要向您展示 驱动器在转换器 效率和可靠性方面发挥的关键作用。 就寄生效应而言, 结电容、PCB 迹线 和 [听不清] 电感以及 电阻都会产生 寄生 效应。 因此,导通 和关断 会稍微 复杂一些。 对于碳化硅 MOSFET 和硅 MOSFET,还有 寄生二极管,它也 被视为会产生 寄生效应。 在分段线性 图示中,导通 过程可以分为 三个阶段。 第一个阶段是 栅极驱动器 电压、路径阈值 和通道电流增大。 使用红线突出 显示的等效 电路表明 CGS 在这个 阶段处于主导地位。 在第二阶段, 对 CGT 充电 并使 VDS 电压降低。 第三阶段是 通过对 CGD 和 CGS 充电并进一步 降低 [? RDSN ?],来进一步增大栅极电压。 重叠 VDS 和 ID 会产生开关损耗。 具有最短 T1 至 T3 阶段的更强驱动器 会导致开关损耗减小。 关断条件与 导通条件类似。 现在我们在半桥 配置中放置两个 器件,从而让情况 变得更复杂一点。 在硬开关 应用中, 会发生二极管 反向恢复。 左上角显示了 关键波形。 这个反向恢复将 反映在顶部开关上, 通常会产生更多的 导通损耗。 对于硅 MOSFET 的 体二极管和 IGBT 的 反并联二极管, 有两种预期结果, 您可以 看到由反向恢复 产生的大量浪涌电流。 对于硅 MOSFET, 过冲可能 是正常 开关电流 的 5 倍以上,IGBT 相对较小。 主要原因在于 硅 MOSFET 的体二极管 是寄生二极管, 未经过全面优化, 而 IGBT 的 紧凑二极管 可以是超级快速 或软恢复二极管。 反向恢复会增大损耗, 导致电流电压 过冲和 di/dt 增大。 还会导致栅极 振荡,与共源电感、 [听不清] 和栅极 驱动信号耦合的 di/dt 丢失,并减慢 开关切换速度。 减慢这个速度的 方法之一是增加一个 二极管或使用隔离输出 栅极驱动器,以增大导通电阻。 您可以看到, 如果增大 RG, 峰值反向恢复 时间会缩短。 但这样的改善 仍然非常有限。 前一部分中 讨论的反向 恢复对于优化系统 效率和可靠性而言 确实是一个难题。 要进一步消除 该问题,软开关 正是解决之道。 与临界模式 图腾柱 PFC 和 IOC 转换器一样, 它们都会在 VDS 电压降至 0 后 导通器件。 对于软开关, 前面提到的 三个阶段现在 只剩下一个阶段。 没有中间充电过程。 在输出电容完全 放电后导通器件, 器件通道电流 由外部电路决定, 而不是由寄生效应决定。 与硬开关相比, di/dt 通常 非常低, 因此不会出现重叠。 不存在导通损耗。 由于栅极驱动器损耗 机制也会改变, 因此对于硬开关,假设 栅极驱动器电压 为 10 伏,阴影区域、 打开和关断区域 是栅极驱动器电路 中的总损耗。 每个周期的总能量 是总面积 Qg 乘以 10 伏 VGS。 对于软开关,由于 没有中间充电过程, 因此红色实线 表示导通轨道。 关断与硬 开关类似。 与硬开关栅极 驱动器损耗 相比,软开关的 损耗更小。 软开关可以消除 此导通损耗。 不过,关断 也是硬开关。 与快速模式 电流传导 类似,关断 电流加倍。 如果使用弱 驱动器来驱动 FET,那么开关 损耗肯定会增加。 这意味着驱动器具有 更低的灌电流能力。 在使用强大的栅极 驱动器时,您几乎 不会看到中间平坦区域, 并且重叠时段也会 最小化。 重要的是, 开关行为 不受栅极 电流控制, 而是受输出电容和 负载电流控制。 考虑高度 非线性电容, 右上角显示了 分段线性开关 波形。 初始阶段非常低的 dv/dt 会成为一个电容器, 低电压 非常大, 为 5 纳法、0 伏。 随后非常高的 dv/dt 和高电压 导致进一步 最小化的重叠面积。 此处是一个关断 超结 MOSFET 的 实验示例。 将波形放大,可以 看到栅极驱动器非常 干净,具有很短的 中间平坦时间。 VDS 以非常缓慢的速度 增大并且及早关断。 您可以看到,比例 仅为每分段 5 伏, 然后升高。 所有开关电压 和电流 在 VGS 完全关断 之后发生变化, 这意味着开关行为 不是受栅极驱动器控制, 而是受输出电容和负载电流控制。 尽管使用强大的栅极 驱动器时的重叠面积 已降至最低,但它仍然存在。 如果我们测量它, 肯定会看到重叠。 不过,这是真正的损耗吗? 让我们看一看 常用 IOC 电路的 关断机制, 并考虑到 每个器件都包含 一个通道、体二极管和一个 CDS。 在第一阶段, 底部 FET 导通, 电流流过 通道。 在第二阶段,通道 关断,通道电流 减小,剩余的电流 会对两个开关的 输出电容充电 和放电。 由于相对大的 电感负载, 开关转换期间的 负载电流保持 [听不清]。 在第三阶段,通道将关断。 所有负载电流用于 继续对输出电容充电和 放电。 在最后一个阶段,会实现 [? ZVS ?],电流会 流过 体二极管。 实际损耗仅在 第二阶段发生, 在这个阶段中,通道 电流和电压发生 重叠。 第三阶段只会对 输出电容充电和放电。 我们 知道,所有输出电容 能量将在软开关期间的 下一个周期中恢复。 具有更小的损耗 和关断是很好的。 不过,dv/dt 和 di/dt 取决于负载, 可能在非常重的负载下 生成高 dv/dt 和 di/dt。 对于开关节点 中的高 dv/dt, 其行为确实是 退出寄生电容的 噪声源,寄生电容 包括 电平转换器电容、 自举二极管或结电容。 在通过这个电容器 进行耦合时, 会向初级侧接地 基准注入噪声。 如果您丢失了干净的 接地,那么栅极驱动器可能会 出现故障。 在这个实验中, 存在波形输入, 但缺少输出过程。 15 安电流 将关断,左侧 图表显示了 氮化镓和 超结 MOSFET 的 dv/dt 以及栅极驱动器电阻。 正如您看到的, MOSFET 的 dv/dt 可以达到每 纳秒 50 伏以上。 氮化镓 甚至更高, 超过每纳秒 150 伏。 di/dt 具有 类似的趋势。 一种解决方案是为低侧 栅极驱动器添加电平 转换器,尝试分隔 电源接地和逻辑接地。 此外,在采用额外旁通 电容器的情况下, 通过增大自举 电容电阻、 增加充电回路以及增大 电感,将环路最小化 而且 dv/dt 噪声 将流过不同的 路径。 因此,将有更少的 噪声流过初级侧。 讨论了 dv/dt 之后, 我们来看一看 di/dt。 它与寄生 电感相关。 不幸的是, 寄生效应无处不在。 当 di/dt 较高时, 不但会减慢驱动器的速度, 还会导致开关 节点中发生 严重漏电。 例如,当关断 顶部开关时, 底部分支将具有 正 di/dt, 实际电路中会 同时存在寄生电感、[? HSP ?] 和过冲 漏电。 这个过冲会导致 驱动器故障、 后二极管过流以及 VHP 减去 VHS 之后过度充电。 为了提高 驱动器的稳健性, 新的 27714 栅极 驱动器可支持 负 70 伏、100 纳秒 和负 30 伏、 200 纳秒。 TIDA-01159 是一种紧凑、 易于评估的 参考设计,适用于 额定驱动功率级为 1 伏至 690 伏的 UCC21520。 这种设计适用于 所有具有半桥功率级 的设备。 板中内置了简单的 低成本隔离式电源, 用于驱动高侧开关。 这种设计演示了 如何并能够帮助客户 评估 UCC21520 栅极 驱动器众多 功能的性能, 栅极驱动器具有 5kV 隔离电压下的 高驱动力仪表、 适用于高 CMTI 环境 的稳健器件以及 采用碳化硅 MOSFET 的器件的高频 运行能力。 这种解决方案提供了 简单易用的 [听不清] 板,用于比较 采用传统电源 变压器的解决方案在 驱动半桥功率级 方面的性能。 与以前的设计 TIDA-01160 以及 UCC53 系列 栅极驱动器的其他 设计参考类似。 这种设计适用于 需要使用单个 隔离式栅极 驱动器来驱动 IGBT 或碳化硅 MOSFET 的设备。 关键终端设备包括 单相或三相 UPS、直流充电电源 和 [听不清] 系统。 板中内置了低成本的 隔离式电源, 用于驱动具有 负电压 [听不清] 的高侧 开关。 总的来说,我们介绍了 栅极驱动基础知识, 并介绍了 低侧、高侧和低侧 以及隔离式栅极驱动器。 我们还介绍了 寄生效应及其对 软开关和硬开关的影响、 具有强大栅极 驱动器的非线性输出电容、 CMTI、dv/dt 和 di/dt 以及如何隔离 dv/dt 产生的本底噪声。 有关更多信息,请 参阅 TIDA 参考设计。 非常感谢 您的观看。 503

大家好! 我叫张伟(音译)。 是 TI 的系统 应用工程师。 本次培训服务 将探讨 专为 UPS、电信 和服务器等 各种应用中的 MOSFET、IGBT 和 宽带隙器件(例如 碳化硅和氮化镓) 设计的高压栅极驱动器。 本次培训将 涵盖哪些内容? 我们将介绍栅极 驱动器应用, 并说明低侧 驱动器、高侧和 低侧驱动器以及 隔离式栅极驱动器。 我们还将深入 探讨栅极驱动器的 设计注意事项,包括 寄生效应、硬软开关、 高 dv/dt 和 di/dt 以及 隔离式栅极驱动器注意事项, 以介绍如何最大 限度地提高栅极 驱动器的性能。 本演示所使用的 器件包括 UCC2751、 52 和 x24 低侧 驱动器 以及 600 伏 驱动器,即 2771x。 此外,还包括隔离式栅极 驱动器系列, 即 2152x、2122x 和 UCC53 系列。 有关更多详细信息, 请参阅 TI.com 上的 其他参考设计。 在这个培训系列中, 我们将介绍 栅极驱动器应用以及 低侧栅极驱动器、 高侧/低侧栅极 驱动器及 隔离式栅极驱动器的基本知识。 我们会深入 讨论并利用 TI 参考设计 帮助您了解栅极 驱动器的设计 注意事项,还将 介绍相应的关键波形。 栅极驱动器的 应用非常广泛, 我在这里举几个例子, 比如便携式设备的 电池管理系统、直流电源 适配器、服务器/电信/UPS、 电动汽车充电器 以及电机驱动器和 D 类音频。 此外还包括厨房、 可再生能源和 固态照明领域中的应用。 总而言之, 栅极驱动器 无处不在,用于实现 高效的电源转换。 我们来看看服务器/电信设备的 典型电源 [听不清], 它的前端与公用电网连接, 并进行功率因数 校正,建立 400 伏直流 总线,后跟隔离式直流 /直流转换器和 [听不清] 电平砖型总线转换器 以及负载点。 在示例电路中,我 挑选了两个通道, 交错升压用于 PFC,IOC 用于 隔离直流/直流转换器, 全桥用于 总线转换器。 总共有大约 10 到 20 个开关, 用于几百瓦的简单 前端转换器。 利用常用的图腾柱 PFC,您可以期待 通过更多有源器件 实现更佳的性能。 重要的是,每个开关 都需要栅极驱动器。 单通道或双通道 低侧栅极驱动器、高侧 和低侧栅极驱动器 (用于高桥), 既可以是 100 伏, 用于 48 伏总线, 也可以是 600 伏,用于 400 伏总线。 对于隔离栅,可以 根据系统安全要求 使用单通道或双通道 隔离式栅极驱动器。 对于双向电动 汽车充电器, 所有高压开关 和电机会 驱动电动汽车 以及由电池供电的工具。 高侧和低侧半桥 驱动器更为流行。 再说一次,如果控制器 位于不同的接地 参考,则 应使用单通道 或双通道隔离式 栅极驱动器。 现代电力电子装置 以开关模式 电源转换为主。 常用的器件,包括 MOSFET、IGBT 以及 碳化硅和氮化镓 等新技术, 都会使用高 开关频率。 栅极端子会控制 MOSFET 和 IGBT 的导通和关断。 要导通通常关断 的器件, 需要施加一个高于 此阈值的器件电压。 要将其关断, 您可以将栅极 下拉至 0,或者使用 负电压关断。 栅极是一个电容输入, 具有高阻抗以及 栅极至漏极 (即 CGD)和栅极 至栅源 (即 CGX)寄生电容。 这里展示了一些 常用的功率半导体, 包括碳化硅 IGBT、碳化硅 MOSFET 和氮化镓器件。 它们是不同的。 对于硅 MOSFET,在将其 驱动至高电压时, 通常 为 10 伏至 15 伏。 对于低压 MOSFET,它可以 使用 5 伏至 7 伏的 电压驱动。 IGBT 可能具有更高的 阈值,也会被驱动至 [听不清] 以上, 通常使用的是 15 伏的驱动电压。 碳化硅 MOSFET 稍微 有所不同, 在器件完全导通时, 某些器件可能需要 更高的电压。 需要使用 20 伏的电压 使其完全导通。 对于 IGBT 和 碳化硅, 在严苛的条件下,您可能需要使用 负电压来关断器件, 以确保噪声不会 意外地使器件 导通。 对于氮化镓 器件,此处的 示例展示了对于 采用增强模式的 GaN 器件,完全 导通电压 (例如 5 伏) 与绝对最大 电压(大约为 6 至 7 伏) 之间非常小的裕量。 所以,当我们驱动 不同的开关时, 需要谨慎 选择栅极驱动器, 在设计栅极驱动器 电路时 也是如此。 例如,在服务器和 电信电源应用中, 低侧栅极驱动器 可用于驱动 PFC 级 中的有源开关。 也可以用于 为总线转换器级 驱动同步整流, 因为电源开关 都是接地基准开关。 低侧驱动器能够 以分立的方式 实现,其中采用大量的 低电压晶体管,用于 电平转换器和 图腾柱 [听不清] 级。 由于大量的 分立器件、 组件尺寸、PCB 布局 以及非音频封装 和 PCB 迹线引入的 寄生效应,缺点 是 [听不清]。 所有这些分立器件 可以轻松为智能芯片 集成可靠性保护 功能优化以及 驱动器性能,例如 峰值驱动电流、 极小的 传播延迟、 更好的脉宽失真度 和极小的 [听不清] 电流消耗。 对于低侧栅极 驱动器,您可以 选择单通道 和双通道。 单通道和 双通道都是同相输入。 如左下角的 示例中所示, 器件具有两个 输入引脚,可以 分别连接两个输入, 因此对同相和反相 输入来说是通用的。 此外,可以 拆分输出引脚, 用于编程 不同的导通和关断, 因此在需要加快关断速度时 可以减少所需的外部组件。 与上一页中 介绍的 低侧驱动器类似, 半桥配置中的低侧 栅极驱动器 相对简单、直观。 输入和输出 具有传播延迟。 由于高侧 驱动器 不以接地端为基准, 需要使用电平 [听不清] 电路 来连接 接地基准输入。 要为高侧驱动器 供电,最常用的 方法是使用自举 配置,在底部 FET 导通时为自举 电容器充电。 如幻灯片中所示,您具有 以接地端为基准的输入。 但输出电压 以 100 伏至 700 伏的 开关模式为基准。 HO 与 HS 之间的差值 是高侧栅极驱动器 电压,它通常是 BDD 减去自举二极管的 满量程压降。 某些应用甚至集成了 自举二极管,从而方便 客户使用。 利用输入滤波器 和分离开/关, 它通常展示了 用于高侧和 低侧驱动器的 全功能电路。 下面是前面页面中讨论的 关键规格的 简短总结。 我们提到的 用于驱动各种 FET 的 欠压锁定和 VDD 事件最大值, 对于增强模式 GaN, 事件最大值可以低至 7 伏, 对于碳化硅,事件 最大值可以高达 35 伏。 为了满足不同的 导通和关断 要求,峰值拉电流 和灌电流可以是 对称的,也可以 不对称。 多种输入逻辑、 TTL 和 CMOS 输入 允许从控制器输入, 控制器的电压通常 低于 3.3 伏。 CMOS 输入 要求 50% 以上的 VDD 才能导通 器件,这可带来 更强的抗噪能力。 但它可能需要为 TSP 或 FPGA 控制器配备一个缓冲器。 采用自举配置 的高侧和低侧 栅极驱动器 具有一个 电平转换器, 总线电压为 48 伏时, 转换器最高电压为 100 伏, 总线电压为 400 伏时, 转换器最高电压为 700 伏。 动态参数 包括导通和 关断传播延迟、 上升时间 和下降时间、 延迟匹配 以及最小导通和关断脉冲。 所有这些动态 参数都很重要—— 瞬态响应、 开关损耗和 高频运行。 此外,封装 也很重要。 TI 支持 典型 SOIC 封装, 也支持 2 x 2 的 小型封装。 安全合规性也是 一个重要因素, 因为电源可能会 与公用电网连接 安全操作员也会接触到它。 对于次级侧 控制架构, 不仅应在通常是 电源变压器的 功率级中实现 隔离,还应在控制器 和驱动电路中 实现隔离。 这里列出了 IEC 标准, 增强型隔离 需要 3kV 以上、 最高 5kV 的隔离电压。 那么,我们应该如何 在栅极驱动器上 实现此隔离呢? 栅极驱动器变压器 是可实现此隔离的 一种传统、常用的方法。 在顶部开关栅极 驱动的示例中, 低侧栅极驱动器 利用补偿电路 (包括 C4、C6 和 D1、D2) 提供驱动信号 放大器和栅极 驱动器变压器输入。 栅极驱动器变压器 不但会提供 信号,还会提供 从输入至输出的电源隔离。 这种配置的缺点是, 不仅需要使用 两个庞大的栅极 驱动器变压器,还需要具备 波段瞬变性能, 以支持脉宽 失真控制策略。 这里我们来比较一下 两种常用的方法, 栅极驱动变压器作为 A 类型,数字式振荡器 加高侧和低侧 驱动器作为 B 类型。 比较这两种解决方案。 从传播延迟的角度而言, 栅极驱动变压器表现 出色,它还传输 信号和电源。 B 类型具有 不确定的 更大传播延迟,需要 用于次级复位的电源。 不过,为了具有 干净的驱动信号, A 类型需要 大量的辅助电路, 并要求相对大的 输入和输出电容和漏电感, 因此,预计会 产生更大的过冲。 还要考虑尺寸, 这里有一个示例。 对于增强型 隔离下的尺寸比较, 此仅考虑关键参数, 其中包含 PCB 面积 和体积。 B 类型可以节省 几乎一半的 PCB [听不清] 尺寸 空间,由于变压器的 尺寸尴尬,它能够 节省多得多的 体积。 另一种类型的 驱动器在一个 被称为 ISO 驱动器的 芯片中集成了隔离器 和驱动器,这个芯片具有超过 每纳秒 100 伏的 CMTI 和 5kV 的 增强型隔离。 关系。传播延迟 仅为 19 纳秒, 脉宽失真 小于 5 纳秒。 重要的是,尺寸仅为 B 解决方案的一半, 与 A 类型相比可以节省 75% 以上的尺寸。 UCC21520 系列栅极 驱动器是业界最快的 5.7kV 隔离式双通道 栅极驱动器。 它还在 TI 的栅极驱动器 产品线中引进了 一个新的隔离系列。 集成式组件(包括 高级保护功能 和经过优化的 开关性能) 使得这款驱动器 能够用作 低侧栅极驱动器、高侧栅极驱动器、 低侧栅极驱动器上的 高侧栅极驱动器或者半桥栅极驱动器。 除了这些优势以外, 我们将讨论 具有 6A 和 4A 灌电流 和拉电流峰值的 栅极驱动器变压器,并将其 与 UCC21520 系列 进行比较。 它还支持 3 伏至 18 伏的 宽输入电压范围, 同时支持 6.5 伏至最高 30 伏的 宽输出电压 范围。 它还具有支持重叠和互锁 功能的可编程延迟 以及 0 纳秒至 5 微秒的 死区时间。 输出利用有源下拉 电路实现了失效防护。 此外,还提供了三个 欠压锁定选项—— 5 伏、8 伏和 12 伏, 用于驱动 各种 MOSFET、IGBT 和碳化硅 MOSFET。 好了,我们介绍了 所有基础 知识,看起来 一点儿也不难。 它就是一个驱动器而已, 有一个输入, 有一个输出。 不过,让我们保持 一颗好奇心,来看看 它对栅极驱动器 性能的系统级 影响,例如寄生效应、 软硬开关差异、 非线性输出电容和 CMTI、dv/dt、di/dt 以及非音频 PCB 布局。 我们来更深入地 探讨一下。 我要向您展示 驱动器在转换器 效率和可靠性方面发挥的关键作用。 就寄生效应而言, 结电容、PCB 迹线 和 [听不清] 电感以及 电阻都会产生 寄生 效应。 因此,导通 和关断 会稍微 复杂一些。 对于碳化硅 MOSFET 和硅 MOSFET,还有 寄生二极管,它也 被视为会产生 寄生效应。 在分段线性 图示中,导通 过程可以分为 三个阶段。 第一个阶段是 栅极驱动器 电压、路径阈值 和通道电流增大。 使用红线突出 显示的等效 电路表明 CGS 在这个 阶段处于主导地位。 在第二阶段, 对 CGT 充电 并使 VDS 电压降低。 第三阶段是 通过对 CGD 和 CGS 充电并进一步 降低 [? RDSN ?],来进一步增大栅极电压。 重叠 VDS 和 ID 会产生开关损耗。 具有最短 T1 至 T3 阶段的更强驱动器 会导致开关损耗减小。 关断条件与 导通条件类似。 现在我们在半桥 配置中放置两个 器件,从而让情况 变得更复杂一点。 在硬开关 应用中, 会发生二极管 反向恢复。 左上角显示了 关键波形。 这个反向恢复将 反映在顶部开关上, 通常会产生更多的 导通损耗。 对于硅 MOSFET 的 体二极管和 IGBT 的 反并联二极管, 有两种预期结果, 您可以 看到由反向恢复 产生的大量浪涌电流。 对于硅 MOSFET, 过冲可能 是正常 开关电流 的 5 倍以上,IGBT 相对较小。 主要原因在于 硅 MOSFET 的体二极管 是寄生二极管, 未经过全面优化, 而 IGBT 的 紧凑二极管 可以是超级快速 或软恢复二极管。 反向恢复会增大损耗, 导致电流电压 过冲和 di/dt 增大。 还会导致栅极 振荡,与共源电感、 [听不清] 和栅极 驱动信号耦合的 di/dt 丢失,并减慢 开关切换速度。 减慢这个速度的 方法之一是增加一个 二极管或使用隔离输出 栅极驱动器,以增大导通电阻。 您可以看到, 如果增大 RG, 峰值反向恢复 时间会缩短。 但这样的改善 仍然非常有限。 前一部分中 讨论的反向 恢复对于优化系统 效率和可靠性而言 确实是一个难题。 要进一步消除 该问题,软开关 正是解决之道。 与临界模式 图腾柱 PFC 和 IOC 转换器一样, 它们都会在 VDS 电压降至 0 后 导通器件。 对于软开关, 前面提到的 三个阶段现在 只剩下一个阶段。 没有中间充电过程。 在输出电容完全 放电后导通器件, 器件通道电流 由外部电路决定, 而不是由寄生效应决定。 与硬开关相比, di/dt 通常 非常低, 因此不会出现重叠。 不存在导通损耗。 由于栅极驱动器损耗 机制也会改变, 因此对于硬开关,假设 栅极驱动器电压 为 10 伏,阴影区域、 打开和关断区域 是栅极驱动器电路 中的总损耗。 每个周期的总能量 是总面积 Qg 乘以 10 伏 VGS。 对于软开关,由于 没有中间充电过程, 因此红色实线 表示导通轨道。 关断与硬 开关类似。 与硬开关栅极 驱动器损耗 相比,软开关的 损耗更小。 软开关可以消除 此导通损耗。 不过,关断 也是硬开关。 与快速模式 电流传导 类似,关断 电流加倍。 如果使用弱 驱动器来驱动 FET,那么开关 损耗肯定会增加。 这意味着驱动器具有 更低的灌电流能力。 在使用强大的栅极 驱动器时,您几乎 不会看到中间平坦区域, 并且重叠时段也会 最小化。 重要的是, 开关行为 不受栅极 电流控制, 而是受输出电容和 负载电流控制。 考虑高度 非线性电容, 右上角显示了 分段线性开关 波形。 初始阶段非常低的 dv/dt 会成为一个电容器, 低电压 非常大, 为 5 纳法、0 伏。 随后非常高的 dv/dt 和高电压 导致进一步 最小化的重叠面积。 此处是一个关断 超结 MOSFET 的 实验示例。 将波形放大,可以 看到栅极驱动器非常 干净,具有很短的 中间平坦时间。 VDS 以非常缓慢的速度 增大并且及早关断。 您可以看到,比例 仅为每分段 5 伏, 然后升高。 所有开关电压 和电流 在 VGS 完全关断 之后发生变化, 这意味着开关行为 不是受栅极驱动器控制, 而是受输出电容和负载电流控制。 尽管使用强大的栅极 驱动器时的重叠面积 已降至最低,但它仍然存在。 如果我们测量它, 肯定会看到重叠。 不过,这是真正的损耗吗? 让我们看一看 常用 IOC 电路的 关断机制, 并考虑到 每个器件都包含 一个通道、体二极管和一个 CDS。 在第一阶段, 底部 FET 导通, 电流流过 通道。 在第二阶段,通道 关断,通道电流 减小,剩余的电流 会对两个开关的 输出电容充电 和放电。 由于相对大的 电感负载, 开关转换期间的 负载电流保持 [听不清]。 在第三阶段,通道将关断。 所有负载电流用于 继续对输出电容充电和 放电。 在最后一个阶段,会实现 [? ZVS ?],电流会 流过 体二极管。 实际损耗仅在 第二阶段发生, 在这个阶段中,通道 电流和电压发生 重叠。 第三阶段只会对 输出电容充电和放电。 我们 知道,所有输出电容 能量将在软开关期间的 下一个周期中恢复。 具有更小的损耗 和关断是很好的。 不过,dv/dt 和 di/dt 取决于负载, 可能在非常重的负载下 生成高 dv/dt 和 di/dt。 对于开关节点 中的高 dv/dt, 其行为确实是 退出寄生电容的 噪声源,寄生电容 包括 电平转换器电容、 自举二极管或结电容。 在通过这个电容器 进行耦合时, 会向初级侧接地 基准注入噪声。 如果您丢失了干净的 接地,那么栅极驱动器可能会 出现故障。 在这个实验中, 存在波形输入, 但缺少输出过程。 15 安电流 将关断,左侧 图表显示了 氮化镓和 超结 MOSFET 的 dv/dt 以及栅极驱动器电阻。 正如您看到的, MOSFET 的 dv/dt 可以达到每 纳秒 50 伏以上。 氮化镓 甚至更高, 超过每纳秒 150 伏。 di/dt 具有 类似的趋势。 一种解决方案是为低侧 栅极驱动器添加电平 转换器,尝试分隔 电源接地和逻辑接地。 此外,在采用额外旁通 电容器的情况下, 通过增大自举 电容电阻、 增加充电回路以及增大 电感,将环路最小化 而且 dv/dt 噪声 将流过不同的 路径。 因此,将有更少的 噪声流过初级侧。 讨论了 dv/dt 之后, 我们来看一看 di/dt。 它与寄生 电感相关。 不幸的是, 寄生效应无处不在。 当 di/dt 较高时, 不但会减慢驱动器的速度, 还会导致开关 节点中发生 严重漏电。 例如,当关断 顶部开关时, 底部分支将具有 正 di/dt, 实际电路中会 同时存在寄生电感、[? HSP ?] 和过冲 漏电。 这个过冲会导致 驱动器故障、 后二极管过流以及 VHP 减去 VHS 之后过度充电。 为了提高 驱动器的稳健性, 新的 27714 栅极 驱动器可支持 负 70 伏、100 纳秒 和负 30 伏、 200 纳秒。 TIDA-01159 是一种紧凑、 易于评估的 参考设计,适用于 额定驱动功率级为 1 伏至 690 伏的 UCC21520。 这种设计适用于 所有具有半桥功率级 的设备。 板中内置了简单的 低成本隔离式电源, 用于驱动高侧开关。 这种设计演示了 如何并能够帮助客户 评估 UCC21520 栅极 驱动器众多 功能的性能, 栅极驱动器具有 5kV 隔离电压下的 高驱动力仪表、 适用于高 CMTI 环境 的稳健器件以及 采用碳化硅 MOSFET 的器件的高频 运行能力。 这种解决方案提供了 简单易用的 [听不清] 板,用于比较 采用传统电源 变压器的解决方案在 驱动半桥功率级 方面的性能。 与以前的设计 TIDA-01160 以及 UCC53 系列 栅极驱动器的其他 设计参考类似。 这种设计适用于 需要使用单个 隔离式栅极 驱动器来驱动 IGBT 或碳化硅 MOSFET 的设备。 关键终端设备包括 单相或三相 UPS、直流充电电源 和 [听不清] 系统。 板中内置了低成本的 隔离式电源, 用于驱动具有 负电压 [听不清] 的高侧 开关。 总的来说,我们介绍了 栅极驱动基础知识, 并介绍了 低侧、高侧和低侧 以及隔离式栅极驱动器。 我们还介绍了 寄生效应及其对 软开关和硬开关的影响、 具有强大栅极 驱动器的非线性输出电容、 CMTI、dv/dt 和 di/dt 以及如何隔离 dv/dt 产生的本底噪声。 有关更多信息,请 参阅 TIDA 参考设计。 非常感谢 您的观看。 503

大家好!

我叫张伟(音译)。

是 TI 的系统 应用工程师。

本次培训服务 将探讨

专为 UPS、电信 和服务器等

各种应用中的 MOSFET、IGBT 和

宽带隙器件(例如 碳化硅和氮化镓)

设计的高压栅极驱动器。

本次培训将 涵盖哪些内容?

我们将介绍栅极 驱动器应用,

并说明低侧 驱动器、高侧和

低侧驱动器以及 隔离式栅极驱动器。

我们还将深入 探讨栅极驱动器的

设计注意事项,包括 寄生效应、硬软开关、

高 dv/dt 和 di/dt 以及 隔离式栅极驱动器注意事项,

以介绍如何最大 限度地提高栅极

驱动器的性能。

本演示所使用的 器件包括 UCC2751、

52 和 x24 低侧 驱动器

以及 600 伏 驱动器,即 2771x。

此外,还包括隔离式栅极 驱动器系列,

即 2152x、2122x 和 UCC53 系列。

有关更多详细信息, 请参阅 TI.com 上的

其他参考设计。

在这个培训系列中, 我们将介绍

栅极驱动器应用以及 低侧栅极驱动器、

高侧/低侧栅极 驱动器及

隔离式栅极驱动器的基本知识。

我们会深入 讨论并利用

TI 参考设计 帮助您了解栅极

驱动器的设计 注意事项,还将

介绍相应的关键波形。

栅极驱动器的 应用非常广泛,

我在这里举几个例子, 比如便携式设备的

电池管理系统、直流电源 适配器、服务器/电信/UPS、

电动汽车充电器 以及电机驱动器和 D 类音频。

此外还包括厨房、 可再生能源和

固态照明领域中的应用。

总而言之, 栅极驱动器

无处不在,用于实现 高效的电源转换。

我们来看看服务器/电信设备的 典型电源 [听不清],

它的前端与公用电网连接, 并进行功率因数

校正,建立 400 伏直流 总线,后跟隔离式直流

/直流转换器和 [听不清] 电平砖型总线转换器

以及负载点。

在示例电路中,我 挑选了两个通道,

交错升压用于 PFC,IOC 用于 隔离直流/直流转换器,

全桥用于 总线转换器。

总共有大约 10 到 20 个开关,

用于几百瓦的简单 前端转换器。

利用常用的图腾柱 PFC,您可以期待

通过更多有源器件 实现更佳的性能。

重要的是,每个开关 都需要栅极驱动器。

单通道或双通道 低侧栅极驱动器、高侧

和低侧栅极驱动器 (用于高桥),

既可以是 100 伏, 用于 48 伏总线,

也可以是 600 伏,用于 400 伏总线。

对于隔离栅,可以 根据系统安全要求

使用单通道或双通道 隔离式栅极驱动器。

对于双向电动 汽车充电器,

所有高压开关 和电机会

驱动电动汽车 以及由电池供电的工具。

高侧和低侧半桥 驱动器更为流行。

再说一次,如果控制器 位于不同的接地

参考,则 应使用单通道

或双通道隔离式 栅极驱动器。

现代电力电子装置 以开关模式

电源转换为主。

常用的器件,包括 MOSFET、IGBT 以及

碳化硅和氮化镓 等新技术,

都会使用高 开关频率。

栅极端子会控制 MOSFET 和 IGBT 的导通和关断。

要导通通常关断 的器件,

需要施加一个高于 此阈值的器件电压。

要将其关断, 您可以将栅极

下拉至 0,或者使用 负电压关断。

栅极是一个电容输入, 具有高阻抗以及

栅极至漏极 (即 CGD)和栅极

至栅源 (即 CGX)寄生电容。

这里展示了一些 常用的功率半导体,

包括碳化硅 IGBT、碳化硅

MOSFET 和氮化镓器件。

它们是不同的。

对于硅 MOSFET,在将其 驱动至高电压时,

通常 为

10 伏至 15 伏。

对于低压 MOSFET,它可以 使用 5 伏至 7 伏的

电压驱动。

IGBT 可能具有更高的 阈值,也会被驱动至

[听不清] 以上, 通常使用的是

15 伏的驱动电压。

碳化硅 MOSFET 稍微 有所不同,

在器件完全导通时, 某些器件可能需要

更高的电压。

需要使用 20 伏的电压 使其完全导通。

对于 IGBT 和 碳化硅,

在严苛的条件下,您可能需要使用 负电压来关断器件,

以确保噪声不会 意外地使器件

导通。

对于氮化镓 器件,此处的

示例展示了对于 采用增强模式的

GaN 器件,完全 导通电压

(例如 5 伏) 与绝对最大

电压(大约为 6 至 7 伏)

之间非常小的裕量。

所以,当我们驱动 不同的开关时,

需要谨慎 选择栅极驱动器,

在设计栅极驱动器 电路时

也是如此。

例如,在服务器和 电信电源应用中,

低侧栅极驱动器 可用于驱动 PFC 级

中的有源开关。

也可以用于 为总线转换器级

驱动同步整流, 因为电源开关

都是接地基准开关。

低侧驱动器能够 以分立的方式

实现,其中采用大量的 低电压晶体管,用于

电平转换器和 图腾柱

[听不清] 级。

由于大量的 分立器件、

组件尺寸、PCB 布局 以及非音频封装

和 PCB 迹线引入的 寄生效应,缺点

是 [听不清]。

所有这些分立器件 可以轻松为智能芯片

集成可靠性保护 功能优化以及

驱动器性能,例如 峰值驱动电流、

极小的 传播延迟、

更好的脉宽失真度 和极小的 [听不清]

电流消耗。

对于低侧栅极 驱动器,您可以

选择单通道 和双通道。

单通道和 双通道都是同相输入。

如左下角的 示例中所示,

器件具有两个 输入引脚,可以

分别连接两个输入, 因此对同相和反相

输入来说是通用的。

此外,可以 拆分输出引脚,

用于编程 不同的导通和关断,

因此在需要加快关断速度时 可以减少所需的外部组件。

与上一页中 介绍的

低侧驱动器类似, 半桥配置中的低侧

栅极驱动器 相对简单、直观。

输入和输出 具有传播延迟。

由于高侧 驱动器

不以接地端为基准, 需要使用电平 [听不清] 电路

来连接 接地基准输入。

要为高侧驱动器 供电,最常用的

方法是使用自举 配置,在底部 FET

导通时为自举 电容器充电。

如幻灯片中所示,您具有 以接地端为基准的输入。

但输出电压 以 100 伏至 700 伏的

开关模式为基准。

HO 与 HS 之间的差值 是高侧栅极驱动器

电压,它通常是 BDD 减去自举二极管的

满量程压降。

某些应用甚至集成了 自举二极管,从而方便

客户使用。

利用输入滤波器 和分离开/关,

它通常展示了 用于高侧和

低侧驱动器的 全功能电路。

下面是前面页面中讨论的 关键规格的

简短总结。

我们提到的 用于驱动各种 FET 的

欠压锁定和 VDD 事件最大值,

对于增强模式 GaN, 事件最大值可以低至 7 伏,

对于碳化硅,事件 最大值可以高达 35 伏。

为了满足不同的 导通和关断

要求,峰值拉电流 和灌电流可以是

对称的,也可以 不对称。

多种输入逻辑、 TTL 和 CMOS 输入

允许从控制器输入, 控制器的电压通常

低于 3.3 伏。

CMOS 输入 要求 50% 以上的

VDD 才能导通 器件,这可带来

更强的抗噪能力。

但它可能需要为 TSP 或 FPGA 控制器配备一个缓冲器。

采用自举配置 的高侧和低侧

栅极驱动器 具有一个

电平转换器, 总线电压为 48 伏时,

转换器最高电压为 100 伏, 总线电压为 400 伏时,

转换器最高电压为 700 伏。

动态参数 包括导通和

关断传播延迟、 上升时间

和下降时间、 延迟匹配

以及最小导通和关断脉冲。

所有这些动态 参数都很重要——

瞬态响应、 开关损耗和

高频运行。

此外,封装 也很重要。

TI 支持 典型 SOIC 封装,

也支持 2 x 2 的 小型封装。

安全合规性也是 一个重要因素,

因为电源可能会 与公用电网连接

安全操作员也会接触到它。

对于次级侧 控制架构,

不仅应在通常是 电源变压器的

功率级中实现 隔离,还应在控制器

和驱动电路中 实现隔离。

这里列出了 IEC 标准, 增强型隔离

需要 3kV 以上、 最高 5kV 的隔离电压。

那么,我们应该如何 在栅极驱动器上

实现此隔离呢?

栅极驱动器变压器 是可实现此隔离的

一种传统、常用的方法。

在顶部开关栅极 驱动的示例中,

低侧栅极驱动器 利用补偿电路

(包括 C4、C6 和 D1、D2) 提供驱动信号

放大器和栅极 驱动器变压器输入。

栅极驱动器变压器 不但会提供

信号,还会提供 从输入至输出的电源隔离。

这种配置的缺点是, 不仅需要使用

两个庞大的栅极 驱动器变压器,还需要具备

波段瞬变性能, 以支持脉宽

失真控制策略。

这里我们来比较一下 两种常用的方法,

栅极驱动变压器作为 A 类型,数字式振荡器

加高侧和低侧 驱动器作为 B 类型。

比较这两种解决方案。

从传播延迟的角度而言, 栅极驱动变压器表现

出色,它还传输 信号和电源。

B 类型具有 不确定的

更大传播延迟,需要 用于次级复位的电源。

不过,为了具有 干净的驱动信号,

A 类型需要 大量的辅助电路,

并要求相对大的 输入和输出电容和漏电感,

因此,预计会 产生更大的过冲。

还要考虑尺寸, 这里有一个示例。

对于增强型 隔离下的尺寸比较,

此仅考虑关键参数, 其中包含

PCB 面积 和体积。

B 类型可以节省 几乎一半的 PCB [听不清] 尺寸

空间,由于变压器的 尺寸尴尬,它能够

节省多得多的 体积。

另一种类型的 驱动器在一个

被称为 ISO 驱动器的 芯片中集成了隔离器

和驱动器,这个芯片具有超过 每纳秒 100 伏的 CMTI 和 5kV 的

增强型隔离。

关系。传播延迟 仅为 19 纳秒,

脉宽失真 小于 5 纳秒。

重要的是,尺寸仅为 B 解决方案的一半,

与 A 类型相比可以节省 75% 以上的尺寸。

UCC21520 系列栅极 驱动器是业界最快的

5.7kV 隔离式双通道 栅极驱动器。

它还在 TI 的栅极驱动器 产品线中引进了

一个新的隔离系列。

集成式组件(包括 高级保护功能

和经过优化的 开关性能)

使得这款驱动器 能够用作

低侧栅极驱动器、高侧栅极驱动器、 低侧栅极驱动器上的

高侧栅极驱动器或者半桥栅极驱动器。

除了这些优势以外, 我们将讨论

具有 6A 和 4A 灌电流 和拉电流峰值的

栅极驱动器变压器,并将其 与 UCC21520 系列

进行比较。

它还支持 3 伏至 18 伏的 宽输入电压范围,

同时支持 6.5 伏至最高 30 伏的 宽输出电压

范围。

它还具有支持重叠和互锁 功能的可编程延迟

以及 0 纳秒至 5 微秒的

死区时间。

输出利用有源下拉 电路实现了失效防护。

此外,还提供了三个 欠压锁定选项——

5 伏、8 伏和 12 伏, 用于驱动

各种 MOSFET、IGBT 和碳化硅 MOSFET。

好了,我们介绍了 所有基础

知识,看起来 一点儿也不难。

它就是一个驱动器而已,

有一个输入,

有一个输出。

不过,让我们保持 一颗好奇心,来看看

它对栅极驱动器 性能的系统级

影响,例如寄生效应、 软硬开关差异、

非线性输出电容和 CMTI、dv/dt、di/dt

以及非音频 PCB 布局。

我们来更深入地 探讨一下。

我要向您展示 驱动器在转换器

效率和可靠性方面发挥的关键作用。

就寄生效应而言, 结电容、PCB 迹线

和 [听不清] 电感以及 电阻都会产生

寄生 效应。

因此,导通 和关断

会稍微 复杂一些。

对于碳化硅 MOSFET 和硅 MOSFET,还有

寄生二极管,它也 被视为会产生

寄生效应。

在分段线性 图示中,导通

过程可以分为 三个阶段。

第一个阶段是 栅极驱动器

电压、路径阈值 和通道电流增大。

使用红线突出 显示的等效

电路表明 CGS 在这个 阶段处于主导地位。

在第二阶段, 对 CGT 充电

并使 VDS 电压降低。

第三阶段是 通过对 CGD 和

CGS 充电并进一步 降低 [? RDSN ?],来进一步增大栅极电压。

重叠 VDS 和 ID 会产生开关损耗。

具有最短 T1 至 T3 阶段的更强驱动器

会导致开关损耗减小。

关断条件与 导通条件类似。

现在我们在半桥 配置中放置两个

器件,从而让情况 变得更复杂一点。

在硬开关 应用中,

会发生二极管 反向恢复。

左上角显示了 关键波形。

这个反向恢复将 反映在顶部开关上,

通常会产生更多的 导通损耗。

对于硅 MOSFET 的 体二极管和 IGBT 的

反并联二极管, 有两种预期结果,

您可以 看到由反向恢复

产生的大量浪涌电流。

对于硅 MOSFET, 过冲可能

是正常 开关电流

的 5 倍以上,IGBT 相对较小。

主要原因在于 硅 MOSFET 的体二极管

是寄生二极管, 未经过全面优化,

而 IGBT 的 紧凑二极管

可以是超级快速 或软恢复二极管。

反向恢复会增大损耗, 导致电流电压

过冲和 di/dt 增大。

还会导致栅极 振荡,与共源电感、

[听不清] 和栅极 驱动信号耦合的

di/dt 丢失,并减慢 开关切换速度。

减慢这个速度的 方法之一是增加一个

二极管或使用隔离输出 栅极驱动器,以增大导通电阻。

您可以看到, 如果增大 RG,

峰值反向恢复 时间会缩短。

但这样的改善 仍然非常有限。

前一部分中 讨论的反向

恢复对于优化系统 效率和可靠性而言

确实是一个难题。

要进一步消除 该问题,软开关

正是解决之道。

与临界模式 图腾柱 PFC

和 IOC 转换器一样,

它们都会在 VDS 电压降至 0 后

导通器件。

对于软开关, 前面提到的

三个阶段现在 只剩下一个阶段。

没有中间充电过程。

在输出电容完全 放电后导通器件,

器件通道电流 由外部电路决定,

而不是由寄生效应决定。

与硬开关相比, di/dt 通常

非常低, 因此不会出现重叠。

不存在导通损耗。

由于栅极驱动器损耗 机制也会改变,

因此对于硬开关,假设 栅极驱动器电压

为 10 伏,阴影区域、 打开和关断区域

是栅极驱动器电路 中的总损耗。

每个周期的总能量 是总面积 Qg 乘以

10 伏 VGS。

对于软开关,由于 没有中间充电过程,

因此红色实线 表示导通轨道。

关断与硬 开关类似。

与硬开关栅极 驱动器损耗

相比,软开关的 损耗更小。

软开关可以消除 此导通损耗。

不过,关断 也是硬开关。

与快速模式 电流传导

类似,关断 电流加倍。

如果使用弱 驱动器来驱动

FET,那么开关 损耗肯定会增加。

这意味着驱动器具有 更低的灌电流能力。

在使用强大的栅极 驱动器时,您几乎

不会看到中间平坦区域, 并且重叠时段也会

最小化。

重要的是, 开关行为

不受栅极 电流控制,

而是受输出电容和 负载电流控制。

考虑高度 非线性电容,

右上角显示了 分段线性开关

波形。

初始阶段非常低的 dv/dt 会成为一个电容器,

低电压 非常大,

为 5 纳法、0 伏。

随后非常高的 dv/dt 和高电压

导致进一步 最小化的重叠面积。

此处是一个关断 超结 MOSFET 的

实验示例。

将波形放大,可以 看到栅极驱动器非常

干净,具有很短的 中间平坦时间。

VDS 以非常缓慢的速度 增大并且及早关断。

您可以看到,比例 仅为每分段 5 伏,

然后升高。

所有开关电压 和电流

在 VGS 完全关断 之后发生变化,

这意味着开关行为 不是受栅极驱动器控制,

而是受输出电容和负载电流控制。

尽管使用强大的栅极 驱动器时的重叠面积

已降至最低,但它仍然存在。

如果我们测量它, 肯定会看到重叠。

不过,这是真正的损耗吗?

让我们看一看 常用 IOC 电路的

关断机制, 并考虑到

每个器件都包含 一个通道、体二极管和一个 CDS。

在第一阶段, 底部 FET 导通,

电流流过 通道。

在第二阶段,通道 关断,通道电流

减小,剩余的电流 会对两个开关的

输出电容充电 和放电。

由于相对大的 电感负载,

开关转换期间的 负载电流保持

[听不清]。

在第三阶段,通道将关断。

所有负载电流用于 继续对输出电容充电和

放电。

在最后一个阶段,会实现 [? ZVS ?],电流会 流过

体二极管。

实际损耗仅在 第二阶段发生,

在这个阶段中,通道 电流和电压发生

重叠。

第三阶段只会对 输出电容充电和放电。

我们 知道,所有输出电容

能量将在软开关期间的 下一个周期中恢复。

具有更小的损耗 和关断是很好的。

不过,dv/dt 和 di/dt 取决于负载,

可能在非常重的负载下 生成高 dv/dt 和

di/dt。

对于开关节点 中的高 dv/dt,

其行为确实是 退出寄生电容的

噪声源,寄生电容 包括

电平转换器电容、 自举二极管或结电容。

在通过这个电容器 进行耦合时,

会向初级侧接地 基准注入噪声。

如果您丢失了干净的 接地,那么栅极驱动器可能会

出现故障。

在这个实验中, 存在波形输入,

但缺少输出过程。

15 安电流 将关断,左侧

图表显示了 氮化镓和

超结 MOSFET 的 dv/dt 以及栅极驱动器电阻。

正如您看到的, MOSFET 的 dv/dt

可以达到每 纳秒 50 伏以上。

氮化镓 甚至更高,

超过每纳秒 150 伏。

di/dt 具有 类似的趋势。

一种解决方案是为低侧 栅极驱动器添加电平

转换器,尝试分隔 电源接地和逻辑接地。

此外,在采用额外旁通 电容器的情况下,

通过增大自举 电容电阻、

增加充电回路以及增大 电感,将环路最小化

而且 dv/dt 噪声 将流过不同的

路径。

因此,将有更少的 噪声流过初级侧。

讨论了 dv/dt 之后, 我们来看一看 di/dt。

它与寄生 电感相关。

不幸的是, 寄生效应无处不在。

当 di/dt 较高时, 不但会减慢驱动器的速度,

还会导致开关 节点中发生

严重漏电。

例如,当关断 顶部开关时,

底部分支将具有 正 di/dt,

实际电路中会 同时存在寄生电感、[? HSP ?]

和过冲 漏电。

这个过冲会导致 驱动器故障、

后二极管过流以及 VHP 减去 VHS 之后过度充电。

为了提高 驱动器的稳健性,

新的 27714 栅极 驱动器可支持

负 70 伏、100 纳秒 和负 30 伏、

200 纳秒。

TIDA-01159 是一种紧凑、 易于评估的

参考设计,适用于 额定驱动功率级为

1 伏至 690 伏的 UCC21520。

这种设计适用于 所有具有半桥功率级

的设备。

板中内置了简单的 低成本隔离式电源,

用于驱动高侧开关。

这种设计演示了 如何并能够帮助客户

评估 UCC21520 栅极 驱动器众多

功能的性能, 栅极驱动器具有

5kV 隔离电压下的 高驱动力仪表、

适用于高 CMTI 环境 的稳健器件以及

采用碳化硅 MOSFET 的器件的高频

运行能力。

这种解决方案提供了 简单易用的 [听不清]

板,用于比较 采用传统电源

变压器的解决方案在 驱动半桥功率级

方面的性能。

与以前的设计 TIDA-01160 以及 UCC53 系列

栅极驱动器的其他 设计参考类似。

这种设计适用于 需要使用单个

隔离式栅极 驱动器来驱动 IGBT

或碳化硅 MOSFET 的设备。

关键终端设备包括 单相或三相

UPS、直流充电电源 和 [听不清] 系统。

板中内置了低成本的 隔离式电源,

用于驱动具有 负电压 [听不清] 的高侧

开关。

总的来说,我们介绍了 栅极驱动基础知识,

并介绍了 低侧、高侧和低侧

以及隔离式栅极驱动器。

我们还介绍了 寄生效应及其对

软开关和硬开关的影响、 具有强大栅极

驱动器的非线性输出电容、 CMTI、dv/dt 和 di/dt

以及如何隔离 dv/dt 产生的本底噪声。

有关更多信息,请 参阅 TIDA 参考设计。

非常感谢 您的观看。 503

大家好! 我叫张伟(音译)。 是 TI 的系统 应用工程师。 本次培训服务 将探讨 专为 UPS、电信 和服务器等 各种应用中的 MOSFET、IGBT 和 宽带隙器件(例如 碳化硅和氮化镓) 设计的高压栅极驱动器。 本次培训将 涵盖哪些内容? 我们将介绍栅极 驱动器应用, 并说明低侧 驱动器、高侧和 低侧驱动器以及 隔离式栅极驱动器。 我们还将深入 探讨栅极驱动器的 设计注意事项,包括 寄生效应、硬软开关、 高 dv/dt 和 di/dt 以及 隔离式栅极驱动器注意事项, 以介绍如何最大 限度地提高栅极 驱动器的性能。 本演示所使用的 器件包括 UCC2751、 52 和 x24 低侧 驱动器 以及 600 伏 驱动器,即 2771x。 此外,还包括隔离式栅极 驱动器系列, 即 2152x、2122x 和 UCC53 系列。 有关更多详细信息, 请参阅 TI.com 上的 其他参考设计。 在这个培训系列中, 我们将介绍 栅极驱动器应用以及 低侧栅极驱动器、 高侧/低侧栅极 驱动器及 隔离式栅极驱动器的基本知识。 我们会深入 讨论并利用 TI 参考设计 帮助您了解栅极 驱动器的设计 注意事项,还将 介绍相应的关键波形。 栅极驱动器的 应用非常广泛, 我在这里举几个例子, 比如便携式设备的 电池管理系统、直流电源 适配器、服务器/电信/UPS、 电动汽车充电器 以及电机驱动器和 D 类音频。 此外还包括厨房、 可再生能源和 固态照明领域中的应用。 总而言之, 栅极驱动器 无处不在,用于实现 高效的电源转换。 我们来看看服务器/电信设备的 典型电源 [听不清], 它的前端与公用电网连接, 并进行功率因数 校正,建立 400 伏直流 总线,后跟隔离式直流 /直流转换器和 [听不清] 电平砖型总线转换器 以及负载点。 在示例电路中,我 挑选了两个通道, 交错升压用于 PFC,IOC 用于 隔离直流/直流转换器, 全桥用于 总线转换器。 总共有大约 10 到 20 个开关, 用于几百瓦的简单 前端转换器。 利用常用的图腾柱 PFC,您可以期待 通过更多有源器件 实现更佳的性能。 重要的是,每个开关 都需要栅极驱动器。 单通道或双通道 低侧栅极驱动器、高侧 和低侧栅极驱动器 (用于高桥), 既可以是 100 伏, 用于 48 伏总线, 也可以是 600 伏,用于 400 伏总线。 对于隔离栅,可以 根据系统安全要求 使用单通道或双通道 隔离式栅极驱动器。 对于双向电动 汽车充电器, 所有高压开关 和电机会 驱动电动汽车 以及由电池供电的工具。 高侧和低侧半桥 驱动器更为流行。 再说一次,如果控制器 位于不同的接地 参考,则 应使用单通道 或双通道隔离式 栅极驱动器。 现代电力电子装置 以开关模式 电源转换为主。 常用的器件,包括 MOSFET、IGBT 以及 碳化硅和氮化镓 等新技术, 都会使用高 开关频率。 栅极端子会控制 MOSFET 和 IGBT 的导通和关断。 要导通通常关断 的器件, 需要施加一个高于 此阈值的器件电压。 要将其关断, 您可以将栅极 下拉至 0,或者使用 负电压关断。 栅极是一个电容输入, 具有高阻抗以及 栅极至漏极 (即 CGD)和栅极 至栅源 (即 CGX)寄生电容。 这里展示了一些 常用的功率半导体, 包括碳化硅 IGBT、碳化硅 MOSFET 和氮化镓器件。 它们是不同的。 对于硅 MOSFET,在将其 驱动至高电压时, 通常 为 10 伏至 15 伏。 对于低压 MOSFET,它可以 使用 5 伏至 7 伏的 电压驱动。 IGBT 可能具有更高的 阈值,也会被驱动至 [听不清] 以上, 通常使用的是 15 伏的驱动电压。 碳化硅 MOSFET 稍微 有所不同, 在器件完全导通时, 某些器件可能需要 更高的电压。 需要使用 20 伏的电压 使其完全导通。 对于 IGBT 和 碳化硅, 在严苛的条件下,您可能需要使用 负电压来关断器件, 以确保噪声不会 意外地使器件 导通。 对于氮化镓 器件,此处的 示例展示了对于 采用增强模式的 GaN 器件,完全 导通电压 (例如 5 伏) 与绝对最大 电压(大约为 6 至 7 伏) 之间非常小的裕量。 所以,当我们驱动 不同的开关时, 需要谨慎 选择栅极驱动器, 在设计栅极驱动器 电路时 也是如此。 例如,在服务器和 电信电源应用中, 低侧栅极驱动器 可用于驱动 PFC 级 中的有源开关。 也可以用于 为总线转换器级 驱动同步整流, 因为电源开关 都是接地基准开关。 低侧驱动器能够 以分立的方式 实现,其中采用大量的 低电压晶体管,用于 电平转换器和 图腾柱 [听不清] 级。 由于大量的 分立器件、 组件尺寸、PCB 布局 以及非音频封装 和 PCB 迹线引入的 寄生效应,缺点 是 [听不清]。 所有这些分立器件 可以轻松为智能芯片 集成可靠性保护 功能优化以及 驱动器性能,例如 峰值驱动电流、 极小的 传播延迟、 更好的脉宽失真度 和极小的 [听不清] 电流消耗。 对于低侧栅极 驱动器,您可以 选择单通道 和双通道。 单通道和 双通道都是同相输入。 如左下角的 示例中所示, 器件具有两个 输入引脚,可以 分别连接两个输入, 因此对同相和反相 输入来说是通用的。 此外,可以 拆分输出引脚, 用于编程 不同的导通和关断, 因此在需要加快关断速度时 可以减少所需的外部组件。 与上一页中 介绍的 低侧驱动器类似, 半桥配置中的低侧 栅极驱动器 相对简单、直观。 输入和输出 具有传播延迟。 由于高侧 驱动器 不以接地端为基准, 需要使用电平 [听不清] 电路 来连接 接地基准输入。 要为高侧驱动器 供电,最常用的 方法是使用自举 配置,在底部 FET 导通时为自举 电容器充电。 如幻灯片中所示,您具有 以接地端为基准的输入。 但输出电压 以 100 伏至 700 伏的 开关模式为基准。 HO 与 HS 之间的差值 是高侧栅极驱动器 电压,它通常是 BDD 减去自举二极管的 满量程压降。 某些应用甚至集成了 自举二极管,从而方便 客户使用。 利用输入滤波器 和分离开/关, 它通常展示了 用于高侧和 低侧驱动器的 全功能电路。 下面是前面页面中讨论的 关键规格的 简短总结。 我们提到的 用于驱动各种 FET 的 欠压锁定和 VDD 事件最大值, 对于增强模式 GaN, 事件最大值可以低至 7 伏, 对于碳化硅,事件 最大值可以高达 35 伏。 为了满足不同的 导通和关断 要求,峰值拉电流 和灌电流可以是 对称的,也可以 不对称。 多种输入逻辑、 TTL 和 CMOS 输入 允许从控制器输入, 控制器的电压通常 低于 3.3 伏。 CMOS 输入 要求 50% 以上的 VDD 才能导通 器件,这可带来 更强的抗噪能力。 但它可能需要为 TSP 或 FPGA 控制器配备一个缓冲器。 采用自举配置 的高侧和低侧 栅极驱动器 具有一个 电平转换器, 总线电压为 48 伏时, 转换器最高电压为 100 伏, 总线电压为 400 伏时, 转换器最高电压为 700 伏。 动态参数 包括导通和 关断传播延迟、 上升时间 和下降时间、 延迟匹配 以及最小导通和关断脉冲。 所有这些动态 参数都很重要—— 瞬态响应、 开关损耗和 高频运行。 此外,封装 也很重要。 TI 支持 典型 SOIC 封装, 也支持 2 x 2 的 小型封装。 安全合规性也是 一个重要因素, 因为电源可能会 与公用电网连接 安全操作员也会接触到它。 对于次级侧 控制架构, 不仅应在通常是 电源变压器的 功率级中实现 隔离,还应在控制器 和驱动电路中 实现隔离。 这里列出了 IEC 标准, 增强型隔离 需要 3kV 以上、 最高 5kV 的隔离电压。 那么,我们应该如何 在栅极驱动器上 实现此隔离呢? 栅极驱动器变压器 是可实现此隔离的 一种传统、常用的方法。 在顶部开关栅极 驱动的示例中, 低侧栅极驱动器 利用补偿电路 (包括 C4、C6 和 D1、D2) 提供驱动信号 放大器和栅极 驱动器变压器输入。 栅极驱动器变压器 不但会提供 信号,还会提供 从输入至输出的电源隔离。 这种配置的缺点是, 不仅需要使用 两个庞大的栅极 驱动器变压器,还需要具备 波段瞬变性能, 以支持脉宽 失真控制策略。 这里我们来比较一下 两种常用的方法, 栅极驱动变压器作为 A 类型,数字式振荡器 加高侧和低侧 驱动器作为 B 类型。 比较这两种解决方案。 从传播延迟的角度而言, 栅极驱动变压器表现 出色,它还传输 信号和电源。 B 类型具有 不确定的 更大传播延迟,需要 用于次级复位的电源。 不过,为了具有 干净的驱动信号, A 类型需要 大量的辅助电路, 并要求相对大的 输入和输出电容和漏电感, 因此,预计会 产生更大的过冲。 还要考虑尺寸, 这里有一个示例。 对于增强型 隔离下的尺寸比较, 此仅考虑关键参数, 其中包含 PCB 面积 和体积。 B 类型可以节省 几乎一半的 PCB [听不清] 尺寸 空间,由于变压器的 尺寸尴尬,它能够 节省多得多的 体积。 另一种类型的 驱动器在一个 被称为 ISO 驱动器的 芯片中集成了隔离器 和驱动器,这个芯片具有超过 每纳秒 100 伏的 CMTI 和 5kV 的 增强型隔离。 关系。传播延迟 仅为 19 纳秒, 脉宽失真 小于 5 纳秒。 重要的是,尺寸仅为 B 解决方案的一半, 与 A 类型相比可以节省 75% 以上的尺寸。 UCC21520 系列栅极 驱动器是业界最快的 5.7kV 隔离式双通道 栅极驱动器。 它还在 TI 的栅极驱动器 产品线中引进了 一个新的隔离系列。 集成式组件(包括 高级保护功能 和经过优化的 开关性能) 使得这款驱动器 能够用作 低侧栅极驱动器、高侧栅极驱动器、 低侧栅极驱动器上的 高侧栅极驱动器或者半桥栅极驱动器。 除了这些优势以外, 我们将讨论 具有 6A 和 4A 灌电流 和拉电流峰值的 栅极驱动器变压器,并将其 与 UCC21520 系列 进行比较。 它还支持 3 伏至 18 伏的 宽输入电压范围, 同时支持 6.5 伏至最高 30 伏的 宽输出电压 范围。 它还具有支持重叠和互锁 功能的可编程延迟 以及 0 纳秒至 5 微秒的 死区时间。 输出利用有源下拉 电路实现了失效防护。 此外,还提供了三个 欠压锁定选项—— 5 伏、8 伏和 12 伏, 用于驱动 各种 MOSFET、IGBT 和碳化硅 MOSFET。 好了,我们介绍了 所有基础 知识,看起来 一点儿也不难。 它就是一个驱动器而已, 有一个输入, 有一个输出。 不过,让我们保持 一颗好奇心,来看看 它对栅极驱动器 性能的系统级 影响,例如寄生效应、 软硬开关差异、 非线性输出电容和 CMTI、dv/dt、di/dt 以及非音频 PCB 布局。 我们来更深入地 探讨一下。 我要向您展示 驱动器在转换器 效率和可靠性方面发挥的关键作用。 就寄生效应而言, 结电容、PCB 迹线 和 [听不清] 电感以及 电阻都会产生 寄生 效应。 因此,导通 和关断 会稍微 复杂一些。 对于碳化硅 MOSFET 和硅 MOSFET,还有 寄生二极管,它也 被视为会产生 寄生效应。 在分段线性 图示中,导通 过程可以分为 三个阶段。 第一个阶段是 栅极驱动器 电压、路径阈值 和通道电流增大。 使用红线突出 显示的等效 电路表明 CGS 在这个 阶段处于主导地位。 在第二阶段, 对 CGT 充电 并使 VDS 电压降低。 第三阶段是 通过对 CGD 和 CGS 充电并进一步 降低 [? RDSN ?],来进一步增大栅极电压。 重叠 VDS 和 ID 会产生开关损耗。 具有最短 T1 至 T3 阶段的更强驱动器 会导致开关损耗减小。 关断条件与 导通条件类似。 现在我们在半桥 配置中放置两个 器件,从而让情况 变得更复杂一点。 在硬开关 应用中, 会发生二极管 反向恢复。 左上角显示了 关键波形。 这个反向恢复将 反映在顶部开关上, 通常会产生更多的 导通损耗。 对于硅 MOSFET 的 体二极管和 IGBT 的 反并联二极管, 有两种预期结果, 您可以 看到由反向恢复 产生的大量浪涌电流。 对于硅 MOSFET, 过冲可能 是正常 开关电流 的 5 倍以上,IGBT 相对较小。 主要原因在于 硅 MOSFET 的体二极管 是寄生二极管, 未经过全面优化, 而 IGBT 的 紧凑二极管 可以是超级快速 或软恢复二极管。 反向恢复会增大损耗, 导致电流电压 过冲和 di/dt 增大。 还会导致栅极 振荡,与共源电感、 [听不清] 和栅极 驱动信号耦合的 di/dt 丢失,并减慢 开关切换速度。 减慢这个速度的 方法之一是增加一个 二极管或使用隔离输出 栅极驱动器,以增大导通电阻。 您可以看到, 如果增大 RG, 峰值反向恢复 时间会缩短。 但这样的改善 仍然非常有限。 前一部分中 讨论的反向 恢复对于优化系统 效率和可靠性而言 确实是一个难题。 要进一步消除 该问题,软开关 正是解决之道。 与临界模式 图腾柱 PFC 和 IOC 转换器一样, 它们都会在 VDS 电压降至 0 后 导通器件。 对于软开关, 前面提到的 三个阶段现在 只剩下一个阶段。 没有中间充电过程。 在输出电容完全 放电后导通器件, 器件通道电流 由外部电路决定, 而不是由寄生效应决定。 与硬开关相比, di/dt 通常 非常低, 因此不会出现重叠。 不存在导通损耗。 由于栅极驱动器损耗 机制也会改变, 因此对于硬开关,假设 栅极驱动器电压 为 10 伏,阴影区域、 打开和关断区域 是栅极驱动器电路 中的总损耗。 每个周期的总能量 是总面积 Qg 乘以 10 伏 VGS。 对于软开关,由于 没有中间充电过程, 因此红色实线 表示导通轨道。 关断与硬 开关类似。 与硬开关栅极 驱动器损耗 相比,软开关的 损耗更小。 软开关可以消除 此导通损耗。 不过,关断 也是硬开关。 与快速模式 电流传导 类似,关断 电流加倍。 如果使用弱 驱动器来驱动 FET,那么开关 损耗肯定会增加。 这意味着驱动器具有 更低的灌电流能力。 在使用强大的栅极 驱动器时,您几乎 不会看到中间平坦区域, 并且重叠时段也会 最小化。 重要的是, 开关行为 不受栅极 电流控制, 而是受输出电容和 负载电流控制。 考虑高度 非线性电容, 右上角显示了 分段线性开关 波形。 初始阶段非常低的 dv/dt 会成为一个电容器, 低电压 非常大, 为 5 纳法、0 伏。 随后非常高的 dv/dt 和高电压 导致进一步 最小化的重叠面积。 此处是一个关断 超结 MOSFET 的 实验示例。 将波形放大,可以 看到栅极驱动器非常 干净,具有很短的 中间平坦时间。 VDS 以非常缓慢的速度 增大并且及早关断。 您可以看到,比例 仅为每分段 5 伏, 然后升高。 所有开关电压 和电流 在 VGS 完全关断 之后发生变化, 这意味着开关行为 不是受栅极驱动器控制, 而是受输出电容和负载电流控制。 尽管使用强大的栅极 驱动器时的重叠面积 已降至最低,但它仍然存在。 如果我们测量它, 肯定会看到重叠。 不过,这是真正的损耗吗? 让我们看一看 常用 IOC 电路的 关断机制, 并考虑到 每个器件都包含 一个通道、体二极管和一个 CDS。 在第一阶段, 底部 FET 导通, 电流流过 通道。 在第二阶段,通道 关断,通道电流 减小,剩余的电流 会对两个开关的 输出电容充电 和放电。 由于相对大的 电感负载, 开关转换期间的 负载电流保持 [听不清]。 在第三阶段,通道将关断。 所有负载电流用于 继续对输出电容充电和 放电。 在最后一个阶段,会实现 [? ZVS ?],电流会 流过 体二极管。 实际损耗仅在 第二阶段发生, 在这个阶段中,通道 电流和电压发生 重叠。 第三阶段只会对 输出电容充电和放电。 我们 知道,所有输出电容 能量将在软开关期间的 下一个周期中恢复。 具有更小的损耗 和关断是很好的。 不过,dv/dt 和 di/dt 取决于负载, 可能在非常重的负载下 生成高 dv/dt 和 di/dt。 对于开关节点 中的高 dv/dt, 其行为确实是 退出寄生电容的 噪声源,寄生电容 包括 电平转换器电容、 自举二极管或结电容。 在通过这个电容器 进行耦合时, 会向初级侧接地 基准注入噪声。 如果您丢失了干净的 接地,那么栅极驱动器可能会 出现故障。 在这个实验中, 存在波形输入, 但缺少输出过程。 15 安电流 将关断,左侧 图表显示了 氮化镓和 超结 MOSFET 的 dv/dt 以及栅极驱动器电阻。 正如您看到的, MOSFET 的 dv/dt 可以达到每 纳秒 50 伏以上。 氮化镓 甚至更高, 超过每纳秒 150 伏。 di/dt 具有 类似的趋势。 一种解决方案是为低侧 栅极驱动器添加电平 转换器,尝试分隔 电源接地和逻辑接地。 此外,在采用额外旁通 电容器的情况下, 通过增大自举 电容电阻、 增加充电回路以及增大 电感,将环路最小化 而且 dv/dt 噪声 将流过不同的 路径。 因此,将有更少的 噪声流过初级侧。 讨论了 dv/dt 之后, 我们来看一看 di/dt。 它与寄生 电感相关。 不幸的是, 寄生效应无处不在。 当 di/dt 较高时, 不但会减慢驱动器的速度, 还会导致开关 节点中发生 严重漏电。 例如,当关断 顶部开关时, 底部分支将具有 正 di/dt, 实际电路中会 同时存在寄生电感、[? HSP ?] 和过冲 漏电。 这个过冲会导致 驱动器故障、 后二极管过流以及 VHP 减去 VHS 之后过度充电。 为了提高 驱动器的稳健性, 新的 27714 栅极 驱动器可支持 负 70 伏、100 纳秒 和负 30 伏、 200 纳秒。 TIDA-01159 是一种紧凑、 易于评估的 参考设计,适用于 额定驱动功率级为 1 伏至 690 伏的 UCC21520。 这种设计适用于 所有具有半桥功率级 的设备。 板中内置了简单的 低成本隔离式电源, 用于驱动高侧开关。 这种设计演示了 如何并能够帮助客户 评估 UCC21520 栅极 驱动器众多 功能的性能, 栅极驱动器具有 5kV 隔离电压下的 高驱动力仪表、 适用于高 CMTI 环境 的稳健器件以及 采用碳化硅 MOSFET 的器件的高频 运行能力。 这种解决方案提供了 简单易用的 [听不清] 板,用于比较 采用传统电源 变压器的解决方案在 驱动半桥功率级 方面的性能。 与以前的设计 TIDA-01160 以及 UCC53 系列 栅极驱动器的其他 设计参考类似。 这种设计适用于 需要使用单个 隔离式栅极 驱动器来驱动 IGBT 或碳化硅 MOSFET 的设备。 关键终端设备包括 单相或三相 UPS、直流充电电源 和 [听不清] 系统。 板中内置了低成本的 隔离式电源, 用于驱动具有 负电压 [听不清] 的高侧 开关。 总的来说,我们介绍了 栅极驱动基础知识, 并介绍了 低侧、高侧和低侧 以及隔离式栅极驱动器。 我们还介绍了 寄生效应及其对 软开关和硬开关的影响、 具有强大栅极 驱动器的非线性输出电容、 CMTI、dv/dt 和 di/dt 以及如何隔离 dv/dt 产生的本底噪声。 有关更多信息,请 参阅 TIDA 参考设计。 非常感谢 您的观看。 503

大家好!

我叫张伟(音译)。

是 TI 的系统 应用工程师。

本次培训服务 将探讨

专为 UPS、电信 和服务器等

各种应用中的 MOSFET、IGBT 和

宽带隙器件(例如 碳化硅和氮化镓)

设计的高压栅极驱动器。

本次培训将 涵盖哪些内容?

我们将介绍栅极 驱动器应用,

并说明低侧 驱动器、高侧和

低侧驱动器以及 隔离式栅极驱动器。

我们还将深入 探讨栅极驱动器的

设计注意事项,包括 寄生效应、硬软开关、

高 dv/dt 和 di/dt 以及 隔离式栅极驱动器注意事项,

以介绍如何最大 限度地提高栅极

驱动器的性能。

本演示所使用的 器件包括 UCC2751、

52 和 x24 低侧 驱动器

以及 600 伏 驱动器,即 2771x。

此外,还包括隔离式栅极 驱动器系列,

即 2152x、2122x 和 UCC53 系列。

有关更多详细信息, 请参阅 TI.com 上的

其他参考设计。

在这个培训系列中, 我们将介绍

栅极驱动器应用以及 低侧栅极驱动器、

高侧/低侧栅极 驱动器及

隔离式栅极驱动器的基本知识。

我们会深入 讨论并利用

TI 参考设计 帮助您了解栅极

驱动器的设计 注意事项,还将

介绍相应的关键波形。

栅极驱动器的 应用非常广泛,

我在这里举几个例子, 比如便携式设备的

电池管理系统、直流电源 适配器、服务器/电信/UPS、

电动汽车充电器 以及电机驱动器和 D 类音频。

此外还包括厨房、 可再生能源和

固态照明领域中的应用。

总而言之, 栅极驱动器

无处不在,用于实现 高效的电源转换。

我们来看看服务器/电信设备的 典型电源 [听不清],

它的前端与公用电网连接, 并进行功率因数

校正,建立 400 伏直流 总线,后跟隔离式直流

/直流转换器和 [听不清] 电平砖型总线转换器

以及负载点。

在示例电路中,我 挑选了两个通道,

交错升压用于 PFC,IOC 用于 隔离直流/直流转换器,

全桥用于 总线转换器。

总共有大约 10 到 20 个开关,

用于几百瓦的简单 前端转换器。

利用常用的图腾柱 PFC,您可以期待

通过更多有源器件 实现更佳的性能。

重要的是,每个开关 都需要栅极驱动器。

单通道或双通道 低侧栅极驱动器、高侧

和低侧栅极驱动器 (用于高桥),

既可以是 100 伏, 用于 48 伏总线,

也可以是 600 伏,用于 400 伏总线。

对于隔离栅,可以 根据系统安全要求

使用单通道或双通道 隔离式栅极驱动器。

对于双向电动 汽车充电器,

所有高压开关 和电机会

驱动电动汽车 以及由电池供电的工具。

高侧和低侧半桥 驱动器更为流行。

再说一次,如果控制器 位于不同的接地

参考,则 应使用单通道

或双通道隔离式 栅极驱动器。

现代电力电子装置 以开关模式

电源转换为主。

常用的器件,包括 MOSFET、IGBT 以及

碳化硅和氮化镓 等新技术,

都会使用高 开关频率。

栅极端子会控制 MOSFET 和 IGBT 的导通和关断。

要导通通常关断 的器件,

需要施加一个高于 此阈值的器件电压。

要将其关断, 您可以将栅极

下拉至 0,或者使用 负电压关断。

栅极是一个电容输入, 具有高阻抗以及

栅极至漏极 (即 CGD)和栅极

至栅源 (即 CGX)寄生电容。

这里展示了一些 常用的功率半导体,

包括碳化硅 IGBT、碳化硅

MOSFET 和氮化镓器件。

它们是不同的。

对于硅 MOSFET,在将其 驱动至高电压时,

通常 为

10 伏至 15 伏。

对于低压 MOSFET,它可以 使用 5 伏至 7 伏的

电压驱动。

IGBT 可能具有更高的 阈值,也会被驱动至

[听不清] 以上, 通常使用的是

15 伏的驱动电压。

碳化硅 MOSFET 稍微 有所不同,

在器件完全导通时, 某些器件可能需要

更高的电压。

需要使用 20 伏的电压 使其完全导通。

对于 IGBT 和 碳化硅,

在严苛的条件下,您可能需要使用 负电压来关断器件,

以确保噪声不会 意外地使器件

导通。

对于氮化镓 器件,此处的

示例展示了对于 采用增强模式的

GaN 器件,完全 导通电压

(例如 5 伏) 与绝对最大

电压(大约为 6 至 7 伏)

之间非常小的裕量。

所以,当我们驱动 不同的开关时,

需要谨慎 选择栅极驱动器,

在设计栅极驱动器 电路时

也是如此。

例如,在服务器和 电信电源应用中,

低侧栅极驱动器 可用于驱动 PFC 级

中的有源开关。

也可以用于 为总线转换器级

驱动同步整流, 因为电源开关

都是接地基准开关。

低侧驱动器能够 以分立的方式

实现,其中采用大量的 低电压晶体管,用于

电平转换器和 图腾柱

[听不清] 级。

由于大量的 分立器件、

组件尺寸、PCB 布局 以及非音频封装

和 PCB 迹线引入的 寄生效应,缺点

是 [听不清]。

所有这些分立器件 可以轻松为智能芯片

集成可靠性保护 功能优化以及

驱动器性能,例如 峰值驱动电流、

极小的 传播延迟、

更好的脉宽失真度 和极小的 [听不清]

电流消耗。

对于低侧栅极 驱动器,您可以

选择单通道 和双通道。

单通道和 双通道都是同相输入。

如左下角的 示例中所示,

器件具有两个 输入引脚,可以

分别连接两个输入, 因此对同相和反相

输入来说是通用的。

此外,可以 拆分输出引脚,

用于编程 不同的导通和关断,

因此在需要加快关断速度时 可以减少所需的外部组件。

与上一页中 介绍的

低侧驱动器类似, 半桥配置中的低侧

栅极驱动器 相对简单、直观。

输入和输出 具有传播延迟。

由于高侧 驱动器

不以接地端为基准, 需要使用电平 [听不清] 电路

来连接 接地基准输入。

要为高侧驱动器 供电,最常用的

方法是使用自举 配置,在底部 FET

导通时为自举 电容器充电。

如幻灯片中所示,您具有 以接地端为基准的输入。

但输出电压 以 100 伏至 700 伏的

开关模式为基准。

HO 与 HS 之间的差值 是高侧栅极驱动器

电压,它通常是 BDD 减去自举二极管的

满量程压降。

某些应用甚至集成了 自举二极管,从而方便

客户使用。

利用输入滤波器 和分离开/关,

它通常展示了 用于高侧和

低侧驱动器的 全功能电路。

下面是前面页面中讨论的 关键规格的

简短总结。

我们提到的 用于驱动各种 FET 的

欠压锁定和 VDD 事件最大值,

对于增强模式 GaN, 事件最大值可以低至 7 伏,

对于碳化硅,事件 最大值可以高达 35 伏。

为了满足不同的 导通和关断

要求,峰值拉电流 和灌电流可以是

对称的,也可以 不对称。

多种输入逻辑、 TTL 和 CMOS 输入

允许从控制器输入, 控制器的电压通常

低于 3.3 伏。

CMOS 输入 要求 50% 以上的

VDD 才能导通 器件,这可带来

更强的抗噪能力。

但它可能需要为 TSP 或 FPGA 控制器配备一个缓冲器。

采用自举配置 的高侧和低侧

栅极驱动器 具有一个

电平转换器, 总线电压为 48 伏时,

转换器最高电压为 100 伏, 总线电压为 400 伏时,

转换器最高电压为 700 伏。

动态参数 包括导通和

关断传播延迟、 上升时间

和下降时间、 延迟匹配

以及最小导通和关断脉冲。

所有这些动态 参数都很重要——

瞬态响应、 开关损耗和

高频运行。

此外,封装 也很重要。

TI 支持 典型 SOIC 封装,

也支持 2 x 2 的 小型封装。

安全合规性也是 一个重要因素,

因为电源可能会 与公用电网连接

安全操作员也会接触到它。

对于次级侧 控制架构,

不仅应在通常是 电源变压器的

功率级中实现 隔离,还应在控制器

和驱动电路中 实现隔离。

这里列出了 IEC 标准, 增强型隔离

需要 3kV 以上、 最高 5kV 的隔离电压。

那么,我们应该如何 在栅极驱动器上

实现此隔离呢?

栅极驱动器变压器 是可实现此隔离的

一种传统、常用的方法。

在顶部开关栅极 驱动的示例中,

低侧栅极驱动器 利用补偿电路

(包括 C4、C6 和 D1、D2) 提供驱动信号

放大器和栅极 驱动器变压器输入。

栅极驱动器变压器 不但会提供

信号,还会提供 从输入至输出的电源隔离。

这种配置的缺点是, 不仅需要使用

两个庞大的栅极 驱动器变压器,还需要具备

波段瞬变性能, 以支持脉宽

失真控制策略。

这里我们来比较一下 两种常用的方法,

栅极驱动变压器作为 A 类型,数字式振荡器

加高侧和低侧 驱动器作为 B 类型。

比较这两种解决方案。

从传播延迟的角度而言, 栅极驱动变压器表现

出色,它还传输 信号和电源。

B 类型具有 不确定的

更大传播延迟,需要 用于次级复位的电源。

不过,为了具有 干净的驱动信号,

A 类型需要 大量的辅助电路,

并要求相对大的 输入和输出电容和漏电感,

因此,预计会 产生更大的过冲。

还要考虑尺寸, 这里有一个示例。

对于增强型 隔离下的尺寸比较,

此仅考虑关键参数, 其中包含

PCB 面积 和体积。

B 类型可以节省 几乎一半的 PCB [听不清] 尺寸

空间,由于变压器的 尺寸尴尬,它能够

节省多得多的 体积。

另一种类型的 驱动器在一个

被称为 ISO 驱动器的 芯片中集成了隔离器

和驱动器,这个芯片具有超过 每纳秒 100 伏的 CMTI 和 5kV 的

增强型隔离。

关系。传播延迟 仅为 19 纳秒,

脉宽失真 小于 5 纳秒。

重要的是,尺寸仅为 B 解决方案的一半,

与 A 类型相比可以节省 75% 以上的尺寸。

UCC21520 系列栅极 驱动器是业界最快的

5.7kV 隔离式双通道 栅极驱动器。

它还在 TI 的栅极驱动器 产品线中引进了

一个新的隔离系列。

集成式组件(包括 高级保护功能

和经过优化的 开关性能)

使得这款驱动器 能够用作

低侧栅极驱动器、高侧栅极驱动器、 低侧栅极驱动器上的

高侧栅极驱动器或者半桥栅极驱动器。

除了这些优势以外, 我们将讨论

具有 6A 和 4A 灌电流 和拉电流峰值的

栅极驱动器变压器,并将其 与 UCC21520 系列

进行比较。

它还支持 3 伏至 18 伏的 宽输入电压范围,

同时支持 6.5 伏至最高 30 伏的 宽输出电压

范围。

它还具有支持重叠和互锁 功能的可编程延迟

以及 0 纳秒至 5 微秒的

死区时间。

输出利用有源下拉 电路实现了失效防护。

此外,还提供了三个 欠压锁定选项——

5 伏、8 伏和 12 伏, 用于驱动

各种 MOSFET、IGBT 和碳化硅 MOSFET。

好了,我们介绍了 所有基础

知识,看起来 一点儿也不难。

它就是一个驱动器而已,

有一个输入,

有一个输出。

不过,让我们保持 一颗好奇心,来看看

它对栅极驱动器 性能的系统级

影响,例如寄生效应、 软硬开关差异、

非线性输出电容和 CMTI、dv/dt、di/dt

以及非音频 PCB 布局。

我们来更深入地 探讨一下。

我要向您展示 驱动器在转换器

效率和可靠性方面发挥的关键作用。

就寄生效应而言, 结电容、PCB 迹线

和 [听不清] 电感以及 电阻都会产生

寄生 效应。

因此,导通 和关断

会稍微 复杂一些。

对于碳化硅 MOSFET 和硅 MOSFET,还有

寄生二极管,它也 被视为会产生

寄生效应。

在分段线性 图示中,导通

过程可以分为 三个阶段。

第一个阶段是 栅极驱动器

电压、路径阈值 和通道电流增大。

使用红线突出 显示的等效

电路表明 CGS 在这个 阶段处于主导地位。

在第二阶段, 对 CGT 充电

并使 VDS 电压降低。

第三阶段是 通过对 CGD 和

CGS 充电并进一步 降低 [? RDSN ?],来进一步增大栅极电压。

重叠 VDS 和 ID 会产生开关损耗。

具有最短 T1 至 T3 阶段的更强驱动器

会导致开关损耗减小。

关断条件与 导通条件类似。

现在我们在半桥 配置中放置两个

器件,从而让情况 变得更复杂一点。

在硬开关 应用中,

会发生二极管 反向恢复。

左上角显示了 关键波形。

这个反向恢复将 反映在顶部开关上,

通常会产生更多的 导通损耗。

对于硅 MOSFET 的 体二极管和 IGBT 的

反并联二极管, 有两种预期结果,

您可以 看到由反向恢复

产生的大量浪涌电流。

对于硅 MOSFET, 过冲可能

是正常 开关电流

的 5 倍以上,IGBT 相对较小。

主要原因在于 硅 MOSFET 的体二极管

是寄生二极管, 未经过全面优化,

而 IGBT 的 紧凑二极管

可以是超级快速 或软恢复二极管。

反向恢复会增大损耗, 导致电流电压

过冲和 di/dt 增大。

还会导致栅极 振荡,与共源电感、

[听不清] 和栅极 驱动信号耦合的

di/dt 丢失,并减慢 开关切换速度。

减慢这个速度的 方法之一是增加一个

二极管或使用隔离输出 栅极驱动器,以增大导通电阻。

您可以看到, 如果增大 RG,

峰值反向恢复 时间会缩短。

但这样的改善 仍然非常有限。

前一部分中 讨论的反向

恢复对于优化系统 效率和可靠性而言

确实是一个难题。

要进一步消除 该问题,软开关

正是解决之道。

与临界模式 图腾柱 PFC

和 IOC 转换器一样,

它们都会在 VDS 电压降至 0 后

导通器件。

对于软开关, 前面提到的

三个阶段现在 只剩下一个阶段。

没有中间充电过程。

在输出电容完全 放电后导通器件,

器件通道电流 由外部电路决定,

而不是由寄生效应决定。

与硬开关相比, di/dt 通常

非常低, 因此不会出现重叠。

不存在导通损耗。

由于栅极驱动器损耗 机制也会改变,

因此对于硬开关,假设 栅极驱动器电压

为 10 伏,阴影区域、 打开和关断区域

是栅极驱动器电路 中的总损耗。

每个周期的总能量 是总面积 Qg 乘以

10 伏 VGS。

对于软开关,由于 没有中间充电过程,

因此红色实线 表示导通轨道。

关断与硬 开关类似。

与硬开关栅极 驱动器损耗

相比,软开关的 损耗更小。

软开关可以消除 此导通损耗。

不过,关断 也是硬开关。

与快速模式 电流传导

类似,关断 电流加倍。

如果使用弱 驱动器来驱动

FET,那么开关 损耗肯定会增加。

这意味着驱动器具有 更低的灌电流能力。

在使用强大的栅极 驱动器时,您几乎

不会看到中间平坦区域, 并且重叠时段也会

最小化。

重要的是, 开关行为

不受栅极 电流控制,

而是受输出电容和 负载电流控制。

考虑高度 非线性电容,

右上角显示了 分段线性开关

波形。

初始阶段非常低的 dv/dt 会成为一个电容器,

低电压 非常大,

为 5 纳法、0 伏。

随后非常高的 dv/dt 和高电压

导致进一步 最小化的重叠面积。

此处是一个关断 超结 MOSFET 的

实验示例。

将波形放大,可以 看到栅极驱动器非常

干净,具有很短的 中间平坦时间。

VDS 以非常缓慢的速度 增大并且及早关断。

您可以看到,比例 仅为每分段 5 伏,

然后升高。

所有开关电压 和电流

在 VGS 完全关断 之后发生变化,

这意味着开关行为 不是受栅极驱动器控制,

而是受输出电容和负载电流控制。

尽管使用强大的栅极 驱动器时的重叠面积

已降至最低,但它仍然存在。

如果我们测量它, 肯定会看到重叠。

不过,这是真正的损耗吗?

让我们看一看 常用 IOC 电路的

关断机制, 并考虑到

每个器件都包含 一个通道、体二极管和一个 CDS。

在第一阶段, 底部 FET 导通,

电流流过 通道。

在第二阶段,通道 关断,通道电流

减小,剩余的电流 会对两个开关的

输出电容充电 和放电。

由于相对大的 电感负载,

开关转换期间的 负载电流保持

[听不清]。

在第三阶段,通道将关断。

所有负载电流用于 继续对输出电容充电和

放电。

在最后一个阶段,会实现 [? ZVS ?],电流会 流过

体二极管。

实际损耗仅在 第二阶段发生,

在这个阶段中,通道 电流和电压发生

重叠。

第三阶段只会对 输出电容充电和放电。

我们 知道,所有输出电容

能量将在软开关期间的 下一个周期中恢复。

具有更小的损耗 和关断是很好的。

不过,dv/dt 和 di/dt 取决于负载,

可能在非常重的负载下 生成高 dv/dt 和

di/dt。

对于开关节点 中的高 dv/dt,

其行为确实是 退出寄生电容的

噪声源,寄生电容 包括

电平转换器电容、 自举二极管或结电容。

在通过这个电容器 进行耦合时,

会向初级侧接地 基准注入噪声。

如果您丢失了干净的 接地,那么栅极驱动器可能会

出现故障。

在这个实验中, 存在波形输入,

但缺少输出过程。

15 安电流 将关断,左侧

图表显示了 氮化镓和

超结 MOSFET 的 dv/dt 以及栅极驱动器电阻。

正如您看到的, MOSFET 的 dv/dt

可以达到每 纳秒 50 伏以上。

氮化镓 甚至更高,

超过每纳秒 150 伏。

di/dt 具有 类似的趋势。

一种解决方案是为低侧 栅极驱动器添加电平

转换器,尝试分隔 电源接地和逻辑接地。

此外,在采用额外旁通 电容器的情况下,

通过增大自举 电容电阻、

增加充电回路以及增大 电感,将环路最小化

而且 dv/dt 噪声 将流过不同的

路径。

因此,将有更少的 噪声流过初级侧。

讨论了 dv/dt 之后, 我们来看一看 di/dt。

它与寄生 电感相关。

不幸的是, 寄生效应无处不在。

当 di/dt 较高时, 不但会减慢驱动器的速度,

还会导致开关 节点中发生

严重漏电。

例如,当关断 顶部开关时,

底部分支将具有 正 di/dt,

实际电路中会 同时存在寄生电感、[? HSP ?]

和过冲 漏电。

这个过冲会导致 驱动器故障、

后二极管过流以及 VHP 减去 VHS 之后过度充电。

为了提高 驱动器的稳健性,

新的 27714 栅极 驱动器可支持

负 70 伏、100 纳秒 和负 30 伏、

200 纳秒。

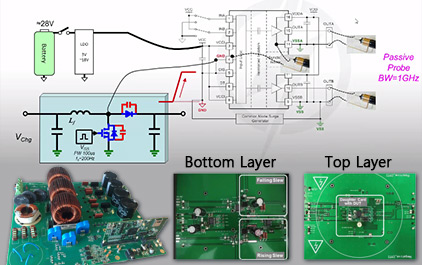

TIDA-01159 是一种紧凑、 易于评估的

参考设计,适用于 额定驱动功率级为

1 伏至 690 伏的 UCC21520。

这种设计适用于 所有具有半桥功率级

的设备。

板中内置了简单的 低成本隔离式电源,

用于驱动高侧开关。

这种设计演示了 如何并能够帮助客户

评估 UCC21520 栅极 驱动器众多

功能的性能, 栅极驱动器具有

5kV 隔离电压下的 高驱动力仪表、

适用于高 CMTI 环境 的稳健器件以及

采用碳化硅 MOSFET 的器件的高频

运行能力。

这种解决方案提供了 简单易用的 [听不清]

板,用于比较 采用传统电源

变压器的解决方案在 驱动半桥功率级

方面的性能。

与以前的设计 TIDA-01160 以及 UCC53 系列

栅极驱动器的其他 设计参考类似。

这种设计适用于 需要使用单个

隔离式栅极 驱动器来驱动 IGBT

或碳化硅 MOSFET 的设备。

关键终端设备包括 单相或三相

UPS、直流充电电源 和 [听不清] 系统。

板中内置了低成本的 隔离式电源,

用于驱动具有 负电压 [听不清] 的高侧

开关。

总的来说,我们介绍了 栅极驱动基础知识,

并介绍了 低侧、高侧和低侧

以及隔离式栅极驱动器。

我们还介绍了 寄生效应及其对

软开关和硬开关的影响、 具有强大栅极

驱动器的非线性输出电容、 CMTI、dv/dt 和 di/dt

以及如何隔离 dv/dt 产生的本底噪声。

有关更多信息,请 参阅 TIDA 参考设计。

非常感谢 您的观看。 503

手机看

扫码用手机观看

视频简介

视频简介

掌握高压门驱动器设计的艺术和基础

所属课程:TI HVI系列培训

发布时间:2018.04.11

视频集数:26

本节视频时长:00:26:09

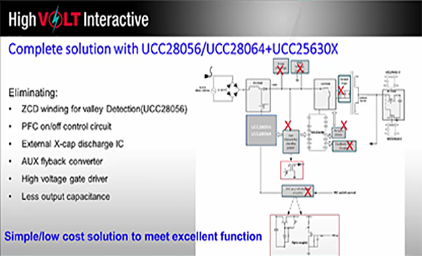

HVI为TI 美国本土每年一届的系统级电源设计研讨会。在这个研讨会中,TI的高级工程师们将和大家讨论常见的系统级电源设计中的各类问题,并介绍TI最新的创新电源解决方案。 会议讨论的主题涵盖从PFC到隔离式栅极驱动器,包括宽带隙解决方案以及电动汽车(EV)等应用主题。

本系列培训收录了20多个HVI研讨会上的讨论主题,您可以观看并从您感兴趣的主题中学习各种系统级电源设计的解决方案。从功率因数校正(PFC)的基本原理到设计多功率电源系统,请选择您最喜欢的主题,并开始学习吧。

未学习 深度掌握隔离驱动器瞬态共模噪音抑制及其特性

未学习 深度掌握隔离驱动器瞬态共模噪音抑制及其特性

未学习 熟练掌握高压MOSFET/IGBT栅极驱动设计

未学习 熟练掌握高压MOSFET/IGBT栅极驱动设计

未学习 1.1 LLC控制:更快,更强,更好---第一部分

未学习 1.1 LLC控制:更快,更强,更好---第一部分

未学习 1.2 LLC控制:更快,更强,更好---第二部分

未学习 1.2 LLC控制:更快,更强,更好---第二部分

未学习 1.3 LLC控制:更快,更强,更好---第三部分

未学习 1.3 LLC控制:更快,更强,更好---第三部分

未学习 1.4 LLC控制:更快,更强,更好---第四部分

未学习 1.4 LLC控制:更快,更强,更好---第四部分

未学习 1.1为你的临界模式PFC提供超强动力 - 课程介绍

未学习 1.1为你的临界模式PFC提供超强动力 - 课程介绍

未学习 1.2为你的临界模式PFC提供超强动力 - PFC以及CRM PFC工作原理

未学习 1.2为你的临界模式PFC提供超强动力 - PFC以及CRM PFC工作原理

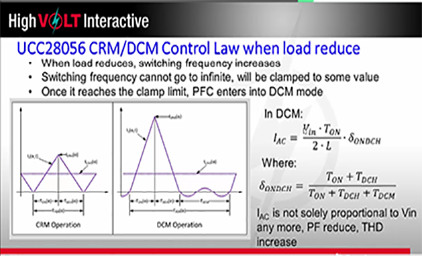

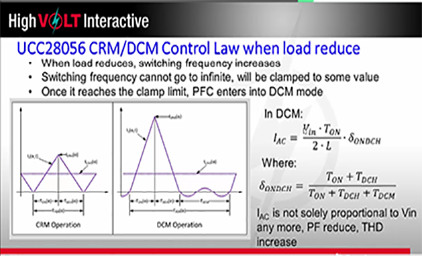

未学习 1.3为你的临界模式PFC提供超强动力 - UCC28056 CRMDCM控制芯片工作原理

未学习 1.3为你的临界模式PFC提供超强动力 - UCC28056 CRMDCM控制芯片工作原理

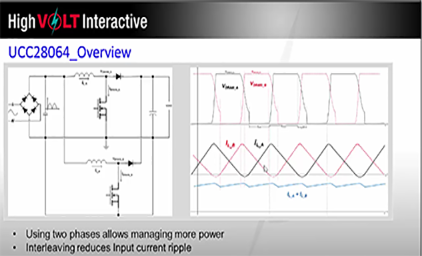

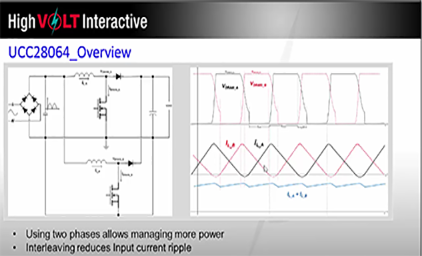

未学习 1.4为你的临界模式PFC提供超强动力 - UCC28064 CRM控制芯片工作原理

未学习 1.4为你的临界模式PFC提供超强动力 - UCC28064 CRM控制芯片工作原理

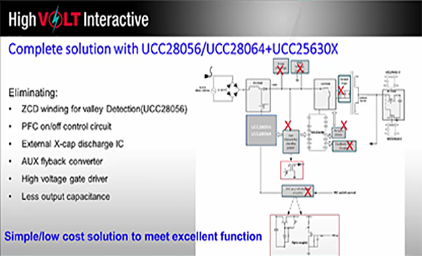

未学习 1.5为你的临界模式PFC提供超强动力 - 课程总结

未学习 1.5为你的临界模式PFC提供超强动力 - 课程总结

未学习 设计超高功率密度的小功率AC-DC电源

未学习 设计超高功率密度的小功率AC-DC电源

未学习 USB type C PD协议设计考量

未学习 USB type C PD协议设计考量

未学习 如何驱动碳化硅MOSFET以优化高功率系统的性能和可靠性

未学习 如何驱动碳化硅MOSFET以优化高功率系统的性能和可靠性

未学习 GaN产品应用于可靠和高密度电源的设计

未学习 GaN产品应用于可靠和高密度电源的设计

未学习 门驱动器设计-从基础到细节

未学习 门驱动器设计-从基础到细节

未学习 常见门驱动器问题及其解决方法

未学习 常见门驱动器问题及其解决方法

未学习 高功率密度和高效率适配器的设计考虑-第1部分

未学习 高功率密度和高效率适配器的设计考虑-第1部分

未学习 高功率密度和高效率适配器的设计考虑-第2部分

未学习 高功率密度和高效率适配器的设计考虑-第2部分

未学习 解除有源钳反激回路补偿的神秘化

未学习 解除有源钳反激回路补偿的神秘化

未学习 用GaN设计可靠的高密度功率解决方案-第一部分

未学习 用GaN设计可靠的高密度功率解决方案-第一部分

未学习 用GaN设计可靠的高密度功率解决方案-第二部分

未学习 用GaN设计可靠的高密度功率解决方案-第二部分

未学习 掌握高压门驱动器设计的艺术和基础

未学习 掌握高压门驱动器设计的艺术和基础

未学习 掌握隔离门驱动器的稳健性——CMTI的深入研究

未学习 掌握隔离门驱动器的稳健性——CMTI的深入研究

未学习 削减待机功耗和系统成本

未学习 削减待机功耗和系统成本

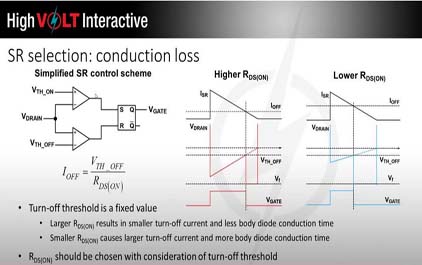

未学习 什么时候可以同步整流提高效率?

未学习 什么时候可以同步整流提高效率?