电源管理

最新课程

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWR6443、xWR6843 和 xWR1843

- 德州仪器 (TI) 毫米波雷达器件的自校准功能:xWRL6432、xWRL1432 和 xWRL6844

- 中端 SBC 概述

- CC3351:无线屏幕共享演示

- IWRL6432WMOD 模块概述

- 借助 AI 驱动的 CCStudio™ IDE 加速开发

- 重新构想人工智能数据中心电源:从电网到终端的全链路方案

- 如何将 PurePath Console (PPC3) 用于 TI 音频转换器

- 为人形机器人提供安全高效运行的动力保障

- 《使用 C2000 IDE-Assist 从 F28x 迁移到 F29x》视频

热门课程

常见门驱动器问题及其解决方法

大家好。

我叫 Mamadou Diallo。

我是高功率驱动器组的 一名应用工程师。

我今天将讨论 许多拓扑中

最常见的栅极驱动器 缺陷以及如何解决它们。

该主题是由 Ritesh Oza 和张伟(音译)

在 HPD 应用团队的 帮助下准备的。

本演示将讨论 与驱动器偏置、

自举电源以及 生成高侧偏置

所必需的组件 选择相关的缺陷。

我还将讨论功能 引脚开路的影响

以及栅极驱动器 电路中 dv/dt 噪声的影响。

然后,我将确认寄生 效应,最后展示

与糟糕的布局相关的 问题及其纠正方法。

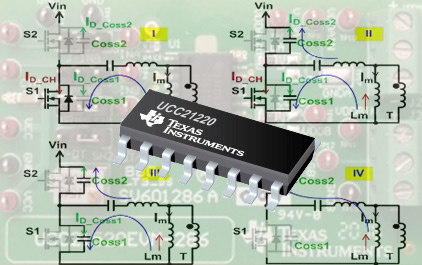

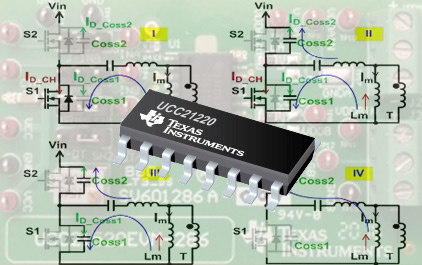

本演示中所提及的 器件型号包括

带互锁的 620 伏 半桥驱动器 UCC27712、

带集成引导 二极管的 120 伏

半桥栅极驱动器 UCC27211、 3kVRMS 隔离式双通道栅极

驱动器 UCC21220 以及 5.7kVRMS 隔离式双通道

栅极驱动器 UCC21520。

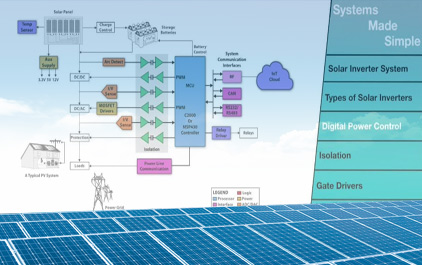

我今天要讨论的 这些拓扑与电机

驱动器应用、开关模式 电源以及光伏逆变器

应用相关。

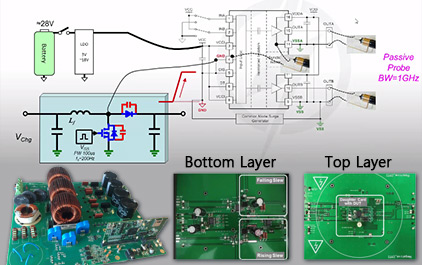

本演示是互动性的, 因此对于每个问题,

我将首先展示一些 波形和原理图,

然后我将暂停 一会儿,以便

您有时间思考 问题的可能

根源和解决 方案,最后

分享答案。

本演示分为 多个视频。

在该第一个视频中, 我们将讨论偏置

和自举组件

好,让我们步入正题吧。

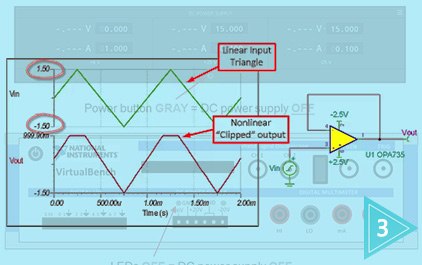

对于我们的第一个问题, 请仔细查看提供的波形

和原理图。

VCC 电源上 为何存在纹波?

导致该纹波的 原因可能是什么?

这是一个半桥 配置,其中一个

PWM 信号控制 驱动器的输入。

自举电路 -- 包含 C 偏置、

引导电容器 和引导

二极管 -- 在高侧 导通时间为高侧

FET 生成偏置。

设计将开关节点 作为高侧 FET 的基准。

驱动器的低侧 输出 LO 为以

接地端为基准的 低侧 FET 提供偏置。

在右侧,通道 1, 蓝色的波形

捕获 VCC,其中存在 大约 3.5 伏的纹波。

通道 3, 粉色的波形,

显示了驱动器的 低侧输出 LO 开关,

其峰峰值为 10 伏。

通道 2, 绿色的波形,

显示了高侧输出 HO。

请暂停视频, 花一点儿时间

思考可能的原因。

您是否能够 确定原因?

您是否猜到原因 是偏置电容器?

如果您猜到了,那么您是正确的。

请注意,在原理图 下面,C 偏置等于

C 引导,等于 1 微法, 这可能会在 VCC 电源上

产生很高的纹波, 从而可能导致驱动器

故障,如波形图中 所示,其中 HO 和 LO

同时开关, 从而导致击穿。

实际上,偏置电容器 大小设置不准确,

从而无法使电容 发生直流偏置和

温度漂移。

如果 VCC 上的纹波达到 UVLO 阈值并禁用栅极

驱动器,那么这可能 会导致 UV LO 跳变。

该问题导致的另一个 后果是电路容易受 EMI

噪声的影响。

要解决该问题,我们首先 需要正确地确定偏置

电容器的大小。

为自举电容器 充电的电荷

必须来自 VCC 旁路电容器。

作为一般的经验 法则,应将 C 偏置的

数大小确定为 至少比引导

电容器大 10 倍,以便 它不会在引导电容器

充电期间耗尽。

这样引导电容器就 可以在充电序列期间

正常充电。

在最坏的情况下, 该 10 倍的比率会

在 VDD 电容器上 生成最大 10% 的纹波。

右下角 还提供了

一种用于确定 C 偏置的替代方法。

它包括确定 HP 上的 所需纹波以及 Δ HP

等于栅极驱动器 IC 的电源电压减去

二极管数据表中提供的 引导二极管正向电压降,

再减去栅极驱动器 数据表中

提供的 HP 引脚 UVLO 下降阈值。

接下来,您可以 通过采用我们

刚才计算的总 Δ HP 电荷的比率

来确定引导电容器。

该电容器的最大值 会随应用而变化。

在确定偏置电容器的 大小之后,应选择

具有足够电压 额定值、温度系数

和电容容差的 低 ESR 低 ESL

表面多层 陶瓷电容器,

这一点很重要。

多层陶瓷 电容器上的

C 偏置会影响 实际的电容值。

例如,在施加 15VDC 的直流

偏置时,25 伏 1 微法 x7 RS 电容器的测量值

仅为 500 纳法。

这里的下一个 问题显示了半桥

配置的波形。

黄色的通道 1 是高侧输入。

通道 3 以红色 显示了开关节点。

蓝色的通道 3 是低侧输出,

通道 4 捕获 高侧输出 HO。

您是否能够说明 HO 曲线会发生什么情况?

请花一点儿 时间思考答案。

您是否注意到高侧 FET 上发生的泄漏?

该 HO 泄漏可能是由 多种因素的组合导致的,

其中包括低引导 电容器值无法

存储驱动高侧 FET 所需的能量。

该问题的另一种 常见原因可能

与高侧的低 栅源电阻有关。

该问题的另一种 可能原因是以

低频率进行开关。

所有这些原因 都可能导致

MOSFET 的结端子发热 以及输出上产生纹波。

该问题的解决方案 包括增大引导

电容器,以便为高侧 栅极提供所需的偏置。

增大栅极电阻器 也有助于解决该问题。

在实施这些 更改之后,

应使引导电容器 非常靠近驱动器的

HP/HS 引脚, 这一点也很重要。

这里是下一个常见问题, 它仍与半桥拓扑有关。

在右侧,黄色的 通道 1 捕获 HP

至接地端开关, 粉色的通道 3

捕获低侧输出 LO。

您是否能够根据所示的 波形指出这里的问题?

现在请暂停, 以考虑您的答案。

您是否通过 高侧关闭

进入了负 HS 瞬态?

很正确,但这 不是全部答案。

对引导电容器进行过度 充电也是这里的问题所在。

请注意低侧 输入 LO 的导通

时间,它远远 超过 500 毫秒。

这会在引导电容器上 产生过度充电,

因此会在 HP 节点上产生

振荡和过冲,这在 通道 1 中以黄色显示。

该过冲或振铃几乎 可以达到 40 伏,

这远远超过现代 驱动器的 HP/HS [听不清]。

一种纠正该问题的 方法是增大引导

电容器值,从而增大 该电容器的能量

储存容量。

一种替代方法是 增大引导电阻器,

从而降低对引导电容器 进行充电的峰值电流,

因此增大为引导 电容器充电的时间

常数 τ。

在高侧关闭时间或 低侧导通时间期间

发生的该时间常数 可以解释对占空比的

依赖性。

该占空比是常数, 应相应地调节

引导电阻器和引导 电容器,以实现所需的

启动时间。

对于下一个常见错误, 我们具有与前一个示例

相同的拓扑。

通道 1,黄色的 波形捕获 HP 至

接地端电压; 通道 2,蓝色的

波形显示了 HO 至接地端输出;

通道 3 捕获 粉色的开关节点。

您是否看到波形中 有任何错误?

如果你您需要更多时间, 请暂停视频,以确定可能的

问题及其原因。

您是否识别出 HS 波形是不一致的?

请注意这个, 每隔一个脉冲,

HS 信号就有时与 20 伏至接地不一致,

有时与 20 伏 至 15 伏不一致。

这通常与在低侧 FET 导通时间期间引导

电容器未充满电相关。

请记住,每次低侧 FET 导通时,引导

电容器都会充电, 因此,如果低侧 FET

导通时间不足以 将引导电容器充满电,

那么我们就会在 HS 节点上看到这些不一致。

该问题的一种 可能解决方案

是降低引导,以便 允许偏置电源的

峰值电流快速 对引导电容器

进行充电。

如之前所述, 可以调节时间

常数 RC,以实现 所需的启动时间。

该问题的另一种 可能解决方案

是确保高侧 开关具有最短

导通时间,从而 允许低侧 FET 导通

时间足够使引导 电容器充满电。

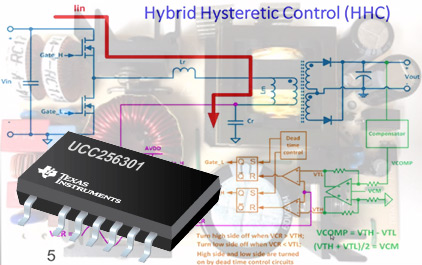

下一个问题与隔离式 栅极驱动器相关,

其中高侧引导电源 开启并由蓝色的

Vboot 捕获。

驱动器也已启用, 如通道 1、蓝色的

波形所示。

PWM 输入,HI 和 LI 也都开启。

波形上的粉色曲线 显示低侧输出在正常

开关,但高侧 输出是平坦的,

没有开关发生, 如绿色的曲线所示。

什么可能会导致 该问题,为什么?

请暂停视频, 以思考答案。

您是否能够 确定该问题?

请注意,输入 LO 远在引导电容器

电源达到 UVLO 上升 阈值之前就已启用。

该设计不考虑 在加电期间

发生的 UVLO 延迟, 从而导致脉冲

跳跃或脉冲缺失。

我们可以看到 HO 脉冲在电源达到

UVLO 上升阈值 50 微秒之后进行开关。

该 UVLO 延迟 取决于驱动器,

必须要加以考虑。

在驱动器为提供适当的 输出状态做好准备之前,

UVLO 上升沿 至输出存在

加电延迟。

该延迟会因 驱动器而异。

对于 UCC21540, 它通常为 40 微秒。

因此,建议在 驱动器偏置

就绪之后,在发出 PWM 信号之前,考虑

适当的余量。

右侧的图 显示了输入

和 VDD 电源的加电 UVLO 延迟时序图。

必须仅在两个 偏置电源都

就绪之后再 同步输入信号。 228

-

未学习 深度掌握隔离驱动器瞬态共模噪音抑制及其特性

未学习 深度掌握隔离驱动器瞬态共模噪音抑制及其特性

-

未学习 熟练掌握高压MOSFET/IGBT栅极驱动设计

未学习 熟练掌握高压MOSFET/IGBT栅极驱动设计

-

未学习 1.1 LLC控制:更快,更强,更好---第一部分

未学习 1.1 LLC控制:更快,更强,更好---第一部分

-

未学习 1.2 LLC控制:更快,更强,更好---第二部分

未学习 1.2 LLC控制:更快,更强,更好---第二部分

-

未学习 1.3 LLC控制:更快,更强,更好---第三部分

未学习 1.3 LLC控制:更快,更强,更好---第三部分

-

未学习 1.4 LLC控制:更快,更强,更好---第四部分

未学习 1.4 LLC控制:更快,更强,更好---第四部分

-

未学习 1.1为你的临界模式PFC提供超强动力 - 课程介绍

未学习 1.1为你的临界模式PFC提供超强动力 - 课程介绍

-

未学习 1.2为你的临界模式PFC提供超强动力 - PFC以及CRM PFC工作原理

未学习 1.2为你的临界模式PFC提供超强动力 - PFC以及CRM PFC工作原理

-

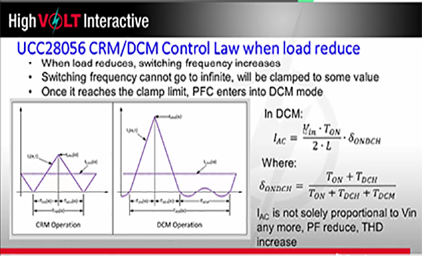

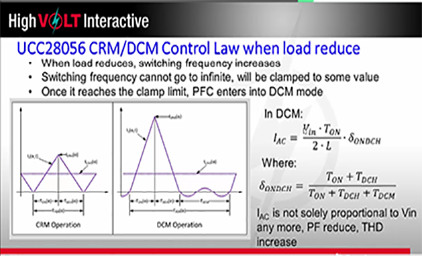

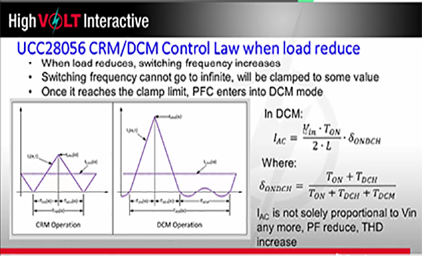

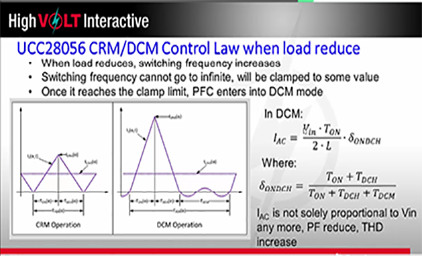

未学习 1.3为你的临界模式PFC提供超强动力 - UCC28056 CRMDCM控制芯片工作原理

未学习 1.3为你的临界模式PFC提供超强动力 - UCC28056 CRMDCM控制芯片工作原理

-

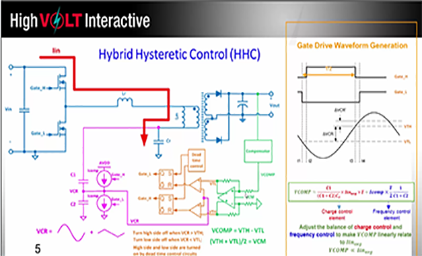

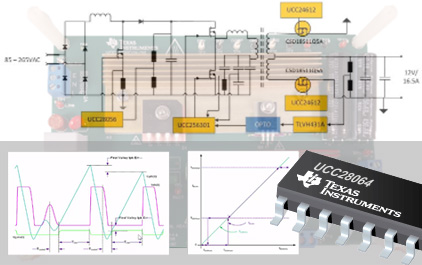

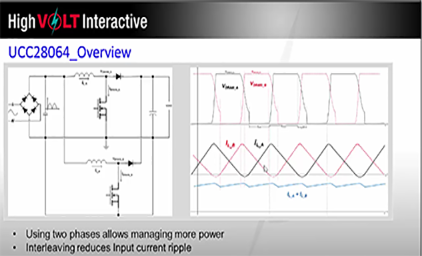

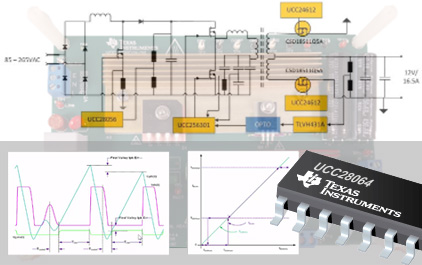

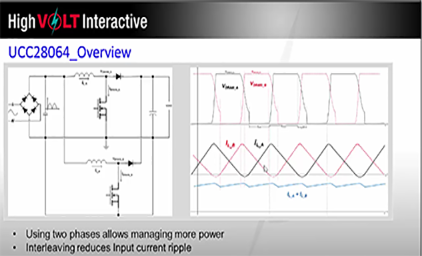

未学习 1.4为你的临界模式PFC提供超强动力 - UCC28064 CRM控制芯片工作原理

未学习 1.4为你的临界模式PFC提供超强动力 - UCC28064 CRM控制芯片工作原理

-

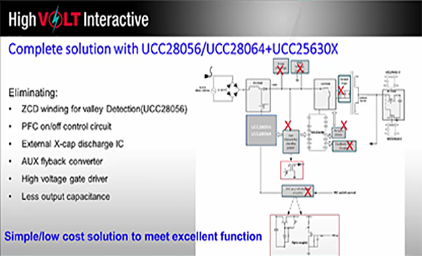

未学习 1.5为你的临界模式PFC提供超强动力 - 课程总结

未学习 1.5为你的临界模式PFC提供超强动力 - 课程总结

-

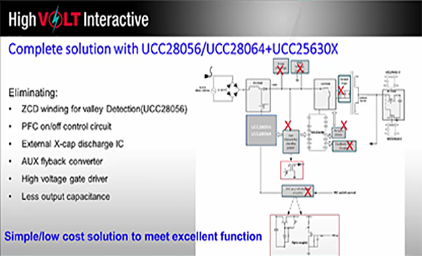

未学习 设计超高功率密度的小功率AC-DC电源

未学习 设计超高功率密度的小功率AC-DC电源

-

未学习 USB type C PD协议设计考量

未学习 USB type C PD协议设计考量

-

未学习 如何驱动碳化硅MOSFET以优化高功率系统的性能和可靠性

未学习 如何驱动碳化硅MOSFET以优化高功率系统的性能和可靠性

-

未学习 GaN产品应用于可靠和高密度电源的设计

未学习 GaN产品应用于可靠和高密度电源的设计

-

未学习 门驱动器设计-从基础到细节

未学习 门驱动器设计-从基础到细节

-

未学习 常见门驱动器问题及其解决方法

未学习 常见门驱动器问题及其解决方法

-

未学习 高功率密度和高效率适配器的设计考虑-第1部分

未学习 高功率密度和高效率适配器的设计考虑-第1部分

-

未学习 高功率密度和高效率适配器的设计考虑-第2部分

未学习 高功率密度和高效率适配器的设计考虑-第2部分

-

未学习 解除有源钳反激回路补偿的神秘化

未学习 解除有源钳反激回路补偿的神秘化

-

未学习 用GaN设计可靠的高密度功率解决方案-第一部分

未学习 用GaN设计可靠的高密度功率解决方案-第一部分

-

未学习 用GaN设计可靠的高密度功率解决方案-第二部分

未学习 用GaN设计可靠的高密度功率解决方案-第二部分

-

未学习 掌握高压门驱动器设计的艺术和基础

未学习 掌握高压门驱动器设计的艺术和基础

-

未学习 掌握隔离门驱动器的稳健性——CMTI的深入研究

未学习 掌握隔离门驱动器的稳健性——CMTI的深入研究

-

未学习 削减待机功耗和系统成本

未学习 削减待机功耗和系统成本

-

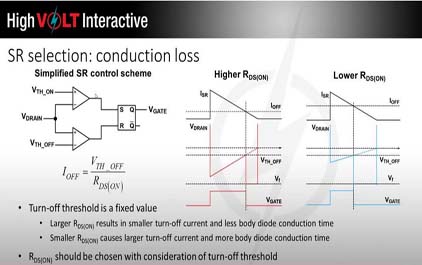

未学习 什么时候可以同步整流提高效率?

未学习 什么时候可以同步整流提高效率?