施密特触发 CMOS 输入

Loading the player...

将在30s后自动为您播放下一课程

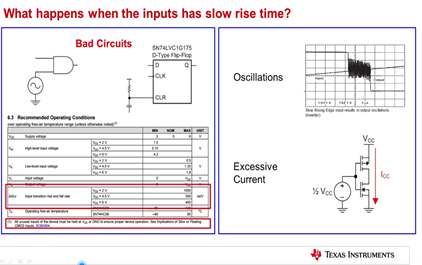

大家好,欢迎观看 The Logic Minute。 在本视频中,我们将讨论 施密特触发 CMOS 输入 架构的好处和工作原理。 几乎所有逻辑器件 都有相似的内部结构, 包含缓冲输入、 逻辑功能和 独立的输出驱动器。 在本视频中, 我们将了解施密特 触发 CMOS 输入结构。 右侧是基于 CMOS 的 施密特触发输入 电路的一种常见设计, 在许多 CMOS 设计 手册中都可以找到。 这种电路设计 有许多变体。 但是,它们的工作 原理都是相同的, 所以在本视频中 我会以此设计为例。 这些输入具有 与标准 CMOS 输入相似的 好处,包括电压受控、低功耗 和响应快速。 但是,它们还有 两种重要好处, 即抗噪声和容忍 缓慢的输入信号 传输。 在这里,您可以看到 绿色的输入波形和 蓝色的输出波形。 施密特触发架构 强制上升沿转换 电压 VT+ 高于 下降沿转换 电压 VT-。 两者之间的差就是 ΔVT, 通常也称为 输入阈值迟滞。 此阈值差值使电路能够 高度容忍幅度 低于迟滞值的 噪声。 虽然输入信号 多次越过阈值, 但输出在每个 边沿上仍然只有 单一传输线。 我们来详细了解 此电路的工作原理, 以上升沿为例。 输入保持在 0 伏时, 底部的两个输入控制 晶体管强制关断, 而顶部的两个导通, 为电流提供 一条输出路径。 顶部的反馈 晶体管关断, 底部的反馈 晶体管导通。 这导致标为 N 的 节点保持在 VCC。 在静态状态下, 非常小的电流 可以从 VCC 流向接地。 当输入电压从 0 伏 转换为电源的一半时, 底部晶体管将导通, 因为它的控制电压 会超过其阈值电压。 这使得部分电流 可以流动,并在反馈 晶体管与底部 控制晶体管之间 产生一个分压器。 反馈节点电压 在这里标为 VN。 第二个晶体管的控制 电压,此处显示为 VGS, 依赖于反馈 节点的电压。 反馈晶体管比专用于 设置 VN,以使 VGS 不超过阈值电压, 直至达到所需的 正输入阈值。 随着输入电压增加, 底部的晶体管将 导通更多,从而降低 VN, 并最终允许 第二个晶体管导通。 一旦达到正阈值, 第二个晶体管导通 而且输出改变状态。 输出电压的这种 变化会改变反馈电路, 使得 Nfet 关断, 而 Pfet 导通。 这将驱动节点 P 接地, 现在器件的状态与 开始时恰好相反。 反馈电路使得 施密特触发输入 架构能够弹性应对 噪声和缓慢转换 信号。 对于下降沿, 电路的工作 方式完全相同, 只是每个 MOSFET 处于相反的状态。 我们来看一看输入 转换如何影响器件的 电源电流。 随着输入转换, 电源电流会因 反馈电路而有所 增加。 在这里可以 看到,输入电压 从 0 伏转换到 VCC 时, 预期的电源电流会增加。 我们可以看到 当器件状态从 低输入更改为 高输入时,电流急剧 下降的地方。 当输入信号从 VCC 再转换为 0 伏时, 电源电流会 遵循不同的曲线。 这是因为另一个 反馈电路现已激活, 我们可以清楚地看到 超过负输入电压阈值时 电路改变状态的地方。 就像标准的 CMOS 输入一样, 当输入处于两轨道之间时, 施密特触发输入会消耗 一些额外的电源电流。 关键区别在于, 施密特触发输入 能够在较慢的 噪声输入下运行, 所以在相同的条件下, 它们的功耗仍然远低于 标准 CMOS 输入, 而且将施密特触发输入 保持在阈值之间总是 安全的。 如果您的系统有 缓慢的转换信号 或嘈杂的数字逻辑信号, 那么施密特触发输入器件 是预防问题的 出色解决方案。 谢谢观看。 如果您的项目 需要施密特触发 输入逻辑器件, 请访问 TI.com/logic 开始搜索。 如果您有任何 关于此主题的 技术性问题,请访问 E2E 论坛,直接向我们咨询。 where you can ask us directly.

大家好,欢迎观看 The Logic Minute。 在本视频中,我们将讨论 施密特触发 CMOS 输入 架构的好处和工作原理。 几乎所有逻辑器件 都有相似的内部结构, 包含缓冲输入、 逻辑功能和 独立的输出驱动器。 在本视频中, 我们将了解施密特 触发 CMOS 输入结构。 右侧是基于 CMOS 的 施密特触发输入 电路的一种常见设计, 在许多 CMOS 设计 手册中都可以找到。 这种电路设计 有许多变体。 但是,它们的工作 原理都是相同的, 所以在本视频中 我会以此设计为例。 这些输入具有 与标准 CMOS 输入相似的 好处,包括电压受控、低功耗 和响应快速。 但是,它们还有 两种重要好处, 即抗噪声和容忍 缓慢的输入信号 传输。 在这里,您可以看到 绿色的输入波形和 蓝色的输出波形。 施密特触发架构 强制上升沿转换 电压 VT+ 高于 下降沿转换 电压 VT-。 两者之间的差就是 ΔVT, 通常也称为 输入阈值迟滞。 此阈值差值使电路能够 高度容忍幅度 低于迟滞值的 噪声。 虽然输入信号 多次越过阈值, 但输出在每个 边沿上仍然只有 单一传输线。 我们来详细了解 此电路的工作原理, 以上升沿为例。 输入保持在 0 伏时, 底部的两个输入控制 晶体管强制关断, 而顶部的两个导通, 为电流提供 一条输出路径。 顶部的反馈 晶体管关断, 底部的反馈 晶体管导通。 这导致标为 N 的 节点保持在 VCC。 在静态状态下, 非常小的电流 可以从 VCC 流向接地。 当输入电压从 0 伏 转换为电源的一半时, 底部晶体管将导通, 因为它的控制电压 会超过其阈值电压。 这使得部分电流 可以流动,并在反馈 晶体管与底部 控制晶体管之间 产生一个分压器。 反馈节点电压 在这里标为 VN。 第二个晶体管的控制 电压,此处显示为 VGS, 依赖于反馈 节点的电压。 反馈晶体管比专用于 设置 VN,以使 VGS 不超过阈值电压, 直至达到所需的 正输入阈值。 随着输入电压增加, 底部的晶体管将 导通更多,从而降低 VN, 并最终允许 第二个晶体管导通。 一旦达到正阈值, 第二个晶体管导通 而且输出改变状态。 输出电压的这种 变化会改变反馈电路, 使得 Nfet 关断, 而 Pfet 导通。 这将驱动节点 P 接地, 现在器件的状态与 开始时恰好相反。 反馈电路使得 施密特触发输入 架构能够弹性应对 噪声和缓慢转换 信号。 对于下降沿, 电路的工作 方式完全相同, 只是每个 MOSFET 处于相反的状态。 我们来看一看输入 转换如何影响器件的 电源电流。 随着输入转换, 电源电流会因 反馈电路而有所 增加。 在这里可以 看到,输入电压 从 0 伏转换到 VCC 时, 预期的电源电流会增加。 我们可以看到 当器件状态从 低输入更改为 高输入时,电流急剧 下降的地方。 当输入信号从 VCC 再转换为 0 伏时, 电源电流会 遵循不同的曲线。 这是因为另一个 反馈电路现已激活, 我们可以清楚地看到 超过负输入电压阈值时 电路改变状态的地方。 就像标准的 CMOS 输入一样, 当输入处于两轨道之间时, 施密特触发输入会消耗 一些额外的电源电流。 关键区别在于, 施密特触发输入 能够在较慢的 噪声输入下运行, 所以在相同的条件下, 它们的功耗仍然远低于 标准 CMOS 输入, 而且将施密特触发输入 保持在阈值之间总是 安全的。 如果您的系统有 缓慢的转换信号 或嘈杂的数字逻辑信号, 那么施密特触发输入器件 是预防问题的 出色解决方案。 谢谢观看。 如果您的项目 需要施密特触发 输入逻辑器件, 请访问 TI.com/logic 开始搜索。 如果您有任何 关于此主题的 技术性问题,请访问 E2E 论坛,直接向我们咨询。 where you can ask us directly.

大家好,欢迎观看 The Logic Minute。

在本视频中,我们将讨论

施密特触发 CMOS 输入 架构的好处和工作原理。

几乎所有逻辑器件 都有相似的内部结构,

包含缓冲输入、 逻辑功能和

独立的输出驱动器。

在本视频中,

我们将了解施密特 触发 CMOS 输入结构。

右侧是基于 CMOS 的

施密特触发输入 电路的一种常见设计,

在许多 CMOS 设计 手册中都可以找到。

这种电路设计 有许多变体。

但是,它们的工作 原理都是相同的,

所以在本视频中 我会以此设计为例。

这些输入具有

与标准 CMOS 输入相似的 好处,包括电压受控、低功耗

和响应快速。

但是,它们还有 两种重要好处,

即抗噪声和容忍 缓慢的输入信号

传输。

在这里,您可以看到 绿色的输入波形和

蓝色的输出波形。

施密特触发架构 强制上升沿转换

电压 VT+ 高于 下降沿转换

电压 VT-。

两者之间的差就是 ΔVT,

通常也称为 输入阈值迟滞。

此阈值差值使电路能够

高度容忍幅度 低于迟滞值的

噪声。

虽然输入信号 多次越过阈值,

但输出在每个 边沿上仍然只有

单一传输线。

我们来详细了解 此电路的工作原理,

以上升沿为例。

输入保持在 0 伏时, 底部的两个输入控制

晶体管强制关断, 而顶部的两个导通,

为电流提供 一条输出路径。

顶部的反馈 晶体管关断,

底部的反馈 晶体管导通。

这导致标为 N 的 节点保持在 VCC。

在静态状态下, 非常小的电流

可以从 VCC 流向接地。

当输入电压从 0 伏 转换为电源的一半时,

底部晶体管将导通,

因为它的控制电压 会超过其阈值电压。

这使得部分电流 可以流动,并在反馈

晶体管与底部 控制晶体管之间

产生一个分压器。

反馈节点电压 在这里标为 VN。

第二个晶体管的控制 电压,此处显示为 VGS,

依赖于反馈 节点的电压。

反馈晶体管比专用于

设置 VN,以使 VGS 不超过阈值电压,

直至达到所需的

正输入阈值。

随着输入电压增加,

底部的晶体管将 导通更多,从而降低 VN,

并最终允许 第二个晶体管导通。

一旦达到正阈值,

第二个晶体管导通 而且输出改变状态。

输出电压的这种 变化会改变反馈电路,

使得 Nfet 关断, 而 Pfet 导通。

这将驱动节点 P 接地, 现在器件的状态与

开始时恰好相反。

反馈电路使得 施密特触发输入

架构能够弹性应对 噪声和缓慢转换

信号。

对于下降沿, 电路的工作

方式完全相同, 只是每个 MOSFET

处于相反的状态。

我们来看一看输入 转换如何影响器件的

电源电流。

随着输入转换,

电源电流会因 反馈电路而有所

增加。

在这里可以 看到,输入电压

从 0 伏转换到 VCC 时, 预期的电源电流会增加。

我们可以看到 当器件状态从

低输入更改为 高输入时,电流急剧

下降的地方。

当输入信号从 VCC 再转换为 0 伏时,

电源电流会 遵循不同的曲线。

这是因为另一个 反馈电路现已激活,

我们可以清楚地看到 超过负输入电压阈值时

电路改变状态的地方。

就像标准的 CMOS 输入一样,

当输入处于两轨道之间时, 施密特触发输入会消耗

一些额外的电源电流。

关键区别在于, 施密特触发输入

能够在较慢的 噪声输入下运行,

所以在相同的条件下, 它们的功耗仍然远低于

标准 CMOS 输入,

而且将施密特触发输入 保持在阈值之间总是

安全的。

如果您的系统有 缓慢的转换信号

或嘈杂的数字逻辑信号, 那么施密特触发输入器件

是预防问题的 出色解决方案。

谢谢观看。

如果您的项目 需要施密特触发

输入逻辑器件, 请访问 TI.com/logic

开始搜索。

如果您有任何 关于此主题的

技术性问题,请访问 E2E 论坛,直接向我们咨询。

where you can ask us directly.

大家好,欢迎观看 The Logic Minute。 在本视频中,我们将讨论 施密特触发 CMOS 输入 架构的好处和工作原理。 几乎所有逻辑器件 都有相似的内部结构, 包含缓冲输入、 逻辑功能和 独立的输出驱动器。 在本视频中, 我们将了解施密特 触发 CMOS 输入结构。 右侧是基于 CMOS 的 施密特触发输入 电路的一种常见设计, 在许多 CMOS 设计 手册中都可以找到。 这种电路设计 有许多变体。 但是,它们的工作 原理都是相同的, 所以在本视频中 我会以此设计为例。 这些输入具有 与标准 CMOS 输入相似的 好处,包括电压受控、低功耗 和响应快速。 但是,它们还有 两种重要好处, 即抗噪声和容忍 缓慢的输入信号 传输。 在这里,您可以看到 绿色的输入波形和 蓝色的输出波形。 施密特触发架构 强制上升沿转换 电压 VT+ 高于 下降沿转换 电压 VT-。 两者之间的差就是 ΔVT, 通常也称为 输入阈值迟滞。 此阈值差值使电路能够 高度容忍幅度 低于迟滞值的 噪声。 虽然输入信号 多次越过阈值, 但输出在每个 边沿上仍然只有 单一传输线。 我们来详细了解 此电路的工作原理, 以上升沿为例。 输入保持在 0 伏时, 底部的两个输入控制 晶体管强制关断, 而顶部的两个导通, 为电流提供 一条输出路径。 顶部的反馈 晶体管关断, 底部的反馈 晶体管导通。 这导致标为 N 的 节点保持在 VCC。 在静态状态下, 非常小的电流 可以从 VCC 流向接地。 当输入电压从 0 伏 转换为电源的一半时, 底部晶体管将导通, 因为它的控制电压 会超过其阈值电压。 这使得部分电流 可以流动,并在反馈 晶体管与底部 控制晶体管之间 产生一个分压器。 反馈节点电压 在这里标为 VN。 第二个晶体管的控制 电压,此处显示为 VGS, 依赖于反馈 节点的电压。 反馈晶体管比专用于 设置 VN,以使 VGS 不超过阈值电压, 直至达到所需的 正输入阈值。 随着输入电压增加, 底部的晶体管将 导通更多,从而降低 VN, 并最终允许 第二个晶体管导通。 一旦达到正阈值, 第二个晶体管导通 而且输出改变状态。 输出电压的这种 变化会改变反馈电路, 使得 Nfet 关断, 而 Pfet 导通。 这将驱动节点 P 接地, 现在器件的状态与 开始时恰好相反。 反馈电路使得 施密特触发输入 架构能够弹性应对 噪声和缓慢转换 信号。 对于下降沿, 电路的工作 方式完全相同, 只是每个 MOSFET 处于相反的状态。 我们来看一看输入 转换如何影响器件的 电源电流。 随着输入转换, 电源电流会因 反馈电路而有所 增加。 在这里可以 看到,输入电压 从 0 伏转换到 VCC 时, 预期的电源电流会增加。 我们可以看到 当器件状态从 低输入更改为 高输入时,电流急剧 下降的地方。 当输入信号从 VCC 再转换为 0 伏时, 电源电流会 遵循不同的曲线。 这是因为另一个 反馈电路现已激活, 我们可以清楚地看到 超过负输入电压阈值时 电路改变状态的地方。 就像标准的 CMOS 输入一样, 当输入处于两轨道之间时, 施密特触发输入会消耗 一些额外的电源电流。 关键区别在于, 施密特触发输入 能够在较慢的 噪声输入下运行, 所以在相同的条件下, 它们的功耗仍然远低于 标准 CMOS 输入, 而且将施密特触发输入 保持在阈值之间总是 安全的。 如果您的系统有 缓慢的转换信号 或嘈杂的数字逻辑信号, 那么施密特触发输入器件 是预防问题的 出色解决方案。 谢谢观看。 如果您的项目 需要施密特触发 输入逻辑器件, 请访问 TI.com/logic 开始搜索。 如果您有任何 关于此主题的 技术性问题,请访问 E2E 论坛,直接向我们咨询。 where you can ask us directly.

大家好,欢迎观看 The Logic Minute。

在本视频中,我们将讨论

施密特触发 CMOS 输入 架构的好处和工作原理。

几乎所有逻辑器件 都有相似的内部结构,

包含缓冲输入、 逻辑功能和

独立的输出驱动器。

在本视频中,

我们将了解施密特 触发 CMOS 输入结构。

右侧是基于 CMOS 的

施密特触发输入 电路的一种常见设计,

在许多 CMOS 设计 手册中都可以找到。

这种电路设计 有许多变体。

但是,它们的工作 原理都是相同的,

所以在本视频中 我会以此设计为例。

这些输入具有

与标准 CMOS 输入相似的 好处,包括电压受控、低功耗

和响应快速。

但是,它们还有 两种重要好处,

即抗噪声和容忍 缓慢的输入信号

传输。

在这里,您可以看到 绿色的输入波形和

蓝色的输出波形。

施密特触发架构 强制上升沿转换

电压 VT+ 高于 下降沿转换

电压 VT-。

两者之间的差就是 ΔVT,

通常也称为 输入阈值迟滞。

此阈值差值使电路能够

高度容忍幅度 低于迟滞值的

噪声。

虽然输入信号 多次越过阈值,

但输出在每个 边沿上仍然只有

单一传输线。

我们来详细了解 此电路的工作原理,

以上升沿为例。

输入保持在 0 伏时, 底部的两个输入控制

晶体管强制关断, 而顶部的两个导通,

为电流提供 一条输出路径。

顶部的反馈 晶体管关断,

底部的反馈 晶体管导通。

这导致标为 N 的 节点保持在 VCC。

在静态状态下, 非常小的电流

可以从 VCC 流向接地。

当输入电压从 0 伏 转换为电源的一半时,

底部晶体管将导通,

因为它的控制电压 会超过其阈值电压。

这使得部分电流 可以流动,并在反馈

晶体管与底部 控制晶体管之间

产生一个分压器。

反馈节点电压 在这里标为 VN。

第二个晶体管的控制 电压,此处显示为 VGS,

依赖于反馈 节点的电压。

反馈晶体管比专用于

设置 VN,以使 VGS 不超过阈值电压,

直至达到所需的

正输入阈值。

随着输入电压增加,

底部的晶体管将 导通更多,从而降低 VN,

并最终允许 第二个晶体管导通。

一旦达到正阈值,

第二个晶体管导通 而且输出改变状态。

输出电压的这种 变化会改变反馈电路,

使得 Nfet 关断, 而 Pfet 导通。

这将驱动节点 P 接地, 现在器件的状态与

开始时恰好相反。

反馈电路使得 施密特触发输入

架构能够弹性应对 噪声和缓慢转换

信号。

对于下降沿, 电路的工作

方式完全相同, 只是每个 MOSFET

处于相反的状态。

我们来看一看输入 转换如何影响器件的

电源电流。

随着输入转换,

电源电流会因 反馈电路而有所

增加。

在这里可以 看到,输入电压

从 0 伏转换到 VCC 时, 预期的电源电流会增加。

我们可以看到 当器件状态从

低输入更改为 高输入时,电流急剧

下降的地方。

当输入信号从 VCC 再转换为 0 伏时,

电源电流会 遵循不同的曲线。

这是因为另一个 反馈电路现已激活,

我们可以清楚地看到 超过负输入电压阈值时

电路改变状态的地方。

就像标准的 CMOS 输入一样,

当输入处于两轨道之间时, 施密特触发输入会消耗

一些额外的电源电流。

关键区别在于, 施密特触发输入

能够在较慢的 噪声输入下运行,

所以在相同的条件下, 它们的功耗仍然远低于

标准 CMOS 输入,

而且将施密特触发输入 保持在阈值之间总是

安全的。

如果您的系统有 缓慢的转换信号

或嘈杂的数字逻辑信号, 那么施密特触发输入器件

是预防问题的 出色解决方案。

谢谢观看。

如果您的项目 需要施密特触发

输入逻辑器件, 请访问 TI.com/logic

开始搜索。

如果您有任何 关于此主题的

技术性问题,请访问 E2E 论坛,直接向我们咨询。

where you can ask us directly.

手机看

扫码用手机观看

视频简介

视频简介

施密特触发 CMOS 输入

所属课程:逻辑和电平转换基础

发布时间:2022.09.02

视频集数:8

本节视频时长:00:04:48

在本课程中,从基本应用到器件操作的技术分析,逻辑专家提供有关标准逻辑器件的简短课程。

未学习 逻辑零件号剖析

未学习 逻辑零件号剖析

未学习 选择合适的自动双向电压转换器

未学习 选择合适的自动双向电压转换器

未学习 逻辑静电放电 (ESD) 保护

未学习 逻辑静电放电 (ESD) 保护

未学习 钳位二极管和 CMOS 逻辑器件

未学习 钳位二极管和 CMOS 逻辑器件

未学习 CMOS逻辑标准输入

未学习 CMOS逻辑标准输入

未学习 施密特触发 CMOS 输入

未学习 施密特触发 CMOS 输入

未学习 双极性逻辑输入操作

未学习 双极性逻辑输入操作

未学习 了解施密特触发器

未学习 了解施密特触发器

视频简介

视频简介