6.3 TI 高精度实验室 -I2C:转换器概述

Loading the player...

将在30s后自动为您播放下一课程

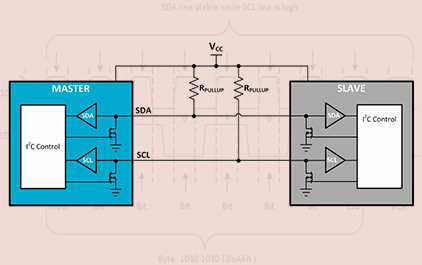

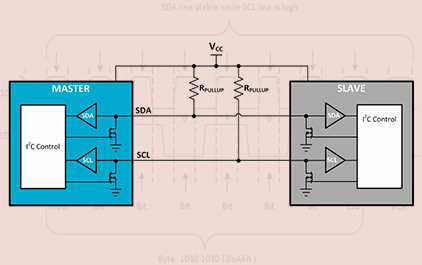

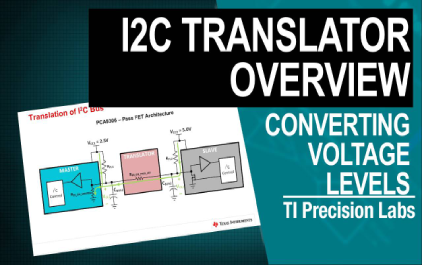

大家好,欢迎观看 高精度实验室 推出的 I²C 转换培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中进行转换、 如何在硬件中实施转换以及 它会对系统产生哪些影响。 I²C 使用一个 带有输入缓冲器的 开漏驱动器, 支持 双向通信。 这意味着上拉电阻器 完全控制着高电平 信号的生成。 如果您不熟悉 I²C 硬件层, 请参阅“I²C 硬件概述”视频, 了解更多 信息和培训。 在此图中,我们可以看到 两个器件具有不同的 VCC 电压, 即 VCCA1 和 VCCB2。 这意味着它们的 数字逻辑电平不同, 因此需要从一个电压电平 转换到另一个电压电平, 这一现象通常称为 电压电平不匹配。 以下是一个示例。 VCCA1 设置为 5 伏, VCCB2 设置为 3.3 伏, 那么上拉电阻器 应连接到哪个 VCC? 如果将上拉电阻器 连接到 3.3 伏的 VCCB2, 则总线上的 电压永远也 达不到 VCCA1 上的器件的 VIH, 也就是 5 伏的 70%,即 3.5 伏。 换言之,5 伏 总线中的器件 将不会看到 连接到 3.3 伏的 器件中的上拉电阻器 达到逻辑高电平。 如果将上拉电阻器 连接到 5 伏的 VCCA1, 则表明 VCC 为 3.3 伏的器件 将暴露在 高于其工作 电压的 电压中。 这样会导致 低压器件损坏, 而且 VIL 上的 电压电平仍会漂移。 很明显,必须纠正此电压 电平不匹配现象。 为此,需要使用 一个转换器,有时将其 称为电平转换器。 I²C 的转换 通常是使用 pass FET 架构 完成的,此架构可 实现电压电平隔离 并提供一种用来传递 低电平信号的方法。 不过,它无法 隔离总线电容。 我们需要看一看 pass FET 转换器的内部,以便 了解其工作原理。 在本例中,我们将 PCA9306 与 1 侧的主器件和 2 侧的从器件配合使用。 注意,它可以不 采用这种配置。 记住,I²C 是双向的, 主器件和从器件的 位置可以互换。 图中只显示了 I²C 通信所需的 两条线中的 一条,不过在 与 SCL 和 SDA 相关的 所有观察中, 物理实施方法 都是一样的。 让我们首先考虑 空闲状态,处于这种状态时, 两侧都是高电平, 转换器的任一侧 正在被拉低。 VCCA1 等于 2.5 伏, VCCB2 等于 5.0 伏。 所有 FET 都关闭。 总线的 1 侧 将被 RPU1 拉到 2.5 伏。 总线的 2 侧 将被 RPU2 上拉到 5.0 伏。 转换器上 标有 VGATE 的 pass FET 栅极具有电压。 在本例中, 它的电压为 2.5 伏。 我们以主器件 拉低为例。 当 1 侧开始拉低时, CBUS 会放电, 我们要开始产生 一个状态,以便在 设置为 2.5 伏的 VGATE 与电压为 总线电压的 VSOURCE 之间产生压差。 随着 VGS 增大并 超过这些 pass FET 的 阈值电压, 通常为 0.7 伏, 它会快速打开。 很容易看到, 当主器件拉低时, pass FET 会打开, 1 侧和 2 侧会同时 被 pass FET 拉低。 pass FET 具有 有限的电阻, 它会影响我们在 从器件上看到的 VOL, 原因在于出现了 IR 压降。 在了解上拉 电阻器和 FET 电阻的 所有值之后, 您就可以计算 在从器件输入端看到的电压。 从器件输入端的 电压不同于 缓冲器的 真正 VOL。 这是因为转换器的 2 侧的电压 会根据转换器 两侧的所有上拉 电阻器的电阻值 以及电路中的 所有 FET 器件的电阻 而变化。 如果以串联或 并联方式使用了 多个转换器,计算 可能会变得繁琐。 因此,我们建议使用 仿真器,例如 TI Tina。 下面我们举例说明。 三条总线被 它们的电压节点 使用两个串联 转换器隔开。 总线 1 的电压为 5 伏, 总线 2 的电压为 3.3 伏, 总线 3 的电压为 2.5 伏。 当主器件拉低时, 转换器上的两个 pass FET 都将打开, 以便将低电平 信号传递给每条总线。 在 TI Tina 中重新 绘制了示例电路。 上拉电阻器 RPU1、RPU2 和 RPU3 被设置为 1.5k 欧姆。 要了解从器件的 转换器 pass FET 电阻, 请查阅 每个相应的数据 [听不清] 规格。 主器件的下拉 FET 电阻为 130 欧姆。 转换器的 pass FET 电阻为 6.3 欧姆典型值。 根据这些参数, 我们可以将 具有代表性的电路 参数输入到 TI Tina 中, 以了解各个总线的 有效 VOL 如何变化。 结果表明,总线 1 的 VOL 电压为 740 毫伏。 总线 2 的电压为 758 毫伏。 总线 3 的电压为 765 毫伏。 I²C 标准声称, 兼容器件的输入 低电压 VIL 是 VCC 的 30%。 这意味着总线 1 的 VIL 为 1500 毫伏。 总线 2 的 VIL 为 900 毫伏。 总线 3 的 VIL 为 750 毫伏。 对于这个给定的电路, 我们可以看到 VOL3 违反了所要求的 750 毫伏 VIL3。 在这种情况下,需要更改 上拉电阻器,或者更改 转换器的 连接方式,以确保 VOL 低于 VIL, 从而确保正确运行。 由于转换器 pass FET 架构的性质, 上拉电阻器值 和 pass FET 串联 电阻显然会对 VOL 产生不利的 影响,因此必须 非常小心,以 确保接口 正确运行。 对于 VOL 也是如此, 当使用转换器时, 也会对总线的上升 时间产生不利影响。 这里是上一个 示例,但主器件 将总线拉低了。 总线 1 具有称为 CBUS1 的总线电容, 取决于主器件的 容量;转换器 1 侧的电容;以及取决于 总线 1 上 来自总线迹线 寄生效应的电容。 总线 2 具有称为 CBUS2 的总线电容, 取决于 从器件的电容; 转换器 2 侧的电容; 以及取决于 总线 2 上 来自总线迹线 寄生效应的电容。 必须注意的是, 转换器的 pass FET 已打开, CBUS1 和 CBUS2 只能与将它们 隔开的小电阻 有效并联。 我们以主器件 释放低电平为例。 随着总线电压 由于上拉电阻器 而开始上升, pass FET 的 VGS 开始下降, FET 的电阻 开始上升。 请记住,在 VGS 达到阈值电压 大约 0.7 伏 之前,总线 1 与 总线 2 之间仍然 存在电阻连接。 那时,两侧的相应 R 上拉电阻会 对两侧充电,使它们 达到各自的 VCC。 最长上升时间 由于比较复杂 而难以计算,这是因为 它涉及 CBUS1、 CBUS2、RPU1、RPU2 以及 pass FET 的 关闭特性。 幸运的是, I²C 接口 非常稳定, 而且使用转换器 不会对最长 上升时间和 VOL 产生任何类型的不利影响。 调节每个总线的 上拉电阻通常 都能够解决 总线上的问题。 转换器是一种 具有成本效益的转换 方法,只要 总线电容 不违反 所用运行模式的 I²C 标准就可以 放心使用。 为了避免上拉 电阻与总线电容之间的 这一相互依赖性, 通常可以使用缓冲器 将总线电容 与缓冲器每一侧的 相关上拉 电阻隔开。 有关 I²C 缓冲器的 更多信息, 请观看“I²C 缓冲器 概述”视频,或者 阅读“使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室 推出的 I²C 转换培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中进行转换、 如何在硬件中实施转换以及 它会对系统产生哪些影响。 I²C 使用一个 带有输入缓冲器的 开漏驱动器, 支持 双向通信。 这意味着上拉电阻器 完全控制着高电平 信号的生成。 如果您不熟悉 I²C 硬件层, 请参阅“I²C 硬件概述”视频, 了解更多 信息和培训。 在此图中,我们可以看到 两个器件具有不同的 VCC 电压, 即 VCCA1 和 VCCB2。 这意味着它们的 数字逻辑电平不同, 因此需要从一个电压电平 转换到另一个电压电平, 这一现象通常称为 电压电平不匹配。 以下是一个示例。 VCCA1 设置为 5 伏, VCCB2 设置为 3.3 伏, 那么上拉电阻器 应连接到哪个 VCC? 如果将上拉电阻器 连接到 3.3 伏的 VCCB2, 则总线上的 电压永远也 达不到 VCCA1 上的器件的 VIH, 也就是 5 伏的 70%,即 3.5 伏。 换言之,5 伏 总线中的器件 将不会看到 连接到 3.3 伏的 器件中的上拉电阻器 达到逻辑高电平。 如果将上拉电阻器 连接到 5 伏的 VCCA1, 则表明 VCC 为 3.3 伏的器件 将暴露在 高于其工作 电压的 电压中。 这样会导致 低压器件损坏, 而且 VIL 上的 电压电平仍会漂移。 很明显,必须纠正此电压 电平不匹配现象。 为此,需要使用 一个转换器,有时将其 称为电平转换器。 I²C 的转换 通常是使用 pass FET 架构 完成的,此架构可 实现电压电平隔离 并提供一种用来传递 低电平信号的方法。 不过,它无法 隔离总线电容。 我们需要看一看 pass FET 转换器的内部,以便 了解其工作原理。 在本例中,我们将 PCA9306 与 1 侧的主器件和 2 侧的从器件配合使用。 注意,它可以不 采用这种配置。 记住,I²C 是双向的, 主器件和从器件的 位置可以互换。 图中只显示了 I²C 通信所需的 两条线中的 一条,不过在 与 SCL 和 SDA 相关的 所有观察中, 物理实施方法 都是一样的。 让我们首先考虑 空闲状态,处于这种状态时, 两侧都是高电平, 转换器的任一侧 正在被拉低。 VCCA1 等于 2.5 伏, VCCB2 等于 5.0 伏。 所有 FET 都关闭。 总线的 1 侧 将被 RPU1 拉到 2.5 伏。 总线的 2 侧 将被 RPU2 上拉到 5.0 伏。 转换器上 标有 VGATE 的 pass FET 栅极具有电压。 在本例中, 它的电压为 2.5 伏。 我们以主器件 拉低为例。 当 1 侧开始拉低时, CBUS 会放电, 我们要开始产生 一个状态,以便在 设置为 2.5 伏的 VGATE 与电压为 总线电压的 VSOURCE 之间产生压差。 随着 VGS 增大并 超过这些 pass FET 的 阈值电压, 通常为 0.7 伏, 它会快速打开。 很容易看到, 当主器件拉低时, pass FET 会打开, 1 侧和 2 侧会同时 被 pass FET 拉低。 pass FET 具有 有限的电阻, 它会影响我们在 从器件上看到的 VOL, 原因在于出现了 IR 压降。 在了解上拉 电阻器和 FET 电阻的 所有值之后, 您就可以计算 在从器件输入端看到的电压。 从器件输入端的 电压不同于 缓冲器的 真正 VOL。 这是因为转换器的 2 侧的电压 会根据转换器 两侧的所有上拉 电阻器的电阻值 以及电路中的 所有 FET 器件的电阻 而变化。 如果以串联或 并联方式使用了 多个转换器,计算 可能会变得繁琐。 因此,我们建议使用 仿真器,例如 TI Tina。 下面我们举例说明。 三条总线被 它们的电压节点 使用两个串联 转换器隔开。 总线 1 的电压为 5 伏, 总线 2 的电压为 3.3 伏, 总线 3 的电压为 2.5 伏。 当主器件拉低时, 转换器上的两个 pass FET 都将打开, 以便将低电平 信号传递给每条总线。 在 TI Tina 中重新 绘制了示例电路。 上拉电阻器 RPU1、RPU2 和 RPU3 被设置为 1.5k 欧姆。 要了解从器件的 转换器 pass FET 电阻, 请查阅 每个相应的数据 [听不清] 规格。 主器件的下拉 FET 电阻为 130 欧姆。 转换器的 pass FET 电阻为 6.3 欧姆典型值。 根据这些参数, 我们可以将 具有代表性的电路 参数输入到 TI Tina 中, 以了解各个总线的 有效 VOL 如何变化。 结果表明,总线 1 的 VOL 电压为 740 毫伏。 总线 2 的电压为 758 毫伏。 总线 3 的电压为 765 毫伏。 I²C 标准声称, 兼容器件的输入 低电压 VIL 是 VCC 的 30%。 这意味着总线 1 的 VIL 为 1500 毫伏。 总线 2 的 VIL 为 900 毫伏。 总线 3 的 VIL 为 750 毫伏。 对于这个给定的电路, 我们可以看到 VOL3 违反了所要求的 750 毫伏 VIL3。 在这种情况下,需要更改 上拉电阻器,或者更改 转换器的 连接方式,以确保 VOL 低于 VIL, 从而确保正确运行。 由于转换器 pass FET 架构的性质, 上拉电阻器值 和 pass FET 串联 电阻显然会对 VOL 产生不利的 影响,因此必须 非常小心,以 确保接口 正确运行。 对于 VOL 也是如此, 当使用转换器时, 也会对总线的上升 时间产生不利影响。 这里是上一个 示例,但主器件 将总线拉低了。 总线 1 具有称为 CBUS1 的总线电容, 取决于主器件的 容量;转换器 1 侧的电容;以及取决于 总线 1 上 来自总线迹线 寄生效应的电容。 总线 2 具有称为 CBUS2 的总线电容, 取决于 从器件的电容; 转换器 2 侧的电容; 以及取决于 总线 2 上 来自总线迹线 寄生效应的电容。 必须注意的是, 转换器的 pass FET 已打开, CBUS1 和 CBUS2 只能与将它们 隔开的小电阻 有效并联。 我们以主器件 释放低电平为例。 随着总线电压 由于上拉电阻器 而开始上升, pass FET 的 VGS 开始下降, FET 的电阻 开始上升。 请记住,在 VGS 达到阈值电压 大约 0.7 伏 之前,总线 1 与 总线 2 之间仍然 存在电阻连接。 那时,两侧的相应 R 上拉电阻会 对两侧充电,使它们 达到各自的 VCC。 最长上升时间 由于比较复杂 而难以计算,这是因为 它涉及 CBUS1、 CBUS2、RPU1、RPU2 以及 pass FET 的 关闭特性。 幸运的是, I²C 接口 非常稳定, 而且使用转换器 不会对最长 上升时间和 VOL 产生任何类型的不利影响。 调节每个总线的 上拉电阻通常 都能够解决 总线上的问题。 转换器是一种 具有成本效益的转换 方法,只要 总线电容 不违反 所用运行模式的 I²C 标准就可以 放心使用。 为了避免上拉 电阻与总线电容之间的 这一相互依赖性, 通常可以使用缓冲器 将总线电容 与缓冲器每一侧的 相关上拉 电阻隔开。 有关 I²C 缓冲器的 更多信息, 请观看“I²C 缓冲器 概述”视频,或者 阅读“使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室

推出的 I²C 转换培训视频。

在本视频中,我们 将讨论是否需要

在 I²C 系统中进行转换、 如何在硬件中实施转换以及

它会对系统产生哪些影响。

I²C 使用一个 带有输入缓冲器的

开漏驱动器, 支持

双向通信。

这意味着上拉电阻器 完全控制着高电平

信号的生成。

如果您不熟悉 I²C 硬件层,

请参阅“I²C 硬件概述”视频,

了解更多 信息和培训。

在此图中,我们可以看到 两个器件具有不同的 VCC 电压,

即 VCCA1 和 VCCB2。

这意味着它们的 数字逻辑电平不同,

因此需要从一个电压电平 转换到另一个电压电平,

这一现象通常称为 电压电平不匹配。

以下是一个示例。

VCCA1 设置为 5 伏,

VCCB2 设置为 3.3 伏, 那么上拉电阻器

应连接到哪个 VCC?

如果将上拉电阻器 连接到 3.3 伏的 VCCB2,

则总线上的 电压永远也

达不到 VCCA1 上的器件的 VIH,

也就是 5 伏的 70%,即 3.5 伏。

换言之,5 伏 总线中的器件

将不会看到 连接到 3.3 伏的

器件中的上拉电阻器 达到逻辑高电平。

如果将上拉电阻器 连接到 5 伏的 VCCA1,

则表明 VCC 为 3.3 伏的器件

将暴露在 高于其工作

电压的 电压中。

这样会导致 低压器件损坏,

而且 VIL 上的 电压电平仍会漂移。

很明显,必须纠正此电压 电平不匹配现象。

为此,需要使用 一个转换器,有时将其

称为电平转换器。

I²C 的转换 通常是使用

pass FET 架构 完成的,此架构可

实现电压电平隔离 并提供一种用来传递

低电平信号的方法。

不过,它无法 隔离总线电容。

我们需要看一看 pass FET 转换器的内部,以便

了解其工作原理。

在本例中,我们将 PCA9306 与 1 侧的主器件和

2 侧的从器件配合使用。

注意,它可以不 采用这种配置。

记住,I²C 是双向的,

主器件和从器件的 位置可以互换。

图中只显示了 I²C 通信所需的

两条线中的 一条,不过在

与 SCL 和 SDA 相关的 所有观察中,

物理实施方法 都是一样的。

让我们首先考虑 空闲状态,处于这种状态时,

两侧都是高电平, 转换器的任一侧

正在被拉低。

VCCA1 等于 2.5 伏, VCCB2 等于 5.0 伏。

所有 FET 都关闭。

总线的 1 侧 将被 RPU1 拉到 2.5 伏。

总线的 2 侧 将被 RPU2 上拉到 5.0 伏。

转换器上 标有 VGATE 的

pass FET 栅极具有电压。

在本例中, 它的电压为 2.5 伏。

我们以主器件 拉低为例。

当 1 侧开始拉低时, CBUS 会放电,

我们要开始产生 一个状态,以便在

设置为 2.5 伏的 VGATE 与电压为

总线电压的 VSOURCE 之间产生压差。

随着 VGS 增大并 超过这些 pass FET 的

阈值电压, 通常为 0.7 伏,

它会快速打开。

很容易看到, 当主器件拉低时,

pass FET 会打开, 1 侧和 2 侧会同时

被 pass FET 拉低。

pass FET 具有 有限的电阻,

它会影响我们在 从器件上看到的 VOL,

原因在于出现了 IR 压降。

在了解上拉 电阻器和 FET 电阻的

所有值之后, 您就可以计算

在从器件输入端看到的电压。

从器件输入端的 电压不同于

缓冲器的 真正 VOL。

这是因为转换器的 2 侧的电压

会根据转换器 两侧的所有上拉

电阻器的电阻值 以及电路中的

所有 FET 器件的电阻 而变化。

如果以串联或 并联方式使用了

多个转换器,计算 可能会变得繁琐。

因此,我们建议使用 仿真器,例如 TI Tina。

下面我们举例说明。

三条总线被 它们的电压节点

使用两个串联 转换器隔开。

总线 1 的电压为 5 伏, 总线 2 的电压为 3.3 伏,

总线 3 的电压为 2.5 伏。

当主器件拉低时, 转换器上的两个

pass FET 都将打开, 以便将低电平

信号传递给每条总线。

在 TI Tina 中重新 绘制了示例电路。

上拉电阻器 RPU1、RPU2 和 RPU3 被设置为 1.5k 欧姆。

要了解从器件的 转换器 pass

FET 电阻, 请查阅

每个相应的数据 [听不清] 规格。

主器件的下拉 FET 电阻为 130 欧姆。

转换器的 pass FET 电阻为 6.3 欧姆典型值。

根据这些参数, 我们可以将

具有代表性的电路 参数输入到 TI Tina 中,

以了解各个总线的 有效 VOL 如何变化。

结果表明,总线 1 的 VOL 电压为 740 毫伏。

总线 2 的电压为 758 毫伏。

总线 3 的电压为 765 毫伏。

I²C 标准声称, 兼容器件的输入

低电压 VIL 是 VCC 的 30%。

这意味着总线 1 的 VIL 为 1500 毫伏。

总线 2 的 VIL 为 900 毫伏。

总线 3 的 VIL 为 750 毫伏。

对于这个给定的电路, 我们可以看到 VOL3

违反了所要求的 750 毫伏 VIL3。

在这种情况下,需要更改 上拉电阻器,或者更改

转换器的 连接方式,以确保

VOL 低于 VIL, 从而确保正确运行。

由于转换器 pass FET 架构的性质,

上拉电阻器值 和 pass FET 串联

电阻显然会对 VOL 产生不利的

影响,因此必须 非常小心,以

确保接口 正确运行。

对于 VOL 也是如此, 当使用转换器时,

也会对总线的上升 时间产生不利影响。

这里是上一个 示例,但主器件

将总线拉低了。

总线 1 具有称为 CBUS1 的总线电容,

取决于主器件的 容量;转换器

1 侧的电容;以及取决于

总线 1 上 来自总线迹线

寄生效应的电容。

总线 2 具有称为 CBUS2 的总线电容,

取决于 从器件的电容;

转换器 2 侧的电容; 以及取决于

总线 2 上 来自总线迹线

寄生效应的电容。

必须注意的是, 转换器的 pass FET 已打开,

CBUS1 和 CBUS2 只能与将它们

隔开的小电阻 有效并联。

我们以主器件 释放低电平为例。

随着总线电压 由于上拉电阻器

而开始上升, pass FET 的 VGS

开始下降, FET 的电阻

开始上升。

请记住,在 VGS 达到阈值电压

大约 0.7 伏 之前,总线 1 与

总线 2 之间仍然 存在电阻连接。

那时,两侧的相应 R 上拉电阻会

对两侧充电,使它们 达到各自的 VCC。

最长上升时间 由于比较复杂

而难以计算,这是因为 它涉及 CBUS1、

CBUS2、RPU1、RPU2 以及 pass FET 的

关闭特性。

幸运的是, I²C 接口

非常稳定, 而且使用转换器

不会对最长 上升时间和 VOL

产生任何类型的不利影响。

调节每个总线的 上拉电阻通常

都能够解决 总线上的问题。

转换器是一种 具有成本效益的转换

方法,只要 总线电容

不违反 所用运行模式的

I²C 标准就可以 放心使用。

为了避免上拉 电阻与总线电容之间的

这一相互依赖性, 通常可以使用缓冲器

将总线电容 与缓冲器每一侧的

相关上拉 电阻隔开。

有关 I²C 缓冲器的 更多信息,

请观看“I²C 缓冲器 概述”视频,或者

阅读“使用 I²C 缓冲器的

原因、时机和方法” 应用报告。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室 推出的 I²C 转换培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中进行转换、 如何在硬件中实施转换以及 它会对系统产生哪些影响。 I²C 使用一个 带有输入缓冲器的 开漏驱动器, 支持 双向通信。 这意味着上拉电阻器 完全控制着高电平 信号的生成。 如果您不熟悉 I²C 硬件层, 请参阅“I²C 硬件概述”视频, 了解更多 信息和培训。 在此图中,我们可以看到 两个器件具有不同的 VCC 电压, 即 VCCA1 和 VCCB2。 这意味着它们的 数字逻辑电平不同, 因此需要从一个电压电平 转换到另一个电压电平, 这一现象通常称为 电压电平不匹配。 以下是一个示例。 VCCA1 设置为 5 伏, VCCB2 设置为 3.3 伏, 那么上拉电阻器 应连接到哪个 VCC? 如果将上拉电阻器 连接到 3.3 伏的 VCCB2, 则总线上的 电压永远也 达不到 VCCA1 上的器件的 VIH, 也就是 5 伏的 70%,即 3.5 伏。 换言之,5 伏 总线中的器件 将不会看到 连接到 3.3 伏的 器件中的上拉电阻器 达到逻辑高电平。 如果将上拉电阻器 连接到 5 伏的 VCCA1, 则表明 VCC 为 3.3 伏的器件 将暴露在 高于其工作 电压的 电压中。 这样会导致 低压器件损坏, 而且 VIL 上的 电压电平仍会漂移。 很明显,必须纠正此电压 电平不匹配现象。 为此,需要使用 一个转换器,有时将其 称为电平转换器。 I²C 的转换 通常是使用 pass FET 架构 完成的,此架构可 实现电压电平隔离 并提供一种用来传递 低电平信号的方法。 不过,它无法 隔离总线电容。 我们需要看一看 pass FET 转换器的内部,以便 了解其工作原理。 在本例中,我们将 PCA9306 与 1 侧的主器件和 2 侧的从器件配合使用。 注意,它可以不 采用这种配置。 记住,I²C 是双向的, 主器件和从器件的 位置可以互换。 图中只显示了 I²C 通信所需的 两条线中的 一条,不过在 与 SCL 和 SDA 相关的 所有观察中, 物理实施方法 都是一样的。 让我们首先考虑 空闲状态,处于这种状态时, 两侧都是高电平, 转换器的任一侧 正在被拉低。 VCCA1 等于 2.5 伏, VCCB2 等于 5.0 伏。 所有 FET 都关闭。 总线的 1 侧 将被 RPU1 拉到 2.5 伏。 总线的 2 侧 将被 RPU2 上拉到 5.0 伏。 转换器上 标有 VGATE 的 pass FET 栅极具有电压。 在本例中, 它的电压为 2.5 伏。 我们以主器件 拉低为例。 当 1 侧开始拉低时, CBUS 会放电, 我们要开始产生 一个状态,以便在 设置为 2.5 伏的 VGATE 与电压为 总线电压的 VSOURCE 之间产生压差。 随着 VGS 增大并 超过这些 pass FET 的 阈值电压, 通常为 0.7 伏, 它会快速打开。 很容易看到, 当主器件拉低时, pass FET 会打开, 1 侧和 2 侧会同时 被 pass FET 拉低。 pass FET 具有 有限的电阻, 它会影响我们在 从器件上看到的 VOL, 原因在于出现了 IR 压降。 在了解上拉 电阻器和 FET 电阻的 所有值之后, 您就可以计算 在从器件输入端看到的电压。 从器件输入端的 电压不同于 缓冲器的 真正 VOL。 这是因为转换器的 2 侧的电压 会根据转换器 两侧的所有上拉 电阻器的电阻值 以及电路中的 所有 FET 器件的电阻 而变化。 如果以串联或 并联方式使用了 多个转换器,计算 可能会变得繁琐。 因此,我们建议使用 仿真器,例如 TI Tina。 下面我们举例说明。 三条总线被 它们的电压节点 使用两个串联 转换器隔开。 总线 1 的电压为 5 伏, 总线 2 的电压为 3.3 伏, 总线 3 的电压为 2.5 伏。 当主器件拉低时, 转换器上的两个 pass FET 都将打开, 以便将低电平 信号传递给每条总线。 在 TI Tina 中重新 绘制了示例电路。 上拉电阻器 RPU1、RPU2 和 RPU3 被设置为 1.5k 欧姆。 要了解从器件的 转换器 pass FET 电阻, 请查阅 每个相应的数据 [听不清] 规格。 主器件的下拉 FET 电阻为 130 欧姆。 转换器的 pass FET 电阻为 6.3 欧姆典型值。 根据这些参数, 我们可以将 具有代表性的电路 参数输入到 TI Tina 中, 以了解各个总线的 有效 VOL 如何变化。 结果表明,总线 1 的 VOL 电压为 740 毫伏。 总线 2 的电压为 758 毫伏。 总线 3 的电压为 765 毫伏。 I²C 标准声称, 兼容器件的输入 低电压 VIL 是 VCC 的 30%。 这意味着总线 1 的 VIL 为 1500 毫伏。 总线 2 的 VIL 为 900 毫伏。 总线 3 的 VIL 为 750 毫伏。 对于这个给定的电路, 我们可以看到 VOL3 违反了所要求的 750 毫伏 VIL3。 在这种情况下,需要更改 上拉电阻器,或者更改 转换器的 连接方式,以确保 VOL 低于 VIL, 从而确保正确运行。 由于转换器 pass FET 架构的性质, 上拉电阻器值 和 pass FET 串联 电阻显然会对 VOL 产生不利的 影响,因此必须 非常小心,以 确保接口 正确运行。 对于 VOL 也是如此, 当使用转换器时, 也会对总线的上升 时间产生不利影响。 这里是上一个 示例,但主器件 将总线拉低了。 总线 1 具有称为 CBUS1 的总线电容, 取决于主器件的 容量;转换器 1 侧的电容;以及取决于 总线 1 上 来自总线迹线 寄生效应的电容。 总线 2 具有称为 CBUS2 的总线电容, 取决于 从器件的电容; 转换器 2 侧的电容; 以及取决于 总线 2 上 来自总线迹线 寄生效应的电容。 必须注意的是, 转换器的 pass FET 已打开, CBUS1 和 CBUS2 只能与将它们 隔开的小电阻 有效并联。 我们以主器件 释放低电平为例。 随着总线电压 由于上拉电阻器 而开始上升, pass FET 的 VGS 开始下降, FET 的电阻 开始上升。 请记住,在 VGS 达到阈值电压 大约 0.7 伏 之前,总线 1 与 总线 2 之间仍然 存在电阻连接。 那时,两侧的相应 R 上拉电阻会 对两侧充电,使它们 达到各自的 VCC。 最长上升时间 由于比较复杂 而难以计算,这是因为 它涉及 CBUS1、 CBUS2、RPU1、RPU2 以及 pass FET 的 关闭特性。 幸运的是, I²C 接口 非常稳定, 而且使用转换器 不会对最长 上升时间和 VOL 产生任何类型的不利影响。 调节每个总线的 上拉电阻通常 都能够解决 总线上的问题。 转换器是一种 具有成本效益的转换 方法,只要 总线电容 不违反 所用运行模式的 I²C 标准就可以 放心使用。 为了避免上拉 电阻与总线电容之间的 这一相互依赖性, 通常可以使用缓冲器 将总线电容 与缓冲器每一侧的 相关上拉 电阻隔开。 有关 I²C 缓冲器的 更多信息, 请观看“I²C 缓冲器 概述”视频,或者 阅读“使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室

推出的 I²C 转换培训视频。

在本视频中,我们 将讨论是否需要

在 I²C 系统中进行转换、 如何在硬件中实施转换以及

它会对系统产生哪些影响。

I²C 使用一个 带有输入缓冲器的

开漏驱动器, 支持

双向通信。

这意味着上拉电阻器 完全控制着高电平

信号的生成。

如果您不熟悉 I²C 硬件层,

请参阅“I²C 硬件概述”视频,

了解更多 信息和培训。

在此图中,我们可以看到 两个器件具有不同的 VCC 电压,

即 VCCA1 和 VCCB2。

这意味着它们的 数字逻辑电平不同,

因此需要从一个电压电平 转换到另一个电压电平,

这一现象通常称为 电压电平不匹配。

以下是一个示例。

VCCA1 设置为 5 伏,

VCCB2 设置为 3.3 伏, 那么上拉电阻器

应连接到哪个 VCC?

如果将上拉电阻器 连接到 3.3 伏的 VCCB2,

则总线上的 电压永远也

达不到 VCCA1 上的器件的 VIH,

也就是 5 伏的 70%,即 3.5 伏。

换言之,5 伏 总线中的器件

将不会看到 连接到 3.3 伏的

器件中的上拉电阻器 达到逻辑高电平。

如果将上拉电阻器 连接到 5 伏的 VCCA1,

则表明 VCC 为 3.3 伏的器件

将暴露在 高于其工作

电压的 电压中。

这样会导致 低压器件损坏,

而且 VIL 上的 电压电平仍会漂移。

很明显,必须纠正此电压 电平不匹配现象。

为此,需要使用 一个转换器,有时将其

称为电平转换器。

I²C 的转换 通常是使用

pass FET 架构 完成的,此架构可

实现电压电平隔离 并提供一种用来传递

低电平信号的方法。

不过,它无法 隔离总线电容。

我们需要看一看 pass FET 转换器的内部,以便

了解其工作原理。

在本例中,我们将 PCA9306 与 1 侧的主器件和

2 侧的从器件配合使用。

注意,它可以不 采用这种配置。

记住,I²C 是双向的,

主器件和从器件的 位置可以互换。

图中只显示了 I²C 通信所需的

两条线中的 一条,不过在

与 SCL 和 SDA 相关的 所有观察中,

物理实施方法 都是一样的。

让我们首先考虑 空闲状态,处于这种状态时,

两侧都是高电平, 转换器的任一侧

正在被拉低。

VCCA1 等于 2.5 伏, VCCB2 等于 5.0 伏。

所有 FET 都关闭。

总线的 1 侧 将被 RPU1 拉到 2.5 伏。

总线的 2 侧 将被 RPU2 上拉到 5.0 伏。

转换器上 标有 VGATE 的

pass FET 栅极具有电压。

在本例中, 它的电压为 2.5 伏。

我们以主器件 拉低为例。

当 1 侧开始拉低时, CBUS 会放电,

我们要开始产生 一个状态,以便在

设置为 2.5 伏的 VGATE 与电压为

总线电压的 VSOURCE 之间产生压差。

随着 VGS 增大并 超过这些 pass FET 的

阈值电压, 通常为 0.7 伏,

它会快速打开。

很容易看到, 当主器件拉低时,

pass FET 会打开, 1 侧和 2 侧会同时

被 pass FET 拉低。

pass FET 具有 有限的电阻,

它会影响我们在 从器件上看到的 VOL,

原因在于出现了 IR 压降。

在了解上拉 电阻器和 FET 电阻的

所有值之后, 您就可以计算

在从器件输入端看到的电压。

从器件输入端的 电压不同于

缓冲器的 真正 VOL。

这是因为转换器的 2 侧的电压

会根据转换器 两侧的所有上拉

电阻器的电阻值 以及电路中的

所有 FET 器件的电阻 而变化。

如果以串联或 并联方式使用了

多个转换器,计算 可能会变得繁琐。

因此,我们建议使用 仿真器,例如 TI Tina。

下面我们举例说明。

三条总线被 它们的电压节点

使用两个串联 转换器隔开。

总线 1 的电压为 5 伏, 总线 2 的电压为 3.3 伏,

总线 3 的电压为 2.5 伏。

当主器件拉低时, 转换器上的两个

pass FET 都将打开, 以便将低电平

信号传递给每条总线。

在 TI Tina 中重新 绘制了示例电路。

上拉电阻器 RPU1、RPU2 和 RPU3 被设置为 1.5k 欧姆。

要了解从器件的 转换器 pass

FET 电阻, 请查阅

每个相应的数据 [听不清] 规格。

主器件的下拉 FET 电阻为 130 欧姆。

转换器的 pass FET 电阻为 6.3 欧姆典型值。

根据这些参数, 我们可以将

具有代表性的电路 参数输入到 TI Tina 中,

以了解各个总线的 有效 VOL 如何变化。

结果表明,总线 1 的 VOL 电压为 740 毫伏。

总线 2 的电压为 758 毫伏。

总线 3 的电压为 765 毫伏。

I²C 标准声称, 兼容器件的输入

低电压 VIL 是 VCC 的 30%。

这意味着总线 1 的 VIL 为 1500 毫伏。

总线 2 的 VIL 为 900 毫伏。

总线 3 的 VIL 为 750 毫伏。

对于这个给定的电路, 我们可以看到 VOL3

违反了所要求的 750 毫伏 VIL3。

在这种情况下,需要更改 上拉电阻器,或者更改

转换器的 连接方式,以确保

VOL 低于 VIL, 从而确保正确运行。

由于转换器 pass FET 架构的性质,

上拉电阻器值 和 pass FET 串联

电阻显然会对 VOL 产生不利的

影响,因此必须 非常小心,以

确保接口 正确运行。

对于 VOL 也是如此, 当使用转换器时,

也会对总线的上升 时间产生不利影响。

这里是上一个 示例,但主器件

将总线拉低了。

总线 1 具有称为 CBUS1 的总线电容,

取决于主器件的 容量;转换器

1 侧的电容;以及取决于

总线 1 上 来自总线迹线

寄生效应的电容。

总线 2 具有称为 CBUS2 的总线电容,

取决于 从器件的电容;

转换器 2 侧的电容; 以及取决于

总线 2 上 来自总线迹线

寄生效应的电容。

必须注意的是, 转换器的 pass FET 已打开,

CBUS1 和 CBUS2 只能与将它们

隔开的小电阻 有效并联。

我们以主器件 释放低电平为例。

随着总线电压 由于上拉电阻器

而开始上升, pass FET 的 VGS

开始下降, FET 的电阻

开始上升。

请记住,在 VGS 达到阈值电压

大约 0.7 伏 之前,总线 1 与

总线 2 之间仍然 存在电阻连接。

那时,两侧的相应 R 上拉电阻会

对两侧充电,使它们 达到各自的 VCC。

最长上升时间 由于比较复杂

而难以计算,这是因为 它涉及 CBUS1、

CBUS2、RPU1、RPU2 以及 pass FET 的

关闭特性。

幸运的是, I²C 接口

非常稳定, 而且使用转换器

不会对最长 上升时间和 VOL

产生任何类型的不利影响。

调节每个总线的 上拉电阻通常

都能够解决 总线上的问题。

转换器是一种 具有成本效益的转换

方法,只要 总线电容

不违反 所用运行模式的

I²C 标准就可以 放心使用。

为了避免上拉 电阻与总线电容之间的

这一相互依赖性, 通常可以使用缓冲器

将总线电容 与缓冲器每一侧的

相关上拉 电阻隔开。

有关 I²C 缓冲器的 更多信息,

请观看“I²C 缓冲器 概述”视频,或者

阅读“使用 I²C 缓冲器的

原因、时机和方法” 应用报告。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频

手机看

扫码用手机观看

视频简介

视频简介

6.3 TI 高精度实验室 -I2C:转换器概述

所属课程:TI 高精度实验室 - I2C

发布时间:2020.01.13

视频集数:4

本节视频时长:00:08:46

了解如何使用I2C IC进行设计。 TI Precision Labs(TIPL)是模拟信号链设计人员最全面的在线教室。该 接口系列 提供了通过工业,汽车和多种应用领域常用协议的技术培训。 从I2C系列开始,以了解I2C标准,数据协议的基础知识和所使用的物理信号,以及如何使用转换器和缓冲设备解决应用程序级问题。

未学习 6.1 TI 高精度实验室 -I2C:硬件概述

未学习 6.1 TI 高精度实验室 -I2C:硬件概述

未学习 6.2 TI 高精度实验室 -I2C:协议概述

未学习 6.2 TI 高精度实验室 -I2C:协议概述

未学习 6.3 TI 高精度实验室 -I2C:转换器概述

未学习 6.3 TI 高精度实验室 -I2C:转换器概述

未学习 6.4 TI 高精度实验室 -I2C:缓冲器概述

未学习 6.4 TI 高精度实验室 -I2C:缓冲器概述

视频简介

视频简介