6.4 TI 高精度实验室 -I2C:缓冲器概述

Loading the player...

将在30s后自动为您播放下一课程

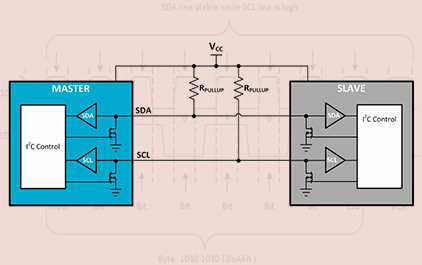

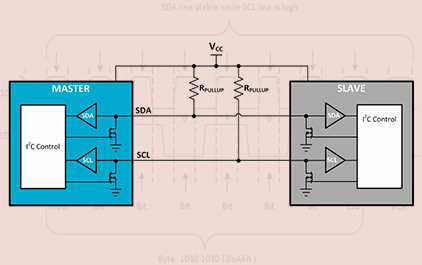

大家好,欢迎观看 高精度实验室 推出的 I²C 缓冲器培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中使用缓冲器、 如何在硬件中实施缓冲器以及 它会对系统产生哪些影响。 I²C 总线 是 5 向接口, 利用一个称为 主器件的控制器 与一个或多个从器件 进行通信。 I²C 总线上的 每个器件都有 一个特定的器件 地址,用于区分 同一个 I²C 总线上的其他器件。 物理 I²C 接口由 串行时钟线 SCL 和 串行数据线 SDA 组成。 SDA 和 SCL 线都 必须通过上拉电阻器 连接到 VCC。 上拉电阻器的大小由 总线上的电容 数量以及 I²C 总线上使用的 最大 VLL 决定。 必须注意的是, 总线上的电容 C BUS 包括 PCB 电容、主器件的 电容以及每个 从器件的电容。 I²C 接口的 SDA 和 SCL 线 都有自己的总线以及 可能不同的 单独总线电容, 即 C Bus。 为了简单起见, 本视频只讨论一条总线。 但内容与 SCL 和 SDA 线都相关。 这一条总线既 代表 SDA,也代表 SCL。 I²C 接口具有 不同的运行模式, 取决于通信的 最高时钟频率, 此频率称为 f CLOCK MAX。 本视频将 介绍三种模式: 标准模式、快速 模式和超快速模式。 I²C 标准为每种 运行模式定义了 多个参数,但 本视频中只 定义了其中四个 最重要的参数,即 C BUS、t RISE MAX、V OL MAX 和 I OL MIN。 对于标准模式, f CLOCK MAX 为 100 千赫兹、 C Bus MAX 为 400 皮法、 t RISE MAX 为 1000 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于快速模式, f CLOCK MAX 为 400 千赫兹、 C BUS MAX 为 400 皮法、 t RISE MAX 为 300 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于超快速模式, f CLOCK MAX 为 1000 千赫兹、 C BUS MAX 为 550 皮法、 t RISE MAX 为 120 纳秒、 V OL 为 0.4 伏、 I OL 为 20 毫安。 这些参数用于 选择上拉电阻器值 和确定是否需要 在系统中使用缓冲器 以满足 I²C 标准。 SCL 和 SDA 的最长 上升时间规格 t RISE MAX 由上拉和 C BUS 所创建的 RC 时间常数控制, 被定义为从 VIO 过渡到 VIH 时 花费的时间。 给定运行模式的 上拉电阻器的 最大大小 由公式 1 决定, 其中的 t RISE 绝不能超过 C BUS 中的任何 给定总线电容, t RISE MAX 绝不能 超过任何给定 总线电容 C BUS, 这样就设置了 上拉电阻值的上限。 最小上拉电阻 R Pullup Min 由 VOL Max 定义,VOL Max 是 跨下拉电阻 产生的电压, 当打开时,会有 一个指定的 IOL Min 经过它。 这样即可有效地 定义总线上的 任何 FET 的最大 RDS。 了解 VCC、 VOL MAX 和 IOL MIN 之后, 我们便可定义 最小上拉电阻, 在为确保绝不超过 VOL 时需要使用此值。 参见公式 2。 它限定了上拉 电阻器值的下限。 I²C 接口 可支持 总线上的数百个 从器件,此数量只取决于 可用从器件地址 的数量。 不过,很明显, 如果每个器件 都有高达 10 皮法的电容, 则运行模式的 给定总线上的从器件 数量将受到 C BUS MAX 的限制。 这意味着需要 采用某种方法 将一个总线及其总线 电容拆分到多个总线中, 以满足 I²C 时序 要求。 幸运的是,I²C 缓冲器正是为此而生。 它们使用一个总线 电容为 C BUS 的总线 并将其拆分和 隔离到两个总线中: 电容 C BUS 1 和 C BUS 2。 要拆分总线电容, 需要使用 单独的上拉电阻器在 每个总线上生成 逻辑高电平,这样就 需要使用 R 上拉 1 和 R 上拉 2。 总线 1 和总线 2 都必须遵循 所用运行模式的 t RISE MAX、C BUS MAX、VOL MAX 和 IOL MIN 的 I²C 标准。 有关实施、选择 和使用 I²C 缓冲器的 更多信息,请阅读 “使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室 推出的 I²C 缓冲器培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中使用缓冲器、 如何在硬件中实施缓冲器以及 它会对系统产生哪些影响。 I²C 总线 是 5 向接口, 利用一个称为 主器件的控制器 与一个或多个从器件 进行通信。 I²C 总线上的 每个器件都有 一个特定的器件 地址,用于区分 同一个 I²C 总线上的其他器件。 物理 I²C 接口由 串行时钟线 SCL 和 串行数据线 SDA 组成。 SDA 和 SCL 线都 必须通过上拉电阻器 连接到 VCC。 上拉电阻器的大小由 总线上的电容 数量以及 I²C 总线上使用的 最大 VLL 决定。 必须注意的是, 总线上的电容 C BUS 包括 PCB 电容、主器件的 电容以及每个 从器件的电容。 I²C 接口的 SDA 和 SCL 线 都有自己的总线以及 可能不同的 单独总线电容, 即 C Bus。 为了简单起见, 本视频只讨论一条总线。 但内容与 SCL 和 SDA 线都相关。 这一条总线既 代表 SDA,也代表 SCL。 I²C 接口具有 不同的运行模式, 取决于通信的 最高时钟频率, 此频率称为 f CLOCK MAX。 本视频将 介绍三种模式: 标准模式、快速 模式和超快速模式。 I²C 标准为每种 运行模式定义了 多个参数,但 本视频中只 定义了其中四个 最重要的参数,即 C BUS、t RISE MAX、V OL MAX 和 I OL MIN。 对于标准模式, f CLOCK MAX 为 100 千赫兹、 C Bus MAX 为 400 皮法、 t RISE MAX 为 1000 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于快速模式, f CLOCK MAX 为 400 千赫兹、 C BUS MAX 为 400 皮法、 t RISE MAX 为 300 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于超快速模式, f CLOCK MAX 为 1000 千赫兹、 C BUS MAX 为 550 皮法、 t RISE MAX 为 120 纳秒、 V OL 为 0.4 伏、 I OL 为 20 毫安。 这些参数用于 选择上拉电阻器值 和确定是否需要 在系统中使用缓冲器 以满足 I²C 标准。 SCL 和 SDA 的最长 上升时间规格 t RISE MAX 由上拉和 C BUS 所创建的 RC 时间常数控制, 被定义为从 VIO 过渡到 VIH 时 花费的时间。 给定运行模式的 上拉电阻器的 最大大小 由公式 1 决定, 其中的 t RISE 绝不能超过 C BUS 中的任何 给定总线电容, t RISE MAX 绝不能 超过任何给定 总线电容 C BUS, 这样就设置了 上拉电阻值的上限。 最小上拉电阻 R Pullup Min 由 VOL Max 定义,VOL Max 是 跨下拉电阻 产生的电压, 当打开时,会有 一个指定的 IOL Min 经过它。 这样即可有效地 定义总线上的 任何 FET 的最大 RDS。 了解 VCC、 VOL MAX 和 IOL MIN 之后, 我们便可定义 最小上拉电阻, 在为确保绝不超过 VOL 时需要使用此值。 参见公式 2。 它限定了上拉 电阻器值的下限。 I²C 接口 可支持 总线上的数百个 从器件,此数量只取决于 可用从器件地址 的数量。 不过,很明显, 如果每个器件 都有高达 10 皮法的电容, 则运行模式的 给定总线上的从器件 数量将受到 C BUS MAX 的限制。 这意味着需要 采用某种方法 将一个总线及其总线 电容拆分到多个总线中, 以满足 I²C 时序 要求。 幸运的是,I²C 缓冲器正是为此而生。 它们使用一个总线 电容为 C BUS 的总线 并将其拆分和 隔离到两个总线中: 电容 C BUS 1 和 C BUS 2。 要拆分总线电容, 需要使用 单独的上拉电阻器在 每个总线上生成 逻辑高电平,这样就 需要使用 R 上拉 1 和 R 上拉 2。 总线 1 和总线 2 都必须遵循 所用运行模式的 t RISE MAX、C BUS MAX、VOL MAX 和 IOL MIN 的 I²C 标准。 有关实施、选择 和使用 I²C 缓冲器的 更多信息,请阅读 “使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室

推出的 I²C 缓冲器培训视频。

在本视频中,我们 将讨论是否需要

在 I²C 系统中使用缓冲器、 如何在硬件中实施缓冲器以及

它会对系统产生哪些影响。

I²C 总线 是 5 向接口,

利用一个称为 主器件的控制器

与一个或多个从器件

进行通信。

I²C 总线上的 每个器件都有

一个特定的器件 地址,用于区分

同一个 I²C 总线上的其他器件。

物理 I²C 接口由

串行时钟线 SCL 和

串行数据线 SDA 组成。

SDA 和 SCL 线都 必须通过上拉电阻器

连接到 VCC。

上拉电阻器的大小由

总线上的电容 数量以及 I²C

总线上使用的 最大 VLL 决定。

必须注意的是, 总线上的电容 C BUS

包括 PCB 电容、主器件的

电容以及每个 从器件的电容。

I²C 接口的 SDA 和 SCL 线

都有自己的总线以及

可能不同的 单独总线电容,

即 C Bus。

为了简单起见, 本视频只讨论一条总线。

但内容与 SCL 和 SDA 线都相关。

这一条总线既 代表 SDA,也代表 SCL。

I²C 接口具有 不同的运行模式,

取决于通信的 最高时钟频率,

此频率称为 f CLOCK MAX。

本视频将 介绍三种模式:

标准模式、快速 模式和超快速模式。

I²C 标准为每种 运行模式定义了

多个参数,但 本视频中只

定义了其中四个 最重要的参数,即 C BUS、t RISE

MAX、V OL MAX 和 I OL MIN。

对于标准模式, f CLOCK MAX 为 100 千赫兹、

C Bus MAX 为 400 皮法、 t RISE MAX 为 1000 纳秒、

V OL 为 0.4 伏、 I OL 为 3 毫安。

对于快速模式, f CLOCK MAX 为 400 千赫兹、

C BUS MAX 为 400 皮法、 t RISE MAX 为 300 纳秒、

V OL 为 0.4 伏、 I OL 为 3 毫安。

对于超快速模式, f CLOCK MAX 为 1000 千赫兹、

C BUS MAX 为 550 皮法、 t RISE MAX 为 120 纳秒、

V OL 为 0.4 伏、 I OL 为 20 毫安。

这些参数用于 选择上拉电阻器值

和确定是否需要 在系统中使用缓冲器

以满足 I²C 标准。

SCL 和 SDA 的最长 上升时间规格 t RISE MAX

由上拉和 C BUS 所创建的

RC 时间常数控制, 被定义为从

VIO 过渡到 VIH 时 花费的时间。

给定运行模式的 上拉电阻器的

最大大小 由公式 1 决定,

其中的 t RISE 绝不能超过

C BUS 中的任何 给定总线电容,

t RISE MAX 绝不能 超过任何给定

总线电容 C BUS, 这样就设置了

上拉电阻值的上限。

最小上拉电阻

R Pullup Min 由 VOL Max 定义,VOL Max 是

跨下拉电阻 产生的电压,

当打开时,会有 一个指定的 IOL

Min 经过它。

这样即可有效地 定义总线上的

任何 FET 的最大 RDS。

了解 VCC、 VOL MAX 和 IOL MIN 之后,

我们便可定义 最小上拉电阻,

在为确保绝不超过 VOL 时需要使用此值。

参见公式 2。

它限定了上拉 电阻器值的下限。

I²C 接口 可支持

总线上的数百个 从器件,此数量只取决于

可用从器件地址 的数量。

不过,很明显, 如果每个器件

都有高达 10 皮法的电容,

则运行模式的 给定总线上的从器件

数量将受到 C BUS MAX 的限制。

这意味着需要 采用某种方法

将一个总线及其总线 电容拆分到多个总线中,

以满足 I²C 时序

要求。

幸运的是,I²C 缓冲器正是为此而生。

它们使用一个总线 电容为 C BUS 的总线

并将其拆分和 隔离到两个总线中:

电容 C BUS 1 和 C BUS 2。

要拆分总线电容, 需要使用

单独的上拉电阻器在

每个总线上生成 逻辑高电平,这样就

需要使用 R 上拉 1 和 R 上拉 2。

总线 1 和总线 2 都必须遵循

所用运行模式的 t RISE MAX、C BUS MAX、VOL MAX

和 IOL MIN 的 I²C 标准。

有关实施、选择 和使用 I²C 缓冲器的

更多信息,请阅读 “使用 I²C 缓冲器的

原因、时机和方法” 应用报告。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室 推出的 I²C 缓冲器培训视频。 在本视频中,我们 将讨论是否需要 在 I²C 系统中使用缓冲器、 如何在硬件中实施缓冲器以及 它会对系统产生哪些影响。 I²C 总线 是 5 向接口, 利用一个称为 主器件的控制器 与一个或多个从器件 进行通信。 I²C 总线上的 每个器件都有 一个特定的器件 地址,用于区分 同一个 I²C 总线上的其他器件。 物理 I²C 接口由 串行时钟线 SCL 和 串行数据线 SDA 组成。 SDA 和 SCL 线都 必须通过上拉电阻器 连接到 VCC。 上拉电阻器的大小由 总线上的电容 数量以及 I²C 总线上使用的 最大 VLL 决定。 必须注意的是, 总线上的电容 C BUS 包括 PCB 电容、主器件的 电容以及每个 从器件的电容。 I²C 接口的 SDA 和 SCL 线 都有自己的总线以及 可能不同的 单独总线电容, 即 C Bus。 为了简单起见, 本视频只讨论一条总线。 但内容与 SCL 和 SDA 线都相关。 这一条总线既 代表 SDA,也代表 SCL。 I²C 接口具有 不同的运行模式, 取决于通信的 最高时钟频率, 此频率称为 f CLOCK MAX。 本视频将 介绍三种模式: 标准模式、快速 模式和超快速模式。 I²C 标准为每种 运行模式定义了 多个参数,但 本视频中只 定义了其中四个 最重要的参数,即 C BUS、t RISE MAX、V OL MAX 和 I OL MIN。 对于标准模式, f CLOCK MAX 为 100 千赫兹、 C Bus MAX 为 400 皮法、 t RISE MAX 为 1000 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于快速模式, f CLOCK MAX 为 400 千赫兹、 C BUS MAX 为 400 皮法、 t RISE MAX 为 300 纳秒、 V OL 为 0.4 伏、 I OL 为 3 毫安。 对于超快速模式, f CLOCK MAX 为 1000 千赫兹、 C BUS MAX 为 550 皮法、 t RISE MAX 为 120 纳秒、 V OL 为 0.4 伏、 I OL 为 20 毫安。 这些参数用于 选择上拉电阻器值 和确定是否需要 在系统中使用缓冲器 以满足 I²C 标准。 SCL 和 SDA 的最长 上升时间规格 t RISE MAX 由上拉和 C BUS 所创建的 RC 时间常数控制, 被定义为从 VIO 过渡到 VIH 时 花费的时间。 给定运行模式的 上拉电阻器的 最大大小 由公式 1 决定, 其中的 t RISE 绝不能超过 C BUS 中的任何 给定总线电容, t RISE MAX 绝不能 超过任何给定 总线电容 C BUS, 这样就设置了 上拉电阻值的上限。 最小上拉电阻 R Pullup Min 由 VOL Max 定义,VOL Max 是 跨下拉电阻 产生的电压, 当打开时,会有 一个指定的 IOL Min 经过它。 这样即可有效地 定义总线上的 任何 FET 的最大 RDS。 了解 VCC、 VOL MAX 和 IOL MIN 之后, 我们便可定义 最小上拉电阻, 在为确保绝不超过 VOL 时需要使用此值。 参见公式 2。 它限定了上拉 电阻器值的下限。 I²C 接口 可支持 总线上的数百个 从器件,此数量只取决于 可用从器件地址 的数量。 不过,很明显, 如果每个器件 都有高达 10 皮法的电容, 则运行模式的 给定总线上的从器件 数量将受到 C BUS MAX 的限制。 这意味着需要 采用某种方法 将一个总线及其总线 电容拆分到多个总线中, 以满足 I²C 时序 要求。 幸运的是,I²C 缓冲器正是为此而生。 它们使用一个总线 电容为 C BUS 的总线 并将其拆分和 隔离到两个总线中: 电容 C BUS 1 和 C BUS 2。 要拆分总线电容, 需要使用 单独的上拉电阻器在 每个总线上生成 逻辑高电平,这样就 需要使用 R 上拉 1 和 R 上拉 2。 总线 1 和总线 2 都必须遵循 所用运行模式的 t RISE MAX、C BUS MAX、VOL MAX 和 IOL MIN 的 I²C 标准。 有关实施、选择 和使用 I²C 缓冲器的 更多信息,请阅读 “使用 I²C 缓冲器的 原因、时机和方法” 应用报告。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频

大家好,欢迎观看 高精度实验室

推出的 I²C 缓冲器培训视频。

在本视频中,我们 将讨论是否需要

在 I²C 系统中使用缓冲器、 如何在硬件中实施缓冲器以及

它会对系统产生哪些影响。

I²C 总线 是 5 向接口,

利用一个称为 主器件的控制器

与一个或多个从器件

进行通信。

I²C 总线上的 每个器件都有

一个特定的器件 地址,用于区分

同一个 I²C 总线上的其他器件。

物理 I²C 接口由

串行时钟线 SCL 和

串行数据线 SDA 组成。

SDA 和 SCL 线都 必须通过上拉电阻器

连接到 VCC。

上拉电阻器的大小由

总线上的电容 数量以及 I²C

总线上使用的 最大 VLL 决定。

必须注意的是, 总线上的电容 C BUS

包括 PCB 电容、主器件的

电容以及每个 从器件的电容。

I²C 接口的 SDA 和 SCL 线

都有自己的总线以及

可能不同的 单独总线电容,

即 C Bus。

为了简单起见, 本视频只讨论一条总线。

但内容与 SCL 和 SDA 线都相关。

这一条总线既 代表 SDA,也代表 SCL。

I²C 接口具有 不同的运行模式,

取决于通信的 最高时钟频率,

此频率称为 f CLOCK MAX。

本视频将 介绍三种模式:

标准模式、快速 模式和超快速模式。

I²C 标准为每种 运行模式定义了

多个参数,但 本视频中只

定义了其中四个 最重要的参数,即 C BUS、t RISE

MAX、V OL MAX 和 I OL MIN。

对于标准模式, f CLOCK MAX 为 100 千赫兹、

C Bus MAX 为 400 皮法、 t RISE MAX 为 1000 纳秒、

V OL 为 0.4 伏、 I OL 为 3 毫安。

对于快速模式, f CLOCK MAX 为 400 千赫兹、

C BUS MAX 为 400 皮法、 t RISE MAX 为 300 纳秒、

V OL 为 0.4 伏、 I OL 为 3 毫安。

对于超快速模式, f CLOCK MAX 为 1000 千赫兹、

C BUS MAX 为 550 皮法、 t RISE MAX 为 120 纳秒、

V OL 为 0.4 伏、 I OL 为 20 毫安。

这些参数用于 选择上拉电阻器值

和确定是否需要 在系统中使用缓冲器

以满足 I²C 标准。

SCL 和 SDA 的最长 上升时间规格 t RISE MAX

由上拉和 C BUS 所创建的

RC 时间常数控制, 被定义为从

VIO 过渡到 VIH 时 花费的时间。

给定运行模式的 上拉电阻器的

最大大小 由公式 1 决定,

其中的 t RISE 绝不能超过

C BUS 中的任何 给定总线电容,

t RISE MAX 绝不能 超过任何给定

总线电容 C BUS, 这样就设置了

上拉电阻值的上限。

最小上拉电阻

R Pullup Min 由 VOL Max 定义,VOL Max 是

跨下拉电阻 产生的电压,

当打开时,会有 一个指定的 IOL

Min 经过它。

这样即可有效地 定义总线上的

任何 FET 的最大 RDS。

了解 VCC、 VOL MAX 和 IOL MIN 之后,

我们便可定义 最小上拉电阻,

在为确保绝不超过 VOL 时需要使用此值。

参见公式 2。

它限定了上拉 电阻器值的下限。

I²C 接口 可支持

总线上的数百个 从器件,此数量只取决于

可用从器件地址 的数量。

不过,很明显, 如果每个器件

都有高达 10 皮法的电容,

则运行模式的 给定总线上的从器件

数量将受到 C BUS MAX 的限制。

这意味着需要 采用某种方法

将一个总线及其总线 电容拆分到多个总线中,

以满足 I²C 时序

要求。

幸运的是,I²C 缓冲器正是为此而生。

它们使用一个总线 电容为 C BUS 的总线

并将其拆分和 隔离到两个总线中:

电容 C BUS 1 和 C BUS 2。

要拆分总线电容, 需要使用

单独的上拉电阻器在

每个总线上生成 逻辑高电平,这样就

需要使用 R 上拉 1 和 R 上拉 2。

总线 1 和总线 2 都必须遵循

所用运行模式的 t RISE MAX、C BUS MAX、VOL MAX

和 IOL MIN 的 I²C 标准。

有关实施、选择 和使用 I²C 缓冲器的

更多信息,请阅读 “使用 I²C 缓冲器的

原因、时机和方法” 应用报告。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频

手机看

扫码用手机观看

视频简介

视频简介

6.4 TI 高精度实验室 -I2C:缓冲器概述

所属课程:TI 高精度实验室 - I2C

发布时间:2020.01.13

视频集数:4

本节视频时长:00:05:13

了解如何使用I2C IC进行设计。 TI Precision Labs(TIPL)是模拟信号链设计人员最全面的在线教室。该 接口系列 提供了通过工业,汽车和多种应用领域常用协议的技术培训。 从I2C系列开始,以了解I2C标准,数据协议的基础知识和所使用的物理信号,以及如何使用转换器和缓冲设备解决应用程序级问题。

未学习 6.1 TI 高精度实验室 -I2C:硬件概述

未学习 6.1 TI 高精度实验室 -I2C:硬件概述

未学习 6.2 TI 高精度实验室 -I2C:协议概述

未学习 6.2 TI 高精度实验室 -I2C:协议概述

未学习 6.3 TI 高精度实验室 -I2C:转换器概述

未学习 6.3 TI 高精度实验室 -I2C:转换器概述

未学习 6.4 TI 高精度实验室 -I2C:缓冲器概述

未学习 6.4 TI 高精度实验室 -I2C:缓冲器概述

视频简介

视频简介