1.2 管理延迟

Loading the player...

将在30s后自动为您播放下一课程

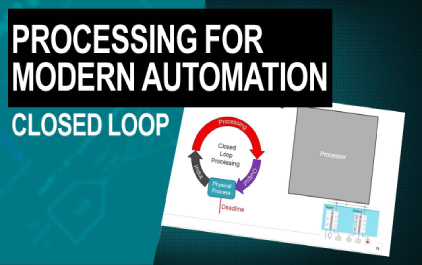

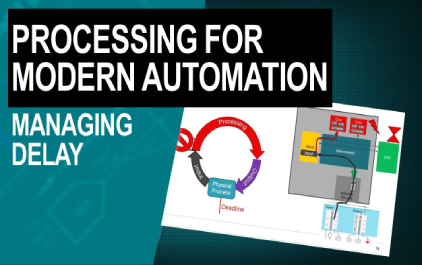

你好。 感谢您选择观看此视频, 本视频的主题是“为工业应用 构建工业ARM-- AM65xx架构差异化”。 这是系列的第2部分, 这部分称为管理延迟。 在本系列的第一部分中, 我们了解了一个名为行李仓库的 现代自动化系统。 这是一个在迪拜国际机场 使用的行李处理系统, 它是一个现代化的自动化系统, 与许多不同的组件一起构建, 可以自动处理行李。 任何旅行的人都知道 你什么时候登机行李并进入飞机 - 并希望它能 在目的地的机场回到你身边 - 这个行李肯定有很有趣的经历, 这涉及一个新方法。 这是我们尝试用现代 自动化系统做的一个很好的例子。 我们谈到了这样一个事实, 即系统由234个PLC或可编程逻辑控制器, 以及大量的输入和输出 以及电机驱动器和许多其他东西组成。 我们进入其中一个PLC, 看看它中使用的处理器是如何构建的, 以及它将要进行的 处理类型。 如果你还未弄明白, 我希望这次你会。 有一个行李处理系统的视频, 你也可以去看看。 这非常有趣,它为这次讨论 设定了良好的背景,我们将讨论 如何使用现代处理器来管理延迟。 所以让我们再深入探讨一下。 这是我们从最后一节构建的 处理器,你可以看到这个处理器 连接到某些输入和输出, 可能通过工业,以太网类型的 应用程序。 如果你一起构建它 并在其周围放置许多其他有趣的东西, 那就是如何构建PLC。 请记住,我们正在进行的处理类型 是受控处理。 所以这里有一个例子,它显示了底部的 物理过程,输入和输出正在处理中, 这是传感器的实际读数 和电机的移动。 然后将该输入传输到 处理器进行处理。 很多时候,在PLC中,这是横向逻辑。 然后,当然,计算输出并将其 放回以用于完成整个 过程的物理过程。 控制循环处理的有趣之处很多, 这必须在非常具体的 时间完成。 我们称之为截止期限。 现在,截止期限的严重程度因系统而异, 但有时可能会非常严重, 导致整个系统崩溃 甚至造成伤害或生命损失。 所以这些可能是非常严重的系统, 当然,它们需要以不符合这些期限的 方式进行架构。 那么让我们来看看这个处理器的组件。 我们正在深入研究这个处理器 需要具备的内容,以便更好地适应这种整体架构。 当然,第一个组件是 实际与输入和输出通信的一种方式。 我们称之为工业以太网接口。 很多时候,这也有移动数据的线索。 接下来的部分只是将这些数据 连接到系统的其他部分, 我们将其称为通用总线 和互连。 这主要用于数据移动。 最后一部分是我们都在思考的部分, 这是实际的处理核心。 很多时候,它们会在进行 处理操作时附带一些 用于本地存储数据的缓存。 因此,让我们在这个过程的输入部分进入区域 - 即将发生的物理过程。 我们需要将输入传输到处理器, 以便将其输入正在使用的 控制算法中。 所以在这里我们将展示来自输入的数据, 通过工业以太网传输。 然后问题就变成, 一旦它进入处理器,我们将它放在哪里? 我们如何储存它? 显然,我们需要某种记忆体。 从延迟的角度来看,将它直接 放在核心的缓存中可能会很好, 但是你不能直接写入缓存, 所以这对我们来说不是一个好的解决方案。 因此,现代处理器当然使用DDR很多, 所以我们将使用它作为我们的例子。 我们有一些DDR,将输入数据存储 在DDR中。 这个过程的下一部分 是实际的处理部分, 然后开始通过中断核心让 它知道它有一个输入进行处理。 然后我们可以通过将其读入处理器 然后将其写回来进行处理。 这就是我们控制循环的处理部分。 我们将展示数据读取到核心, 处理,当然,我们会将其 作为本地输出写回来。 为了完成控制循环 并至少将其恢复到物理过程, 我们需要将输出写入输出设备。 这是我们这样做的方法。 所以这才是真正的全过程。 我们将把这一切都搞定,这样你就能看到一切。 输入,那里的核心, 过程,输出, 大量的通信和同步。 我们现在了解了概念, 你可能会对整体情况有所了解。 当然,我们希望有足够的时间 来完成物理过程 以满足我们的最后期限, 并且我们控制的系统可以正确控制, 以便它能够完成它的设计目标。 好吧,当一切正常时,这一切都很好, 但是工作有点出错。 例如,如果我们的输入需要更长时间,会发生什么? 什么会导致这种情况发生? 所以在这里我们将展示你的输入正在延长, 超出了我们刚才看到的第一个 例子中的时间。 有一些延迟是从第一次 输入完成时添加的。 所以现在这个输入花费的时间比那个更长, 当然,如果我们的处理花费相同的时间 并且我们的输出需要相同的时间, 那么在物理过程完成之前 可能不会留下足够的时间满足期限要求, 这当然会导致我们的 控制系统出现问题。 所以这不好。 控制回路设计系统中的延迟很糟糕。 因此,我们希望学会避免, 我们希望看到我们如何能够构建这个系统 - 特别是处理器 - 以便能够避免这些延迟或管理它们。 那么我们怎么能以不同的方式做到这一点, 至少可以控制延迟? 让我们来看看我们正在尝试的方法。 我们将数据带入DDR。 我们中断核心。 但是在这个例子中,如果核心不能立即服务 中断怎么办? 也许它正在忙于做其他事情, 而且它不能做到这一点, 当然,这会延迟处理。 我们可以尝试通过安排来处理这个问题。 所以你可以使用基于优先级的 调度算法,这是你最重要的事情, 所以当发生这种情况时, 停止你正在做的事情并去做优先事项。 并且您可以以更物理的方式使用嵌套中断 来执行此操作。 这些都是很好的例子,但有时它们只会 让你止步于此,并且很难在复杂系统的 每个环境中构建 并验证它。 所以这可能很有用, 但特别是当我们以1到2千兆赫兹的 速度点击处理器时,或者我们受到限制时, 这会让你止步于此。 所以你可能想要一些更好的东西, 所以我们将看一个不同的解决方案, 允许在处理器忙时导入数据, 并在读取DDR输入之前导致延迟。 我们将通过添加更多内核来实现这一目标。 这将成为整个演示文稿中 的一个共同主题 - 为了使您能够管理延迟,当然,适当、一致和系统地 处理您的期限, 很多时候您需要按顺序 进行特定的资源分配处理实时数据。 这将是第一个例子。 我们要添加一个核心 - 所以这就是新核心。 而这将允许我们做的是 用一个核心管理中断, 并为梯形逻辑提供另一个核心。 然后你的梯形逻辑可以不断地拉动, 或者不管它需要做什么来找出 - 去获得 新的输入。 只要你的循环时间和阶梯逻辑是合适的, 就应该没问题。 因此,这是添加另一个核心的示例, 以便您可以管理延迟并摆脱它, 对于控制器处理, 这就是我们想要做的。 让我们来看另一个 可能出现延迟的例子。 所以我们有两个核心。 我们已经解决了部分问题。 但另一个延迟可以从哪里来? 这将是我们正在使用的内存类型。 所以我们来到这里。 我们写或输入DDR。 我们中断处理器。 我们有一个专用的核心,所以你可以得到数据。 但是,如果要获得数据,DDR会恨忙吗? 在我们看到核心繁忙之前。 现在核心可用,但DDR必须刷新。 这会将数据延迟一些, 并将我们的延迟带回控制回路 并对我们的系统造成严重破坏。 我们不希望这种情况发生,那么我们 如何解决这个问题呢? 想一想。你可以做到的一种 方法是获得更多的记忆体。 我们将为设备添加一些片上存储器。 我们的数据延迟。 我们不希望这样,所以我们 将添加片上存储器,以便存储我们的时间关键数据。 与我们之前谈到的缓存不同, 芯片存储器可以直接写入。 因此,我们将输入数据从DDR 移至内部SRAM,这样我们就可以 直接在那里写入并使用它 来处理核心,内部SRAM 不会出现刷新问题或 可能与DDR相关的延迟其他问题, 这也使我们能够摆脱这种延迟。 所以我们为核心处理添加了核心。 现在我们已经增加了内存,因此我们通过内部存储器 获得了实时数据的特定路径, 这样我们就可以避免DDR延迟。 让我们继续。 现在,我们已经为我们的实时数据提供了良好的途径。 因此,我们在此处显示 - 您的实时数据的 输入和输出通过工业以太网, 进入内部存储器,并由您的一个核心 用于处理。 如果我们需要,还有其他核心用于 中断和其他一些内务管理。 这对于实时路径都有好处, 但其他呢? 正如您所预料的那样,现代系统 需要的不仅仅是处理实时数据。 他们经常也必须处理其他数据。 那就是非实时数据。 这可以是管理数据,元数据。 对整个操作系统来说这很重要, 但它不是闭环的一部分, 或者是一个非常松散的闭环。 因此,它没有我们一直在关注的 这些实时期限, 这会导致系统以灾难性的方式影响系统, 从而导致系统真正失败。 因此,我们还有其他需要 流经系统的非实时数据, 并且它不需要干扰我们的实时数据。 这就是我们在深灰色 和紫色中显示的数据。 所以我们的非实时数据 - 当我们将它添加到系统中时, 是否会导致实时数据出现问题? 当然,如果你没有把事情做好, 它肯定会进入并开始造成麻烦, 因为如果它经过相同的资源, 这些资源可能会被很多非实时数据所消耗, 因为这会导致 实时数据错过时间。 你可能会看到这里发生的一个地方 是在工业以太网的队列中。 如果它们的设计不正确, 如果你有一个队列来存储所有这些数据, 那么当然会有一些非实时数据 进入并阻塞这些队列, 导致你的实时数据被卡在非实时数据, 无法满足期限要求。 所以我们需要以不同的方式构建。 当然,我们要这样做的方式 与核心和内存非常相似。 我们将添加一些冗余资源, 并专门用于实时数据。 所以我们将添加更多队列。 如果愿意的话,我们会通过这些新的实时 线索传递我们的 实时数据。 我们将通过非实时时间队列 传递非实时数据。 当然,我们可以将这些存储在DDR中。 所以现在我们为实时数据 和非实时数据提供了单独的路径。 这会花费我们更多的资源, 但如果我们需要解决这个问题并可靠地解决它, 那么这是一个很好的设计。 让我们来看看另一个 可能会遇到一些问题的地方。 那这个呢总线结构, 所有数据仍然流经的总线? 那个总线不够宽和足够快, 可能会导致问题。 再次,它是一个单一的资源, 所以我们可能要做的是继续添加更多的总线, 以便我们有一个专用的总线用于我们的实时数据, 然后我们可以使用非实时总线 用于我们的非实时数据。 因此,我们将添加另一条总线, 通过它传递我们的实时数据, 然后通过另一条总线获取非实时数据。 所以现在我们已经采用了相当多的系统, 我们已经添加了特定的部分来处理这些实时数据, 我们已经允许非实时数据的其他部分, 以便您可以设计一个系统管理 并取得成功。 我们谈到的中间部分大块是互连, 这显然非常重要。 它正在进行所有数据移动。 我们谈到了增加总线的问题。 我们增加了更多内存。 我们添加了更多内核。 我们有很多不同的东西 需要通过这种互连进行通信 和发送数据,而这种互连 需要以能够管理它的方式进行设计。 它需要知道实时数据是什么 以及非实时数据是什么, 并确保它可以保持实时数据的 时序约束。 互连的一个最大问题是 你有大量的非实时数据, 你开始大转移 - 通过以太网到DDR-- 并且互连专用了大量资源来 尽可能快地完成, 但随后实时传输量很小, 必须等待大传输。 显然,这不是一个好的设计, 所以我们需要一个互连,以确保 您的实时数据仍然可以传输, 即使有大量非实时 数据传输。 所以我们很好地构建了它。 稍微改变视图 并查看该系统的不同方面。 我们已经很好地研究了芯片的内部结构, 但让我们考虑一下以太网的实际物理介质, 看看这是否 可能导致延迟。 当我们开始将流量放在那个 以太网传输介质上时,该介质真的会成为 延迟的原因吗? 当然,它可以,取决于可用的 带宽和它的架构。 它当然可能成为一个问题, 其中一堆非实时数据 通过该总线并使用它,您的实时数据 无法传输,等等。 因此,实际的以太网本身 可能是导致系统延迟的原因。 你可以看到,因为所有东西 都在使用这条线, 而且我们的延迟图片 显示我们在系统中遇到了延迟。 无论是否在处理器中发生, 如果它是系统中的延迟,那将导致问题。 因此,以太网本身可能成为一个问题, 因此我们需要一个解决方案。 我们需要看一下一些新的 现代工业以太网方法。 当然,要考虑的是TSN。 就像我们今天在讨论的 其余部分中所做的那样, 为RT数据提供单独的路径到非RT数据, 这样RT数据总是可以在需要时连线, 并且可以使非RT数据等待 或使用不同的时序,以便RT数据 可以获得它需要的优先级。 这是对此的最后一种看法, 因为我们已经完成整个系统 并系统地消除了一些延迟。 让我们考虑一下整个系统 以及它将如何运作。 如果我们想要同时做事, 那么其中一个重大问题就会变成什么? 每个人都同意在同一时间做某事。 我们如何确保系统能够做到这一点? 请记住,这可能是一个非常大的系统。 我们谈到了234 PLC的行李仓库, 整个系统试图一起工作。 但这可以像你和你的同事 试图组织午餐一样简单。 你们都同意:中午 我们会一起去。 而且你想要在正确的时间去, 这样你就可以高效,有组织等 所以这实际上只是 您尝试进行时间同步的任何系统。 当然,你需要做的第一件事是 你需要一个时间基础。 所以每个人都需要钟表或手表, 这取决于你自己的方式。 所以我们将这些添加到我们的图表中, 每个人都会尝试同时做某事。 如果你这样做,输入的表运行缓慢, 会发生什么? 每个人都同意我们会在1:30做一些事情, 但输入的手表很慢, 所以当它在1:30读取时,会发生什么? 这真的晚了五分钟,对吗? 并且迟到五分钟的输入 结果看起来像我们之前 谈到的延迟。 所以这是我们的延迟。 如果输入读取的时间较晚,因为它的表速度很慢, 那么对于其他系统来说,它看起来就像是一个延迟。 输入成为你午餐会议 总是迟到五分钟的那个人, 并使你成为自助餐厅队列中的最后一人。 因此,我们想要解决的问题 当然是拥有一个强大的同步系统, 整个系统中的所有手表组织良好, 系统实际上遵循这些时间, 以便您的同事不能总是 五分钟迟到吃午饭。 因此,时间同步对于消除系统中的延迟也很重要, 并且它将成为我们 将如何在系统中处理此类活动的 策略之一。 本节内容到此结束, 我们已经彻底地说明了 一个过程或体系结构,并查看了几个可以 将延迟引入系统的地方, 以及这种延迟对系统的影响。 这是我们查看所有这些并通过内核 和内存以及包管理的方式队列, 总线,互连。 我们谈到的最后几件事 是实际的以太网接口本身, 以及整个系统的时间同步。 这些都是概念,如果我们 将它们应用到芯片架构中, 我们希望能够构建一个对闭环处理 非常有效的芯片, 并且是PLC的理想选择。 我希望你喜欢这个演讲。 感谢各位。 如果您想获得更多信息, 特别是AM654x, 我会为您提供更多资源。 我们有更多的培训。 可供您选择。 你也可以去看看。 当然,就数据表, 技术参考手册而言,我们在网上有大量信息 包括您需要进行设计的所有不同内容。 我们还为AM65x系列提供软件。 我们有板、评估模块 和工业开发套件。 当然,我们很乐意通过我们的支持论坛 为您提供支持,您可以搜索 已经提出的问题, 希望这对您有所帮助。 如果没有,您可以提出一个新问题, 我们会尽力帮助您。 再次,非常感谢, 希望各位一切顺利。 谢谢。

你好。 感谢您选择观看此视频, 本视频的主题是“为工业应用 构建工业ARM-- AM65xx架构差异化”。 这是系列的第2部分, 这部分称为管理延迟。 在本系列的第一部分中, 我们了解了一个名为行李仓库的 现代自动化系统。 这是一个在迪拜国际机场 使用的行李处理系统, 它是一个现代化的自动化系统, 与许多不同的组件一起构建, 可以自动处理行李。 任何旅行的人都知道 你什么时候登机行李并进入飞机 - 并希望它能 在目的地的机场回到你身边 - 这个行李肯定有很有趣的经历, 这涉及一个新方法。 这是我们尝试用现代 自动化系统做的一个很好的例子。 我们谈到了这样一个事实, 即系统由234个PLC或可编程逻辑控制器, 以及大量的输入和输出 以及电机驱动器和许多其他东西组成。 我们进入其中一个PLC, 看看它中使用的处理器是如何构建的, 以及它将要进行的 处理类型。 如果你还未弄明白, 我希望这次你会。 有一个行李处理系统的视频, 你也可以去看看。 这非常有趣,它为这次讨论 设定了良好的背景,我们将讨论 如何使用现代处理器来管理延迟。 所以让我们再深入探讨一下。 这是我们从最后一节构建的 处理器,你可以看到这个处理器 连接到某些输入和输出, 可能通过工业,以太网类型的 应用程序。 如果你一起构建它 并在其周围放置许多其他有趣的东西, 那就是如何构建PLC。 请记住,我们正在进行的处理类型 是受控处理。 所以这里有一个例子,它显示了底部的 物理过程,输入和输出正在处理中, 这是传感器的实际读数 和电机的移动。 然后将该输入传输到 处理器进行处理。 很多时候,在PLC中,这是横向逻辑。 然后,当然,计算输出并将其 放回以用于完成整个 过程的物理过程。 控制循环处理的有趣之处很多, 这必须在非常具体的 时间完成。 我们称之为截止期限。 现在,截止期限的严重程度因系统而异, 但有时可能会非常严重, 导致整个系统崩溃 甚至造成伤害或生命损失。 所以这些可能是非常严重的系统, 当然,它们需要以不符合这些期限的 方式进行架构。 那么让我们来看看这个处理器的组件。 我们正在深入研究这个处理器 需要具备的内容,以便更好地适应这种整体架构。 当然,第一个组件是 实际与输入和输出通信的一种方式。 我们称之为工业以太网接口。 很多时候,这也有移动数据的线索。 接下来的部分只是将这些数据 连接到系统的其他部分, 我们将其称为通用总线 和互连。 这主要用于数据移动。 最后一部分是我们都在思考的部分, 这是实际的处理核心。 很多时候,它们会在进行 处理操作时附带一些 用于本地存储数据的缓存。 因此,让我们在这个过程的输入部分进入区域 - 即将发生的物理过程。 我们需要将输入传输到处理器, 以便将其输入正在使用的 控制算法中。 所以在这里我们将展示来自输入的数据, 通过工业以太网传输。 然后问题就变成, 一旦它进入处理器,我们将它放在哪里? 我们如何储存它? 显然,我们需要某种记忆体。 从延迟的角度来看,将它直接 放在核心的缓存中可能会很好, 但是你不能直接写入缓存, 所以这对我们来说不是一个好的解决方案。 因此,现代处理器当然使用DDR很多, 所以我们将使用它作为我们的例子。 我们有一些DDR,将输入数据存储 在DDR中。 这个过程的下一部分 是实际的处理部分, 然后开始通过中断核心让 它知道它有一个输入进行处理。 然后我们可以通过将其读入处理器 然后将其写回来进行处理。 这就是我们控制循环的处理部分。 我们将展示数据读取到核心, 处理,当然,我们会将其 作为本地输出写回来。 为了完成控制循环 并至少将其恢复到物理过程, 我们需要将输出写入输出设备。 这是我们这样做的方法。 所以这才是真正的全过程。 我们将把这一切都搞定,这样你就能看到一切。 输入,那里的核心, 过程,输出, 大量的通信和同步。 我们现在了解了概念, 你可能会对整体情况有所了解。 当然,我们希望有足够的时间 来完成物理过程 以满足我们的最后期限, 并且我们控制的系统可以正确控制, 以便它能够完成它的设计目标。 好吧,当一切正常时,这一切都很好, 但是工作有点出错。 例如,如果我们的输入需要更长时间,会发生什么? 什么会导致这种情况发生? 所以在这里我们将展示你的输入正在延长, 超出了我们刚才看到的第一个 例子中的时间。 有一些延迟是从第一次 输入完成时添加的。 所以现在这个输入花费的时间比那个更长, 当然,如果我们的处理花费相同的时间 并且我们的输出需要相同的时间, 那么在物理过程完成之前 可能不会留下足够的时间满足期限要求, 这当然会导致我们的 控制系统出现问题。 所以这不好。 控制回路设计系统中的延迟很糟糕。 因此,我们希望学会避免, 我们希望看到我们如何能够构建这个系统 - 特别是处理器 - 以便能够避免这些延迟或管理它们。 那么我们怎么能以不同的方式做到这一点, 至少可以控制延迟? 让我们来看看我们正在尝试的方法。 我们将数据带入DDR。 我们中断核心。 但是在这个例子中,如果核心不能立即服务 中断怎么办? 也许它正在忙于做其他事情, 而且它不能做到这一点, 当然,这会延迟处理。 我们可以尝试通过安排来处理这个问题。 所以你可以使用基于优先级的 调度算法,这是你最重要的事情, 所以当发生这种情况时, 停止你正在做的事情并去做优先事项。 并且您可以以更物理的方式使用嵌套中断 来执行此操作。 这些都是很好的例子,但有时它们只会 让你止步于此,并且很难在复杂系统的 每个环境中构建 并验证它。 所以这可能很有用, 但特别是当我们以1到2千兆赫兹的 速度点击处理器时,或者我们受到限制时, 这会让你止步于此。 所以你可能想要一些更好的东西, 所以我们将看一个不同的解决方案, 允许在处理器忙时导入数据, 并在读取DDR输入之前导致延迟。 我们将通过添加更多内核来实现这一目标。 这将成为整个演示文稿中 的一个共同主题 - 为了使您能够管理延迟,当然,适当、一致和系统地 处理您的期限, 很多时候您需要按顺序 进行特定的资源分配处理实时数据。 这将是第一个例子。 我们要添加一个核心 - 所以这就是新核心。 而这将允许我们做的是 用一个核心管理中断, 并为梯形逻辑提供另一个核心。 然后你的梯形逻辑可以不断地拉动, 或者不管它需要做什么来找出 - 去获得 新的输入。 只要你的循环时间和阶梯逻辑是合适的, 就应该没问题。 因此,这是添加另一个核心的示例, 以便您可以管理延迟并摆脱它, 对于控制器处理, 这就是我们想要做的。 让我们来看另一个 可能出现延迟的例子。 所以我们有两个核心。 我们已经解决了部分问题。 但另一个延迟可以从哪里来? 这将是我们正在使用的内存类型。 所以我们来到这里。 我们写或输入DDR。 我们中断处理器。 我们有一个专用的核心,所以你可以得到数据。 但是,如果要获得数据,DDR会恨忙吗? 在我们看到核心繁忙之前。 现在核心可用,但DDR必须刷新。 这会将数据延迟一些, 并将我们的延迟带回控制回路 并对我们的系统造成严重破坏。 我们不希望这种情况发生,那么我们 如何解决这个问题呢? 想一想。你可以做到的一种 方法是获得更多的记忆体。 我们将为设备添加一些片上存储器。 我们的数据延迟。 我们不希望这样,所以我们 将添加片上存储器,以便存储我们的时间关键数据。 与我们之前谈到的缓存不同, 芯片存储器可以直接写入。 因此,我们将输入数据从DDR 移至内部SRAM,这样我们就可以 直接在那里写入并使用它 来处理核心,内部SRAM 不会出现刷新问题或 可能与DDR相关的延迟其他问题, 这也使我们能够摆脱这种延迟。 所以我们为核心处理添加了核心。 现在我们已经增加了内存,因此我们通过内部存储器 获得了实时数据的特定路径, 这样我们就可以避免DDR延迟。 让我们继续。 现在,我们已经为我们的实时数据提供了良好的途径。 因此,我们在此处显示 - 您的实时数据的 输入和输出通过工业以太网, 进入内部存储器,并由您的一个核心 用于处理。 如果我们需要,还有其他核心用于 中断和其他一些内务管理。 这对于实时路径都有好处, 但其他呢? 正如您所预料的那样,现代系统 需要的不仅仅是处理实时数据。 他们经常也必须处理其他数据。 那就是非实时数据。 这可以是管理数据,元数据。 对整个操作系统来说这很重要, 但它不是闭环的一部分, 或者是一个非常松散的闭环。 因此,它没有我们一直在关注的 这些实时期限, 这会导致系统以灾难性的方式影响系统, 从而导致系统真正失败。 因此,我们还有其他需要 流经系统的非实时数据, 并且它不需要干扰我们的实时数据。 这就是我们在深灰色 和紫色中显示的数据。 所以我们的非实时数据 - 当我们将它添加到系统中时, 是否会导致实时数据出现问题? 当然,如果你没有把事情做好, 它肯定会进入并开始造成麻烦, 因为如果它经过相同的资源, 这些资源可能会被很多非实时数据所消耗, 因为这会导致 实时数据错过时间。 你可能会看到这里发生的一个地方 是在工业以太网的队列中。 如果它们的设计不正确, 如果你有一个队列来存储所有这些数据, 那么当然会有一些非实时数据 进入并阻塞这些队列, 导致你的实时数据被卡在非实时数据, 无法满足期限要求。 所以我们需要以不同的方式构建。 当然,我们要这样做的方式 与核心和内存非常相似。 我们将添加一些冗余资源, 并专门用于实时数据。 所以我们将添加更多队列。 如果愿意的话,我们会通过这些新的实时 线索传递我们的 实时数据。 我们将通过非实时时间队列 传递非实时数据。 当然,我们可以将这些存储在DDR中。 所以现在我们为实时数据 和非实时数据提供了单独的路径。 这会花费我们更多的资源, 但如果我们需要解决这个问题并可靠地解决它, 那么这是一个很好的设计。 让我们来看看另一个 可能会遇到一些问题的地方。 那这个呢总线结构, 所有数据仍然流经的总线? 那个总线不够宽和足够快, 可能会导致问题。 再次,它是一个单一的资源, 所以我们可能要做的是继续添加更多的总线, 以便我们有一个专用的总线用于我们的实时数据, 然后我们可以使用非实时总线 用于我们的非实时数据。 因此,我们将添加另一条总线, 通过它传递我们的实时数据, 然后通过另一条总线获取非实时数据。 所以现在我们已经采用了相当多的系统, 我们已经添加了特定的部分来处理这些实时数据, 我们已经允许非实时数据的其他部分, 以便您可以设计一个系统管理 并取得成功。 我们谈到的中间部分大块是互连, 这显然非常重要。 它正在进行所有数据移动。 我们谈到了增加总线的问题。 我们增加了更多内存。 我们添加了更多内核。 我们有很多不同的东西 需要通过这种互连进行通信 和发送数据,而这种互连 需要以能够管理它的方式进行设计。 它需要知道实时数据是什么 以及非实时数据是什么, 并确保它可以保持实时数据的 时序约束。 互连的一个最大问题是 你有大量的非实时数据, 你开始大转移 - 通过以太网到DDR-- 并且互连专用了大量资源来 尽可能快地完成, 但随后实时传输量很小, 必须等待大传输。 显然,这不是一个好的设计, 所以我们需要一个互连,以确保 您的实时数据仍然可以传输, 即使有大量非实时 数据传输。 所以我们很好地构建了它。 稍微改变视图 并查看该系统的不同方面。 我们已经很好地研究了芯片的内部结构, 但让我们考虑一下以太网的实际物理介质, 看看这是否 可能导致延迟。 当我们开始将流量放在那个 以太网传输介质上时,该介质真的会成为 延迟的原因吗? 当然,它可以,取决于可用的 带宽和它的架构。 它当然可能成为一个问题, 其中一堆非实时数据 通过该总线并使用它,您的实时数据 无法传输,等等。 因此,实际的以太网本身 可能是导致系统延迟的原因。 你可以看到,因为所有东西 都在使用这条线, 而且我们的延迟图片 显示我们在系统中遇到了延迟。 无论是否在处理器中发生, 如果它是系统中的延迟,那将导致问题。 因此,以太网本身可能成为一个问题, 因此我们需要一个解决方案。 我们需要看一下一些新的 现代工业以太网方法。 当然,要考虑的是TSN。 就像我们今天在讨论的 其余部分中所做的那样, 为RT数据提供单独的路径到非RT数据, 这样RT数据总是可以在需要时连线, 并且可以使非RT数据等待 或使用不同的时序,以便RT数据 可以获得它需要的优先级。 这是对此的最后一种看法, 因为我们已经完成整个系统 并系统地消除了一些延迟。 让我们考虑一下整个系统 以及它将如何运作。 如果我们想要同时做事, 那么其中一个重大问题就会变成什么? 每个人都同意在同一时间做某事。 我们如何确保系统能够做到这一点? 请记住,这可能是一个非常大的系统。 我们谈到了234 PLC的行李仓库, 整个系统试图一起工作。 但这可以像你和你的同事 试图组织午餐一样简单。 你们都同意:中午 我们会一起去。 而且你想要在正确的时间去, 这样你就可以高效,有组织等 所以这实际上只是 您尝试进行时间同步的任何系统。 当然,你需要做的第一件事是 你需要一个时间基础。 所以每个人都需要钟表或手表, 这取决于你自己的方式。 所以我们将这些添加到我们的图表中, 每个人都会尝试同时做某事。 如果你这样做,输入的表运行缓慢, 会发生什么? 每个人都同意我们会在1:30做一些事情, 但输入的手表很慢, 所以当它在1:30读取时,会发生什么? 这真的晚了五分钟,对吗? 并且迟到五分钟的输入 结果看起来像我们之前 谈到的延迟。 所以这是我们的延迟。 如果输入读取的时间较晚,因为它的表速度很慢, 那么对于其他系统来说,它看起来就像是一个延迟。 输入成为你午餐会议 总是迟到五分钟的那个人, 并使你成为自助餐厅队列中的最后一人。 因此,我们想要解决的问题 当然是拥有一个强大的同步系统, 整个系统中的所有手表组织良好, 系统实际上遵循这些时间, 以便您的同事不能总是 五分钟迟到吃午饭。 因此,时间同步对于消除系统中的延迟也很重要, 并且它将成为我们 将如何在系统中处理此类活动的 策略之一。 本节内容到此结束, 我们已经彻底地说明了 一个过程或体系结构,并查看了几个可以 将延迟引入系统的地方, 以及这种延迟对系统的影响。 这是我们查看所有这些并通过内核 和内存以及包管理的方式队列, 总线,互连。 我们谈到的最后几件事 是实际的以太网接口本身, 以及整个系统的时间同步。 这些都是概念,如果我们 将它们应用到芯片架构中, 我们希望能够构建一个对闭环处理 非常有效的芯片, 并且是PLC的理想选择。 我希望你喜欢这个演讲。 感谢各位。 如果您想获得更多信息, 特别是AM654x, 我会为您提供更多资源。 我们有更多的培训。 可供您选择。 你也可以去看看。 当然,就数据表, 技术参考手册而言,我们在网上有大量信息 包括您需要进行设计的所有不同内容。 我们还为AM65x系列提供软件。 我们有板、评估模块 和工业开发套件。 当然,我们很乐意通过我们的支持论坛 为您提供支持,您可以搜索 已经提出的问题, 希望这对您有所帮助。 如果没有,您可以提出一个新问题, 我们会尽力帮助您。 再次,非常感谢, 希望各位一切顺利。 谢谢。

你好。

感谢您选择观看此视频,

本视频的主题是“为工业应用

构建工业ARM--

AM65xx架构差异化”。

这是系列的第2部分,

这部分称为管理延迟。

在本系列的第一部分中,

我们了解了一个名为行李仓库的

现代自动化系统。

这是一个在迪拜国际机场

使用的行李处理系统,

它是一个现代化的自动化系统,

与许多不同的组件一起构建,

可以自动处理行李。

任何旅行的人都知道

你什么时候登机行李并进入飞机 -

并希望它能

在目的地的机场回到你身边 -

这个行李肯定有很有趣的经历,

这涉及一个新方法。

这是我们尝试用现代

自动化系统做的一个很好的例子。

我们谈到了这样一个事实,

即系统由234个PLC或可编程逻辑控制器,

以及大量的输入和输出

以及电机驱动器和许多其他东西组成。

我们进入其中一个PLC,

看看它中使用的处理器是如何构建的,

以及它将要进行的

处理类型。

如果你还未弄明白,

我希望这次你会。

有一个行李处理系统的视频,

你也可以去看看。

这非常有趣,它为这次讨论

设定了良好的背景,我们将讨论

如何使用现代处理器来管理延迟。

所以让我们再深入探讨一下。

这是我们从最后一节构建的

处理器,你可以看到这个处理器

连接到某些输入和输出,

可能通过工业,以太网类型的

应用程序。

如果你一起构建它

并在其周围放置许多其他有趣的东西,

那就是如何构建PLC。

请记住,我们正在进行的处理类型

是受控处理。

所以这里有一个例子,它显示了底部的

物理过程,输入和输出正在处理中,

这是传感器的实际读数

和电机的移动。

然后将该输入传输到

处理器进行处理。

很多时候,在PLC中,这是横向逻辑。

然后,当然,计算输出并将其

放回以用于完成整个

过程的物理过程。

控制循环处理的有趣之处很多,

这必须在非常具体的

时间完成。

我们称之为截止期限。

现在,截止期限的严重程度因系统而异,

但有时可能会非常严重,

导致整个系统崩溃

甚至造成伤害或生命损失。

所以这些可能是非常严重的系统,

当然,它们需要以不符合这些期限的

方式进行架构。

那么让我们来看看这个处理器的组件。

我们正在深入研究这个处理器

需要具备的内容,以便更好地适应这种整体架构。

当然,第一个组件是

实际与输入和输出通信的一种方式。

我们称之为工业以太网接口。

很多时候,这也有移动数据的线索。

接下来的部分只是将这些数据

连接到系统的其他部分,

我们将其称为通用总线

和互连。

这主要用于数据移动。

最后一部分是我们都在思考的部分,

这是实际的处理核心。

很多时候,它们会在进行

处理操作时附带一些

用于本地存储数据的缓存。

因此,让我们在这个过程的输入部分进入区域 -

即将发生的物理过程。

我们需要将输入传输到处理器,

以便将其输入正在使用的

控制算法中。

所以在这里我们将展示来自输入的数据,

通过工业以太网传输。

然后问题就变成,

一旦它进入处理器,我们将它放在哪里?

我们如何储存它?

显然,我们需要某种记忆体。

从延迟的角度来看,将它直接

放在核心的缓存中可能会很好,

但是你不能直接写入缓存,

所以这对我们来说不是一个好的解决方案。

因此,现代处理器当然使用DDR很多,

所以我们将使用它作为我们的例子。

我们有一些DDR,将输入数据存储

在DDR中。

这个过程的下一部分

是实际的处理部分,

然后开始通过中断核心让

它知道它有一个输入进行处理。

然后我们可以通过将其读入处理器

然后将其写回来进行处理。

这就是我们控制循环的处理部分。

我们将展示数据读取到核心,

处理,当然,我们会将其

作为本地输出写回来。

为了完成控制循环

并至少将其恢复到物理过程,

我们需要将输出写入输出设备。

这是我们这样做的方法。

所以这才是真正的全过程。

我们将把这一切都搞定,这样你就能看到一切。

输入,那里的核心,

过程,输出,

大量的通信和同步。

我们现在了解了概念,

你可能会对整体情况有所了解。

当然,我们希望有足够的时间

来完成物理过程

以满足我们的最后期限,

并且我们控制的系统可以正确控制,

以便它能够完成它的设计目标。

好吧,当一切正常时,这一切都很好,

但是工作有点出错。

例如,如果我们的输入需要更长时间,会发生什么?

什么会导致这种情况发生?

所以在这里我们将展示你的输入正在延长,

超出了我们刚才看到的第一个

例子中的时间。

有一些延迟是从第一次

输入完成时添加的。

所以现在这个输入花费的时间比那个更长,

当然,如果我们的处理花费相同的时间

并且我们的输出需要相同的时间,

那么在物理过程完成之前

可能不会留下足够的时间满足期限要求,

这当然会导致我们的

控制系统出现问题。

所以这不好。

控制回路设计系统中的延迟很糟糕。

因此,我们希望学会避免,

我们希望看到我们如何能够构建这个系统 -

特别是处理器 -

以便能够避免这些延迟或管理它们。

那么我们怎么能以不同的方式做到这一点,

至少可以控制延迟?

让我们来看看我们正在尝试的方法。

我们将数据带入DDR。

我们中断核心。

但是在这个例子中,如果核心不能立即服务

中断怎么办?

也许它正在忙于做其他事情,

而且它不能做到这一点,

当然,这会延迟处理。

我们可以尝试通过安排来处理这个问题。

所以你可以使用基于优先级的

调度算法,这是你最重要的事情,

所以当发生这种情况时, 停止你正在做的事情并去做优先事项。

并且您可以以更物理的方式使用嵌套中断

来执行此操作。

这些都是很好的例子,但有时它们只会

让你止步于此,并且很难在复杂系统的

每个环境中构建

并验证它。

所以这可能很有用,

但特别是当我们以1到2千兆赫兹的

速度点击处理器时,或者我们受到限制时, 这会让你止步于此。

所以你可能想要一些更好的东西,

所以我们将看一个不同的解决方案,

允许在处理器忙时导入数据,

并在读取DDR输入之前导致延迟。

我们将通过添加更多内核来实现这一目标。

这将成为整个演示文稿中

的一个共同主题 -

为了使您能够管理延迟,当然,适当、一致和系统地

处理您的期限,

很多时候您需要按顺序

进行特定的资源分配处理实时数据。

这将是第一个例子。

我们要添加一个核心 - 所以这就是新核心。

而这将允许我们做的是

用一个核心管理中断,

并为梯形逻辑提供另一个核心。

然后你的梯形逻辑可以不断地拉动,

或者不管它需要做什么来找出 - 去获得

新的输入。

只要你的循环时间和阶梯逻辑是合适的,

就应该没问题。

因此,这是添加另一个核心的示例,

以便您可以管理延迟并摆脱它,

对于控制器处理,

这就是我们想要做的。

让我们来看另一个

可能出现延迟的例子。

所以我们有两个核心。

我们已经解决了部分问题。

但另一个延迟可以从哪里来?

这将是我们正在使用的内存类型。

所以我们来到这里。

我们写或输入DDR。

我们中断处理器。

我们有一个专用的核心,所以你可以得到数据。

但是,如果要获得数据,DDR会恨忙吗?

在我们看到核心繁忙之前。

现在核心可用,但DDR必须刷新。

这会将数据延迟一些,

并将我们的延迟带回控制回路

并对我们的系统造成严重破坏。

我们不希望这种情况发生,那么我们

如何解决这个问题呢?

想一想。你可以做到的一种

方法是获得更多的记忆体。

我们将为设备添加一些片上存储器。

我们的数据延迟。

我们不希望这样,所以我们

将添加片上存储器,以便存储我们的时间关键数据。

与我们之前谈到的缓存不同,

芯片存储器可以直接写入。

因此,我们将输入数据从DDR

移至内部SRAM,这样我们就可以

直接在那里写入并使用它

来处理核心,内部SRAM

不会出现刷新问题或

可能与DDR相关的延迟其他问题,

这也使我们能够摆脱这种延迟。

所以我们为核心处理添加了核心。

现在我们已经增加了内存,因此我们通过内部存储器

获得了实时数据的特定路径,

这样我们就可以避免DDR延迟。

让我们继续。

现在,我们已经为我们的实时数据提供了良好的途径。

因此,我们在此处显示 - 您的实时数据的

输入和输出通过工业以太网,

进入内部存储器,并由您的一个核心

用于处理。

如果我们需要,还有其他核心用于

中断和其他一些内务管理。

这对于实时路径都有好处,

但其他呢?

正如您所预料的那样,现代系统

需要的不仅仅是处理实时数据。

他们经常也必须处理其他数据。

那就是非实时数据。

这可以是管理数据,元数据。

对整个操作系统来说这很重要,

但它不是闭环的一部分,

或者是一个非常松散的闭环。

因此,它没有我们一直在关注的

这些实时期限,

这会导致系统以灾难性的方式影响系统,

从而导致系统真正失败。

因此,我们还有其他需要

流经系统的非实时数据,

并且它不需要干扰我们的实时数据。

这就是我们在深灰色

和紫色中显示的数据。

所以我们的非实时数据 -

当我们将它添加到系统中时,

是否会导致实时数据出现问题?

当然,如果你没有把事情做好,

它肯定会进入并开始造成麻烦,

因为如果它经过相同的资源,

这些资源可能会被很多非实时数据所消耗,

因为这会导致

实时数据错过时间。

你可能会看到这里发生的一个地方

是在工业以太网的队列中。

如果它们的设计不正确,

如果你有一个队列来存储所有这些数据,

那么当然会有一些非实时数据

进入并阻塞这些队列,

导致你的实时数据被卡在非实时数据,

无法满足期限要求。

所以我们需要以不同的方式构建。

当然,我们要这样做的方式

与核心和内存非常相似。

我们将添加一些冗余资源,

并专门用于实时数据。

所以我们将添加更多队列。

如果愿意的话,我们会通过这些新的实时 线索传递我们的

实时数据。

我们将通过非实时时间队列

传递非实时数据。

当然,我们可以将这些存储在DDR中。

所以现在我们为实时数据

和非实时数据提供了单独的路径。

这会花费我们更多的资源,

但如果我们需要解决这个问题并可靠地解决它,

那么这是一个很好的设计。

让我们来看看另一个

可能会遇到一些问题的地方。

那这个呢总线结构,

所有数据仍然流经的总线?

那个总线不够宽和足够快,

可能会导致问题。

再次,它是一个单一的资源,

所以我们可能要做的是继续添加更多的总线,

以便我们有一个专用的总线用于我们的实时数据,

然后我们可以使用非实时总线

用于我们的非实时数据。

因此,我们将添加另一条总线,

通过它传递我们的实时数据,

然后通过另一条总线获取非实时数据。

所以现在我们已经采用了相当多的系统,

我们已经添加了特定的部分来处理这些实时数据,

我们已经允许非实时数据的其他部分,

以便您可以设计一个系统管理

并取得成功。

我们谈到的中间部分大块是互连,

这显然非常重要。

它正在进行所有数据移动。

我们谈到了增加总线的问题。

我们增加了更多内存。

我们添加了更多内核。

我们有很多不同的东西

需要通过这种互连进行通信

和发送数据,而这种互连

需要以能够管理它的方式进行设计。

它需要知道实时数据是什么

以及非实时数据是什么,

并确保它可以保持实时数据的

时序约束。

互连的一个最大问题是

你有大量的非实时数据,

你开始大转移 -

通过以太网到DDR--

并且互连专用了大量资源来

尽可能快地完成,

但随后实时传输量很小,

必须等待大传输。

显然,这不是一个好的设计,

所以我们需要一个互连,以确保

您的实时数据仍然可以传输,

即使有大量非实时

数据传输。

所以我们很好地构建了它。

稍微改变视图

并查看该系统的不同方面。

我们已经很好地研究了芯片的内部结构,

但让我们考虑一下以太网的实际物理介质,

看看这是否

可能导致延迟。

当我们开始将流量放在那个

以太网传输介质上时,该介质真的会成为

延迟的原因吗?

当然,它可以,取决于可用的

带宽和它的架构。

它当然可能成为一个问题,

其中一堆非实时数据

通过该总线并使用它,您的实时数据

无法传输,等等。

因此,实际的以太网本身

可能是导致系统延迟的原因。

你可以看到,因为所有东西

都在使用这条线,

而且我们的延迟图片

显示我们在系统中遇到了延迟。

无论是否在处理器中发生,

如果它是系统中的延迟,那将导致问题。

因此,以太网本身可能成为一个问题,

因此我们需要一个解决方案。

我们需要看一下一些新的

现代工业以太网方法。

当然,要考虑的是TSN。

就像我们今天在讨论的

其余部分中所做的那样,

为RT数据提供单独的路径到非RT数据,

这样RT数据总是可以在需要时连线,

并且可以使非RT数据等待

或使用不同的时序,以便RT数据

可以获得它需要的优先级。

这是对此的最后一种看法,

因为我们已经完成整个系统

并系统地消除了一些延迟。

让我们考虑一下整个系统

以及它将如何运作。

如果我们想要同时做事,

那么其中一个重大问题就会变成什么?

每个人都同意在同一时间做某事。

我们如何确保系统能够做到这一点?

请记住,这可能是一个非常大的系统。

我们谈到了234 PLC的行李仓库,

整个系统试图一起工作。

但这可以像你和你的同事

试图组织午餐一样简单。

你们都同意:中午

我们会一起去。

而且你想要在正确的时间去,

这样你就可以高效,有组织等

所以这实际上只是

您尝试进行时间同步的任何系统。

当然,你需要做的第一件事是

你需要一个时间基础。

所以每个人都需要钟表或手表,

这取决于你自己的方式。

所以我们将这些添加到我们的图表中,

每个人都会尝试同时做某事。

如果你这样做,输入的表运行缓慢,

会发生什么?

每个人都同意我们会在1:30做一些事情,

但输入的手表很慢,

所以当它在1:30读取时,会发生什么?

这真的晚了五分钟,对吗?

并且迟到五分钟的输入

结果看起来像我们之前

谈到的延迟。

所以这是我们的延迟。

如果输入读取的时间较晚,因为它的表速度很慢,

那么对于其他系统来说,它看起来就像是一个延迟。

输入成为你午餐会议

总是迟到五分钟的那个人,

并使你成为自助餐厅队列中的最后一人。

因此,我们想要解决的问题

当然是拥有一个强大的同步系统,

整个系统中的所有手表组织良好,

系统实际上遵循这些时间,

以便您的同事不能总是

五分钟迟到吃午饭。

因此,时间同步对于消除系统中的延迟也很重要,

并且它将成为我们

将如何在系统中处理此类活动的

策略之一。

本节内容到此结束,

我们已经彻底地说明了

一个过程或体系结构,并查看了几个可以

将延迟引入系统的地方,

以及这种延迟对系统的影响。

这是我们查看所有这些并通过内核

和内存以及包管理的方式队列,

总线,互连。

我们谈到的最后几件事

是实际的以太网接口本身,

以及整个系统的时间同步。

这些都是概念,如果我们

将它们应用到芯片架构中,

我们希望能够构建一个对闭环处理

非常有效的芯片,

并且是PLC的理想选择。

我希望你喜欢这个演讲。

感谢各位。

如果您想获得更多信息,

特别是AM654x,

我会为您提供更多资源。

我们有更多的培训。

可供您选择。

你也可以去看看。

当然,就数据表,

技术参考手册而言,我们在网上有大量信息

包括您需要进行设计的所有不同内容。

我们还为AM65x系列提供软件。

我们有板、评估模块

和工业开发套件。

当然,我们很乐意通过我们的支持论坛

为您提供支持,您可以搜索

已经提出的问题,

希望这对您有所帮助。

如果没有,您可以提出一个新问题,

我们会尽力帮助您。

再次,非常感谢,

希望各位一切顺利。

谢谢。

你好。 感谢您选择观看此视频, 本视频的主题是“为工业应用 构建工业ARM-- AM65xx架构差异化”。 这是系列的第2部分, 这部分称为管理延迟。 在本系列的第一部分中, 我们了解了一个名为行李仓库的 现代自动化系统。 这是一个在迪拜国际机场 使用的行李处理系统, 它是一个现代化的自动化系统, 与许多不同的组件一起构建, 可以自动处理行李。 任何旅行的人都知道 你什么时候登机行李并进入飞机 - 并希望它能 在目的地的机场回到你身边 - 这个行李肯定有很有趣的经历, 这涉及一个新方法。 这是我们尝试用现代 自动化系统做的一个很好的例子。 我们谈到了这样一个事实, 即系统由234个PLC或可编程逻辑控制器, 以及大量的输入和输出 以及电机驱动器和许多其他东西组成。 我们进入其中一个PLC, 看看它中使用的处理器是如何构建的, 以及它将要进行的 处理类型。 如果你还未弄明白, 我希望这次你会。 有一个行李处理系统的视频, 你也可以去看看。 这非常有趣,它为这次讨论 设定了良好的背景,我们将讨论 如何使用现代处理器来管理延迟。 所以让我们再深入探讨一下。 这是我们从最后一节构建的 处理器,你可以看到这个处理器 连接到某些输入和输出, 可能通过工业,以太网类型的 应用程序。 如果你一起构建它 并在其周围放置许多其他有趣的东西, 那就是如何构建PLC。 请记住,我们正在进行的处理类型 是受控处理。 所以这里有一个例子,它显示了底部的 物理过程,输入和输出正在处理中, 这是传感器的实际读数 和电机的移动。 然后将该输入传输到 处理器进行处理。 很多时候,在PLC中,这是横向逻辑。 然后,当然,计算输出并将其 放回以用于完成整个 过程的物理过程。 控制循环处理的有趣之处很多, 这必须在非常具体的 时间完成。 我们称之为截止期限。 现在,截止期限的严重程度因系统而异, 但有时可能会非常严重, 导致整个系统崩溃 甚至造成伤害或生命损失。 所以这些可能是非常严重的系统, 当然,它们需要以不符合这些期限的 方式进行架构。 那么让我们来看看这个处理器的组件。 我们正在深入研究这个处理器 需要具备的内容,以便更好地适应这种整体架构。 当然,第一个组件是 实际与输入和输出通信的一种方式。 我们称之为工业以太网接口。 很多时候,这也有移动数据的线索。 接下来的部分只是将这些数据 连接到系统的其他部分, 我们将其称为通用总线 和互连。 这主要用于数据移动。 最后一部分是我们都在思考的部分, 这是实际的处理核心。 很多时候,它们会在进行 处理操作时附带一些 用于本地存储数据的缓存。 因此,让我们在这个过程的输入部分进入区域 - 即将发生的物理过程。 我们需要将输入传输到处理器, 以便将其输入正在使用的 控制算法中。 所以在这里我们将展示来自输入的数据, 通过工业以太网传输。 然后问题就变成, 一旦它进入处理器,我们将它放在哪里? 我们如何储存它? 显然,我们需要某种记忆体。 从延迟的角度来看,将它直接 放在核心的缓存中可能会很好, 但是你不能直接写入缓存, 所以这对我们来说不是一个好的解决方案。 因此,现代处理器当然使用DDR很多, 所以我们将使用它作为我们的例子。 我们有一些DDR,将输入数据存储 在DDR中。 这个过程的下一部分 是实际的处理部分, 然后开始通过中断核心让 它知道它有一个输入进行处理。 然后我们可以通过将其读入处理器 然后将其写回来进行处理。 这就是我们控制循环的处理部分。 我们将展示数据读取到核心, 处理,当然,我们会将其 作为本地输出写回来。 为了完成控制循环 并至少将其恢复到物理过程, 我们需要将输出写入输出设备。 这是我们这样做的方法。 所以这才是真正的全过程。 我们将把这一切都搞定,这样你就能看到一切。 输入,那里的核心, 过程,输出, 大量的通信和同步。 我们现在了解了概念, 你可能会对整体情况有所了解。 当然,我们希望有足够的时间 来完成物理过程 以满足我们的最后期限, 并且我们控制的系统可以正确控制, 以便它能够完成它的设计目标。 好吧,当一切正常时,这一切都很好, 但是工作有点出错。 例如,如果我们的输入需要更长时间,会发生什么? 什么会导致这种情况发生? 所以在这里我们将展示你的输入正在延长, 超出了我们刚才看到的第一个 例子中的时间。 有一些延迟是从第一次 输入完成时添加的。 所以现在这个输入花费的时间比那个更长, 当然,如果我们的处理花费相同的时间 并且我们的输出需要相同的时间, 那么在物理过程完成之前 可能不会留下足够的时间满足期限要求, 这当然会导致我们的 控制系统出现问题。 所以这不好。 控制回路设计系统中的延迟很糟糕。 因此,我们希望学会避免, 我们希望看到我们如何能够构建这个系统 - 特别是处理器 - 以便能够避免这些延迟或管理它们。 那么我们怎么能以不同的方式做到这一点, 至少可以控制延迟? 让我们来看看我们正在尝试的方法。 我们将数据带入DDR。 我们中断核心。 但是在这个例子中,如果核心不能立即服务 中断怎么办? 也许它正在忙于做其他事情, 而且它不能做到这一点, 当然,这会延迟处理。 我们可以尝试通过安排来处理这个问题。 所以你可以使用基于优先级的 调度算法,这是你最重要的事情, 所以当发生这种情况时, 停止你正在做的事情并去做优先事项。 并且您可以以更物理的方式使用嵌套中断 来执行此操作。 这些都是很好的例子,但有时它们只会 让你止步于此,并且很难在复杂系统的 每个环境中构建 并验证它。 所以这可能很有用, 但特别是当我们以1到2千兆赫兹的 速度点击处理器时,或者我们受到限制时, 这会让你止步于此。 所以你可能想要一些更好的东西, 所以我们将看一个不同的解决方案, 允许在处理器忙时导入数据, 并在读取DDR输入之前导致延迟。 我们将通过添加更多内核来实现这一目标。 这将成为整个演示文稿中 的一个共同主题 - 为了使您能够管理延迟,当然,适当、一致和系统地 处理您的期限, 很多时候您需要按顺序 进行特定的资源分配处理实时数据。 这将是第一个例子。 我们要添加一个核心 - 所以这就是新核心。 而这将允许我们做的是 用一个核心管理中断, 并为梯形逻辑提供另一个核心。 然后你的梯形逻辑可以不断地拉动, 或者不管它需要做什么来找出 - 去获得 新的输入。 只要你的循环时间和阶梯逻辑是合适的, 就应该没问题。 因此,这是添加另一个核心的示例, 以便您可以管理延迟并摆脱它, 对于控制器处理, 这就是我们想要做的。 让我们来看另一个 可能出现延迟的例子。 所以我们有两个核心。 我们已经解决了部分问题。 但另一个延迟可以从哪里来? 这将是我们正在使用的内存类型。 所以我们来到这里。 我们写或输入DDR。 我们中断处理器。 我们有一个专用的核心,所以你可以得到数据。 但是,如果要获得数据,DDR会恨忙吗? 在我们看到核心繁忙之前。 现在核心可用,但DDR必须刷新。 这会将数据延迟一些, 并将我们的延迟带回控制回路 并对我们的系统造成严重破坏。 我们不希望这种情况发生,那么我们 如何解决这个问题呢? 想一想。你可以做到的一种 方法是获得更多的记忆体。 我们将为设备添加一些片上存储器。 我们的数据延迟。 我们不希望这样,所以我们 将添加片上存储器,以便存储我们的时间关键数据。 与我们之前谈到的缓存不同, 芯片存储器可以直接写入。 因此,我们将输入数据从DDR 移至内部SRAM,这样我们就可以 直接在那里写入并使用它 来处理核心,内部SRAM 不会出现刷新问题或 可能与DDR相关的延迟其他问题, 这也使我们能够摆脱这种延迟。 所以我们为核心处理添加了核心。 现在我们已经增加了内存,因此我们通过内部存储器 获得了实时数据的特定路径, 这样我们就可以避免DDR延迟。 让我们继续。 现在,我们已经为我们的实时数据提供了良好的途径。 因此,我们在此处显示 - 您的实时数据的 输入和输出通过工业以太网, 进入内部存储器,并由您的一个核心 用于处理。 如果我们需要,还有其他核心用于 中断和其他一些内务管理。 这对于实时路径都有好处, 但其他呢? 正如您所预料的那样,现代系统 需要的不仅仅是处理实时数据。 他们经常也必须处理其他数据。 那就是非实时数据。 这可以是管理数据,元数据。 对整个操作系统来说这很重要, 但它不是闭环的一部分, 或者是一个非常松散的闭环。 因此,它没有我们一直在关注的 这些实时期限, 这会导致系统以灾难性的方式影响系统, 从而导致系统真正失败。 因此,我们还有其他需要 流经系统的非实时数据, 并且它不需要干扰我们的实时数据。 这就是我们在深灰色 和紫色中显示的数据。 所以我们的非实时数据 - 当我们将它添加到系统中时, 是否会导致实时数据出现问题? 当然,如果你没有把事情做好, 它肯定会进入并开始造成麻烦, 因为如果它经过相同的资源, 这些资源可能会被很多非实时数据所消耗, 因为这会导致 实时数据错过时间。 你可能会看到这里发生的一个地方 是在工业以太网的队列中。 如果它们的设计不正确, 如果你有一个队列来存储所有这些数据, 那么当然会有一些非实时数据 进入并阻塞这些队列, 导致你的实时数据被卡在非实时数据, 无法满足期限要求。 所以我们需要以不同的方式构建。 当然,我们要这样做的方式 与核心和内存非常相似。 我们将添加一些冗余资源, 并专门用于实时数据。 所以我们将添加更多队列。 如果愿意的话,我们会通过这些新的实时 线索传递我们的 实时数据。 我们将通过非实时时间队列 传递非实时数据。 当然,我们可以将这些存储在DDR中。 所以现在我们为实时数据 和非实时数据提供了单独的路径。 这会花费我们更多的资源, 但如果我们需要解决这个问题并可靠地解决它, 那么这是一个很好的设计。 让我们来看看另一个 可能会遇到一些问题的地方。 那这个呢总线结构, 所有数据仍然流经的总线? 那个总线不够宽和足够快, 可能会导致问题。 再次,它是一个单一的资源, 所以我们可能要做的是继续添加更多的总线, 以便我们有一个专用的总线用于我们的实时数据, 然后我们可以使用非实时总线 用于我们的非实时数据。 因此,我们将添加另一条总线, 通过它传递我们的实时数据, 然后通过另一条总线获取非实时数据。 所以现在我们已经采用了相当多的系统, 我们已经添加了特定的部分来处理这些实时数据, 我们已经允许非实时数据的其他部分, 以便您可以设计一个系统管理 并取得成功。 我们谈到的中间部分大块是互连, 这显然非常重要。 它正在进行所有数据移动。 我们谈到了增加总线的问题。 我们增加了更多内存。 我们添加了更多内核。 我们有很多不同的东西 需要通过这种互连进行通信 和发送数据,而这种互连 需要以能够管理它的方式进行设计。 它需要知道实时数据是什么 以及非实时数据是什么, 并确保它可以保持实时数据的 时序约束。 互连的一个最大问题是 你有大量的非实时数据, 你开始大转移 - 通过以太网到DDR-- 并且互连专用了大量资源来 尽可能快地完成, 但随后实时传输量很小, 必须等待大传输。 显然,这不是一个好的设计, 所以我们需要一个互连,以确保 您的实时数据仍然可以传输, 即使有大量非实时 数据传输。 所以我们很好地构建了它。 稍微改变视图 并查看该系统的不同方面。 我们已经很好地研究了芯片的内部结构, 但让我们考虑一下以太网的实际物理介质, 看看这是否 可能导致延迟。 当我们开始将流量放在那个 以太网传输介质上时,该介质真的会成为 延迟的原因吗? 当然,它可以,取决于可用的 带宽和它的架构。 它当然可能成为一个问题, 其中一堆非实时数据 通过该总线并使用它,您的实时数据 无法传输,等等。 因此,实际的以太网本身 可能是导致系统延迟的原因。 你可以看到,因为所有东西 都在使用这条线, 而且我们的延迟图片 显示我们在系统中遇到了延迟。 无论是否在处理器中发生, 如果它是系统中的延迟,那将导致问题。 因此,以太网本身可能成为一个问题, 因此我们需要一个解决方案。 我们需要看一下一些新的 现代工业以太网方法。 当然,要考虑的是TSN。 就像我们今天在讨论的 其余部分中所做的那样, 为RT数据提供单独的路径到非RT数据, 这样RT数据总是可以在需要时连线, 并且可以使非RT数据等待 或使用不同的时序,以便RT数据 可以获得它需要的优先级。 这是对此的最后一种看法, 因为我们已经完成整个系统 并系统地消除了一些延迟。 让我们考虑一下整个系统 以及它将如何运作。 如果我们想要同时做事, 那么其中一个重大问题就会变成什么? 每个人都同意在同一时间做某事。 我们如何确保系统能够做到这一点? 请记住,这可能是一个非常大的系统。 我们谈到了234 PLC的行李仓库, 整个系统试图一起工作。 但这可以像你和你的同事 试图组织午餐一样简单。 你们都同意:中午 我们会一起去。 而且你想要在正确的时间去, 这样你就可以高效,有组织等 所以这实际上只是 您尝试进行时间同步的任何系统。 当然,你需要做的第一件事是 你需要一个时间基础。 所以每个人都需要钟表或手表, 这取决于你自己的方式。 所以我们将这些添加到我们的图表中, 每个人都会尝试同时做某事。 如果你这样做,输入的表运行缓慢, 会发生什么? 每个人都同意我们会在1:30做一些事情, 但输入的手表很慢, 所以当它在1:30读取时,会发生什么? 这真的晚了五分钟,对吗? 并且迟到五分钟的输入 结果看起来像我们之前 谈到的延迟。 所以这是我们的延迟。 如果输入读取的时间较晚,因为它的表速度很慢, 那么对于其他系统来说,它看起来就像是一个延迟。 输入成为你午餐会议 总是迟到五分钟的那个人, 并使你成为自助餐厅队列中的最后一人。 因此,我们想要解决的问题 当然是拥有一个强大的同步系统, 整个系统中的所有手表组织良好, 系统实际上遵循这些时间, 以便您的同事不能总是 五分钟迟到吃午饭。 因此,时间同步对于消除系统中的延迟也很重要, 并且它将成为我们 将如何在系统中处理此类活动的 策略之一。 本节内容到此结束, 我们已经彻底地说明了 一个过程或体系结构,并查看了几个可以 将延迟引入系统的地方, 以及这种延迟对系统的影响。 这是我们查看所有这些并通过内核 和内存以及包管理的方式队列, 总线,互连。 我们谈到的最后几件事 是实际的以太网接口本身, 以及整个系统的时间同步。 这些都是概念,如果我们 将它们应用到芯片架构中, 我们希望能够构建一个对闭环处理 非常有效的芯片, 并且是PLC的理想选择。 我希望你喜欢这个演讲。 感谢各位。 如果您想获得更多信息, 特别是AM654x, 我会为您提供更多资源。 我们有更多的培训。 可供您选择。 你也可以去看看。 当然,就数据表, 技术参考手册而言,我们在网上有大量信息 包括您需要进行设计的所有不同内容。 我们还为AM65x系列提供软件。 我们有板、评估模块 和工业开发套件。 当然,我们很乐意通过我们的支持论坛 为您提供支持,您可以搜索 已经提出的问题, 希望这对您有所帮助。 如果没有,您可以提出一个新问题, 我们会尽力帮助您。 再次,非常感谢, 希望各位一切顺利。 谢谢。

你好。

感谢您选择观看此视频,

本视频的主题是“为工业应用

构建工业ARM--

AM65xx架构差异化”。

这是系列的第2部分,

这部分称为管理延迟。

在本系列的第一部分中,

我们了解了一个名为行李仓库的

现代自动化系统。

这是一个在迪拜国际机场

使用的行李处理系统,

它是一个现代化的自动化系统,

与许多不同的组件一起构建,

可以自动处理行李。

任何旅行的人都知道

你什么时候登机行李并进入飞机 -

并希望它能

在目的地的机场回到你身边 -

这个行李肯定有很有趣的经历,

这涉及一个新方法。

这是我们尝试用现代

自动化系统做的一个很好的例子。

我们谈到了这样一个事实,

即系统由234个PLC或可编程逻辑控制器,

以及大量的输入和输出

以及电机驱动器和许多其他东西组成。

我们进入其中一个PLC,

看看它中使用的处理器是如何构建的,

以及它将要进行的

处理类型。

如果你还未弄明白,

我希望这次你会。

有一个行李处理系统的视频,

你也可以去看看。

这非常有趣,它为这次讨论

设定了良好的背景,我们将讨论

如何使用现代处理器来管理延迟。

所以让我们再深入探讨一下。

这是我们从最后一节构建的

处理器,你可以看到这个处理器

连接到某些输入和输出,

可能通过工业,以太网类型的

应用程序。

如果你一起构建它

并在其周围放置许多其他有趣的东西,

那就是如何构建PLC。

请记住,我们正在进行的处理类型

是受控处理。

所以这里有一个例子,它显示了底部的

物理过程,输入和输出正在处理中,

这是传感器的实际读数

和电机的移动。

然后将该输入传输到

处理器进行处理。

很多时候,在PLC中,这是横向逻辑。

然后,当然,计算输出并将其

放回以用于完成整个

过程的物理过程。

控制循环处理的有趣之处很多,

这必须在非常具体的

时间完成。

我们称之为截止期限。

现在,截止期限的严重程度因系统而异,

但有时可能会非常严重,

导致整个系统崩溃

甚至造成伤害或生命损失。

所以这些可能是非常严重的系统,

当然,它们需要以不符合这些期限的

方式进行架构。

那么让我们来看看这个处理器的组件。

我们正在深入研究这个处理器

需要具备的内容,以便更好地适应这种整体架构。

当然,第一个组件是

实际与输入和输出通信的一种方式。

我们称之为工业以太网接口。

很多时候,这也有移动数据的线索。

接下来的部分只是将这些数据

连接到系统的其他部分,

我们将其称为通用总线

和互连。

这主要用于数据移动。

最后一部分是我们都在思考的部分,

这是实际的处理核心。

很多时候,它们会在进行

处理操作时附带一些

用于本地存储数据的缓存。

因此,让我们在这个过程的输入部分进入区域 -

即将发生的物理过程。

我们需要将输入传输到处理器,

以便将其输入正在使用的

控制算法中。

所以在这里我们将展示来自输入的数据,

通过工业以太网传输。

然后问题就变成,

一旦它进入处理器,我们将它放在哪里?

我们如何储存它?

显然,我们需要某种记忆体。

从延迟的角度来看,将它直接

放在核心的缓存中可能会很好,

但是你不能直接写入缓存,

所以这对我们来说不是一个好的解决方案。

因此,现代处理器当然使用DDR很多,

所以我们将使用它作为我们的例子。

我们有一些DDR,将输入数据存储

在DDR中。

这个过程的下一部分

是实际的处理部分,

然后开始通过中断核心让

它知道它有一个输入进行处理。

然后我们可以通过将其读入处理器

然后将其写回来进行处理。

这就是我们控制循环的处理部分。

我们将展示数据读取到核心,

处理,当然,我们会将其

作为本地输出写回来。

为了完成控制循环

并至少将其恢复到物理过程,

我们需要将输出写入输出设备。

这是我们这样做的方法。

所以这才是真正的全过程。

我们将把这一切都搞定,这样你就能看到一切。

输入,那里的核心,

过程,输出,

大量的通信和同步。

我们现在了解了概念,

你可能会对整体情况有所了解。

当然,我们希望有足够的时间

来完成物理过程

以满足我们的最后期限,

并且我们控制的系统可以正确控制,

以便它能够完成它的设计目标。

好吧,当一切正常时,这一切都很好,

但是工作有点出错。

例如,如果我们的输入需要更长时间,会发生什么?

什么会导致这种情况发生?

所以在这里我们将展示你的输入正在延长,

超出了我们刚才看到的第一个

例子中的时间。

有一些延迟是从第一次

输入完成时添加的。

所以现在这个输入花费的时间比那个更长,

当然,如果我们的处理花费相同的时间

并且我们的输出需要相同的时间,

那么在物理过程完成之前

可能不会留下足够的时间满足期限要求,

这当然会导致我们的

控制系统出现问题。

所以这不好。

控制回路设计系统中的延迟很糟糕。

因此,我们希望学会避免,

我们希望看到我们如何能够构建这个系统 -

特别是处理器 -

以便能够避免这些延迟或管理它们。

那么我们怎么能以不同的方式做到这一点,

至少可以控制延迟?

让我们来看看我们正在尝试的方法。

我们将数据带入DDR。

我们中断核心。

但是在这个例子中,如果核心不能立即服务

中断怎么办?

也许它正在忙于做其他事情,

而且它不能做到这一点,

当然,这会延迟处理。

我们可以尝试通过安排来处理这个问题。

所以你可以使用基于优先级的

调度算法,这是你最重要的事情,

所以当发生这种情况时, 停止你正在做的事情并去做优先事项。

并且您可以以更物理的方式使用嵌套中断

来执行此操作。

这些都是很好的例子,但有时它们只会

让你止步于此,并且很难在复杂系统的

每个环境中构建

并验证它。

所以这可能很有用,

但特别是当我们以1到2千兆赫兹的

速度点击处理器时,或者我们受到限制时, 这会让你止步于此。

所以你可能想要一些更好的东西,

所以我们将看一个不同的解决方案,

允许在处理器忙时导入数据,

并在读取DDR输入之前导致延迟。

我们将通过添加更多内核来实现这一目标。

这将成为整个演示文稿中

的一个共同主题 -

为了使您能够管理延迟,当然,适当、一致和系统地

处理您的期限,

很多时候您需要按顺序

进行特定的资源分配处理实时数据。

这将是第一个例子。

我们要添加一个核心 - 所以这就是新核心。

而这将允许我们做的是

用一个核心管理中断,

并为梯形逻辑提供另一个核心。

然后你的梯形逻辑可以不断地拉动,

或者不管它需要做什么来找出 - 去获得

新的输入。

只要你的循环时间和阶梯逻辑是合适的,

就应该没问题。

因此,这是添加另一个核心的示例,

以便您可以管理延迟并摆脱它,

对于控制器处理,

这就是我们想要做的。

让我们来看另一个

可能出现延迟的例子。

所以我们有两个核心。

我们已经解决了部分问题。

但另一个延迟可以从哪里来?

这将是我们正在使用的内存类型。

所以我们来到这里。

我们写或输入DDR。

我们中断处理器。

我们有一个专用的核心,所以你可以得到数据。

但是,如果要获得数据,DDR会恨忙吗?

在我们看到核心繁忙之前。

现在核心可用,但DDR必须刷新。

这会将数据延迟一些,

并将我们的延迟带回控制回路

并对我们的系统造成严重破坏。

我们不希望这种情况发生,那么我们

如何解决这个问题呢?

想一想。你可以做到的一种

方法是获得更多的记忆体。

我们将为设备添加一些片上存储器。

我们的数据延迟。

我们不希望这样,所以我们

将添加片上存储器,以便存储我们的时间关键数据。

与我们之前谈到的缓存不同,

芯片存储器可以直接写入。

因此,我们将输入数据从DDR

移至内部SRAM,这样我们就可以

直接在那里写入并使用它

来处理核心,内部SRAM

不会出现刷新问题或

可能与DDR相关的延迟其他问题,

这也使我们能够摆脱这种延迟。

所以我们为核心处理添加了核心。

现在我们已经增加了内存,因此我们通过内部存储器

获得了实时数据的特定路径,

这样我们就可以避免DDR延迟。

让我们继续。

现在,我们已经为我们的实时数据提供了良好的途径。

因此,我们在此处显示 - 您的实时数据的

输入和输出通过工业以太网,

进入内部存储器,并由您的一个核心

用于处理。

如果我们需要,还有其他核心用于

中断和其他一些内务管理。

这对于实时路径都有好处,

但其他呢?

正如您所预料的那样,现代系统

需要的不仅仅是处理实时数据。

他们经常也必须处理其他数据。

那就是非实时数据。

这可以是管理数据,元数据。

对整个操作系统来说这很重要,

但它不是闭环的一部分,

或者是一个非常松散的闭环。

因此,它没有我们一直在关注的

这些实时期限,

这会导致系统以灾难性的方式影响系统,

从而导致系统真正失败。

因此,我们还有其他需要

流经系统的非实时数据,

并且它不需要干扰我们的实时数据。

这就是我们在深灰色

和紫色中显示的数据。

所以我们的非实时数据 -

当我们将它添加到系统中时,

是否会导致实时数据出现问题?

当然,如果你没有把事情做好,

它肯定会进入并开始造成麻烦,

因为如果它经过相同的资源,

这些资源可能会被很多非实时数据所消耗,

因为这会导致

实时数据错过时间。

你可能会看到这里发生的一个地方

是在工业以太网的队列中。

如果它们的设计不正确,

如果你有一个队列来存储所有这些数据,

那么当然会有一些非实时数据

进入并阻塞这些队列,

导致你的实时数据被卡在非实时数据,

无法满足期限要求。

所以我们需要以不同的方式构建。

当然,我们要这样做的方式

与核心和内存非常相似。

我们将添加一些冗余资源,

并专门用于实时数据。

所以我们将添加更多队列。

如果愿意的话,我们会通过这些新的实时 线索传递我们的

实时数据。

我们将通过非实时时间队列

传递非实时数据。

当然,我们可以将这些存储在DDR中。

所以现在我们为实时数据

和非实时数据提供了单独的路径。

这会花费我们更多的资源,

但如果我们需要解决这个问题并可靠地解决它,

那么这是一个很好的设计。

让我们来看看另一个

可能会遇到一些问题的地方。

那这个呢总线结构,

所有数据仍然流经的总线?

那个总线不够宽和足够快,

可能会导致问题。

再次,它是一个单一的资源,

所以我们可能要做的是继续添加更多的总线,

以便我们有一个专用的总线用于我们的实时数据,

然后我们可以使用非实时总线

用于我们的非实时数据。

因此,我们将添加另一条总线,

通过它传递我们的实时数据,

然后通过另一条总线获取非实时数据。

所以现在我们已经采用了相当多的系统,

我们已经添加了特定的部分来处理这些实时数据,

我们已经允许非实时数据的其他部分,

以便您可以设计一个系统管理

并取得成功。

我们谈到的中间部分大块是互连,

这显然非常重要。

它正在进行所有数据移动。

我们谈到了增加总线的问题。

我们增加了更多内存。

我们添加了更多内核。

我们有很多不同的东西

需要通过这种互连进行通信

和发送数据,而这种互连

需要以能够管理它的方式进行设计。

它需要知道实时数据是什么

以及非实时数据是什么,

并确保它可以保持实时数据的

时序约束。

互连的一个最大问题是

你有大量的非实时数据,

你开始大转移 -

通过以太网到DDR--

并且互连专用了大量资源来

尽可能快地完成,

但随后实时传输量很小,

必须等待大传输。

显然,这不是一个好的设计,

所以我们需要一个互连,以确保

您的实时数据仍然可以传输,

即使有大量非实时

数据传输。

所以我们很好地构建了它。

稍微改变视图

并查看该系统的不同方面。

我们已经很好地研究了芯片的内部结构,

但让我们考虑一下以太网的实际物理介质,

看看这是否

可能导致延迟。

当我们开始将流量放在那个

以太网传输介质上时,该介质真的会成为

延迟的原因吗?

当然,它可以,取决于可用的

带宽和它的架构。

它当然可能成为一个问题,

其中一堆非实时数据

通过该总线并使用它,您的实时数据

无法传输,等等。

因此,实际的以太网本身

可能是导致系统延迟的原因。

你可以看到,因为所有东西

都在使用这条线,

而且我们的延迟图片

显示我们在系统中遇到了延迟。

无论是否在处理器中发生,

如果它是系统中的延迟,那将导致问题。

因此,以太网本身可能成为一个问题,

因此我们需要一个解决方案。

我们需要看一下一些新的

现代工业以太网方法。

当然,要考虑的是TSN。

就像我们今天在讨论的

其余部分中所做的那样,

为RT数据提供单独的路径到非RT数据,

这样RT数据总是可以在需要时连线,

并且可以使非RT数据等待

或使用不同的时序,以便RT数据

可以获得它需要的优先级。

这是对此的最后一种看法,

因为我们已经完成整个系统

并系统地消除了一些延迟。

让我们考虑一下整个系统

以及它将如何运作。

如果我们想要同时做事,

那么其中一个重大问题就会变成什么?

每个人都同意在同一时间做某事。

我们如何确保系统能够做到这一点?

请记住,这可能是一个非常大的系统。

我们谈到了234 PLC的行李仓库,

整个系统试图一起工作。

但这可以像你和你的同事

试图组织午餐一样简单。

你们都同意:中午

我们会一起去。

而且你想要在正确的时间去,

这样你就可以高效,有组织等

所以这实际上只是

您尝试进行时间同步的任何系统。

当然,你需要做的第一件事是

你需要一个时间基础。

所以每个人都需要钟表或手表,

这取决于你自己的方式。

所以我们将这些添加到我们的图表中,

每个人都会尝试同时做某事。

如果你这样做,输入的表运行缓慢,

会发生什么?

每个人都同意我们会在1:30做一些事情,

但输入的手表很慢,

所以当它在1:30读取时,会发生什么?

这真的晚了五分钟,对吗?

并且迟到五分钟的输入

结果看起来像我们之前

谈到的延迟。

所以这是我们的延迟。

如果输入读取的时间较晚,因为它的表速度很慢,

那么对于其他系统来说,它看起来就像是一个延迟。

输入成为你午餐会议

总是迟到五分钟的那个人,

并使你成为自助餐厅队列中的最后一人。

因此,我们想要解决的问题

当然是拥有一个强大的同步系统,

整个系统中的所有手表组织良好,

系统实际上遵循这些时间,

以便您的同事不能总是

五分钟迟到吃午饭。

因此,时间同步对于消除系统中的延迟也很重要,

并且它将成为我们

将如何在系统中处理此类活动的

策略之一。

本节内容到此结束,

我们已经彻底地说明了

一个过程或体系结构,并查看了几个可以

将延迟引入系统的地方,

以及这种延迟对系统的影响。

这是我们查看所有这些并通过内核

和内存以及包管理的方式队列,

总线,互连。

我们谈到的最后几件事

是实际的以太网接口本身,

以及整个系统的时间同步。

这些都是概念,如果我们

将它们应用到芯片架构中,

我们希望能够构建一个对闭环处理

非常有效的芯片,

并且是PLC的理想选择。

我希望你喜欢这个演讲。

感谢各位。

如果您想获得更多信息,

特别是AM654x,

我会为您提供更多资源。

我们有更多的培训。

可供您选择。

你也可以去看看。

当然,就数据表,

技术参考手册而言,我们在网上有大量信息

包括您需要进行设计的所有不同内容。

我们还为AM65x系列提供软件。

我们有板、评估模块

和工业开发套件。

当然,我们很乐意通过我们的支持论坛

为您提供支持,您可以搜索

已经提出的问题,

希望这对您有所帮助。

如果没有,您可以提出一个新问题,

我们会尽力帮助您。

再次,非常感谢,

希望各位一切顺利。

谢谢。

手机看

扫码用手机观看

视频简介

视频简介

1.2 管理延迟

所属课程:使用Sitara AM6x培训系列了解工业用ARM

发布时间:2019.08.07

视频集数:2

本节视频时长:00:20:37

该培训着眼于Sitara AM654x(AM6546,AM6548)处理器架构的差异化以及如何使用它来管理工厂自动化中的闭环延迟。

未学习 1.1 控制循环的处理

未学习 1.1 控制循环的处理

未学习 1.2 管理延迟

未学习 1.2 管理延迟

视频简介

视频简介