比较器应用1

Loading the player...

将在30s后自动为您播放下一课程

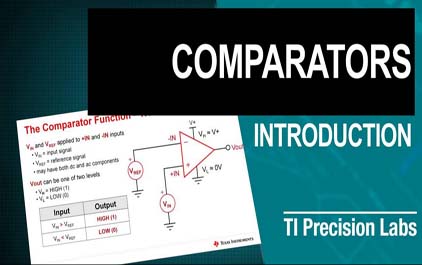

大家好,欢迎观看 TI 高精度实验室 视频系列,其中 介绍比较器应用。 比较器的作用是 比较两个模拟输入 信号并根据该比较 生成数字或逻辑 电平输出。 在本视频中,我们 将讨论模拟比较器的 基本功能及其 部分主要规格, 其中包括输入 失调电压或 VOS。 让我们首先 介绍比较器的 基本功能。 与标准运算放大器 类似,比较器具有 两个输入、一个输出 以及两个电源引脚。 从原理图的角度而言, 它与运算放大器类似, 但其预期功能 大不相同。 比较器之所以得此 名称,是因为它比较 施加到其输入端的 电压并根据输入 电平来设置 其输出电压。 一个输入被视为 主输入信号 或 VIN。 另一个 输入被 视为基准 信号 VREF。 这些输入可能具有 直流和交流分量。 可以将输出电压 Vout 设置为两种电平之一 -- 高电平或逻辑 1, 或者低电平或逻辑 0。 输出高电平 VH 接近于 V+,即正 电源电压。 输出低电平 VL 接近于 0 伏或接地,或双电源 配置中的负电源。 该幻灯片中 显示的比较器 针对同相操作 进行了配置。 在该情况下, 输入信号 VIN 连接到 同相输入 +IN,基准 信号 VREF 连接到反相 输入 -IN。 如果 VIN 大于 VREF, 则比较器输出为高电平。 如果 VIN 小于 VREF, 则比较器输出为低电平。 比较器还可以 用于反相配置。 在该情况下, 输入信号 VIN 连接到反相 输入 -IN, 基准 信号 VREF 连接到 同相输入 +IN。 由于我们 定义输入 信号方式的改变, 可以将输出行为 视为反相。 现在,如果 VIN 大于 VREF, 那么比较器输出为低电平。 如果 VIN 小于 VREF, 则输出为高电平。 让我们来看看 双极比较器 LM139 的简化 内部设计。 此处的目标不是 讲授晶体管理论 或比较器设计的 详细工作原理, 而是为您提供有关比较器 如何工作的一般概念。 蓝色框中 所示的输入级 包含一个 PNP 差分放大器。 该差分级的 每侧都使用 达林顿 PNP 晶体管。 使用达林顿 连接晶体管 可增大输入阻抗, 降低输入偏置电流, 允许共模 输入电压 向下扩展至 0 伏。 该级中每个晶体管的 发射极电路中都具有 电流源,用于设置 发射极电流。 差分输入级中 晶体管的集电极 连接到用作 动态负载的 NPN 晶体管,如 青绿色部分所示。 最后,动态负载级的 输出耦合到 NPN 驱动器和集电极 开路输出级,如紫色 部分所示。 在比较器的 正常运行期间, 差分输入信号 +IN 减去 -IN 由输入差分 放大器的电压 增益进行放大。 该差分级的 输出在 T6 上形成, 并用于打开或 关闭输出级, 具体取决于输入极性。 为了更好地理解 内部功能,现在 让我们向该比较器 施加一些变化的输入 信号,并查看内部 电压在各个级 是如何变化的。 在该示例中, 我们将使用 采用反相配置的 比较器,VREF 连接到 +IN,VIN 连接到 -IN。 让我们首先向 +IN 施加 2.5 伏的基准 电压,向 -IN 施加 2.4 伏的输入信号。 那么我们要将 2.4 伏 与 2.5 伏基准进行比较。 这些电压以红色 显示在各个节点上。 底部提供了输入 为 2.4 伏的情形。 查看 -IN,可以 发现连接到 差分输入对的 该侧的晶体管 连接到动态 负载晶体管 T6。 T6 集电极处的 电压等于由 晶体管 T7 的 基极-发射极 电压钳制的 0.3 伏。 晶体管 T7 现在处于 导通状态,从而通过 下拉晶体管 T8 的 基极电压而将其关闭。 由于 T8 关闭, 因此其集电极 看起来具有高 阻抗,比较器的 输出电压 被连接到 正电源的 2 千欧上拉 电阻器拉高。 现在,让我们在 +IN 上 保持2.5 伏的基准, 但将 -IN 上的输入 信号更改为 2.65 伏。 我们现在要将 2.65 伏 与 2.5 伏基准进行比较。 晶体管 T4 和 T6 将导通并饱和, 从而使 T6 上的 电压变得很低。 T7 现在关闭,从而 允许 T8 完全导通 并将比较器输出电压 向下驱动至约 0 伏, 即逻辑低电平。 比较器根据 其输出级设计 分为两种 主要的类型。 这两种类型称为漏极 开路或集电极开路和 推挽,也称为 漏极-漏极, 我们的集电极-集电极。 集电极开路和 集电极-集电极 比较器是使用 双极晶体管构建的。 而漏极开路和漏极-漏极 比较器是使用 FET 构建的。 左侧的比较器和 前一张幻灯片中的 LM139 示例具有 集电极开路 输出以及包含 单个 NPN 双极 晶体管的输出级。 当该晶体管导通时, 它会主动地将电流 从集电极灌入到 发射极,并将输出 电压 VO 下拉至非常 接近于接地,即 0 伏。 输出摆动至 接近于接地的 程度取决于 集电极-发射极 饱和电压。 当晶体管关闭时, 其集电极看起来 具有高阻抗, 对输出电压 基本上没有影响。 在这种情况下, 会通过上拉 电阻器从 V+ 拉取较小的电流, VO 升至 VOH, 即我们的逻辑 1。 如果不使用该 上拉电阻器,则 VO 可能会浮动至未知状态。 另一方面,推挽 比较器具有 包含一对 输出晶体管的 输出级。 该晶体管对中的 上部或下部晶体管 会导通,并主动拉取 或灌入电流,以根据 需要将输出驱动至 高电平或低电平。 在右侧的示例中, P 沟道上部 FET 导通,以拉取 电流并将输出 推至高电平。 同时 N 沟道 下部 FET 导通, 以灌入电流并将 输出拉至低电平。 该类型的比较器 不需要上拉电阻器。 比较器的常见期望 功能是生成逻辑“或”, 当其两个 输入中的 任一个打开时, 输出为逻辑低电平。 该功能块通常 可以通过将 两个比较器的 输出连接在 一起来实现。 不过,必须注意使用 正确类型的比较器, 我们以后会 讨论这一点。 让我们首先 考虑左侧的电路, 该电路具有两个输出 连接在一起的推挽器件。 请记住,推挽 比较器会主动 拉取或灌入电流,以将其 输出电压推高或拉低。 您可能已经 看出该电路 配置的问题。 但让我们来分析一下 其运行的不同可能性。 如果两个比较器的 输出都为高电平, 那么每个推挽 输出级中的顶部 晶体管会导通,输出 被驱动为高电平。 类似地,如果两个 输出都为低电平, 那么每个比较器中的 底部晶体管会导通, 输出被驱动为低电平。 当两个比较器试图 将输出驱动为不同的 状态时,问题 就出现了。 在这种情况下, 会发生冲突, 因为每个比较器 都试图拉取或灌入 电流,以强制输出 变为不同的电压。 这会导致出现高电流 情况,从而将输出驱动至 某种不确定的状态, 可能是高电平, 也可能是低电平。 正如您可以 想象的那样, 该情况是不利的, 甚至可能损坏器件。 因此,绝对不应 以这种方式 将推挽比较器 连接在一起。 另一方面,集电极 开路或漏极开路 比较器可以在该 方法下很好地工作。 请记住,集电极开路 或漏极开路比较器的 输出级是使用 单个晶体管 构建的,该晶体管 在导通时会将 输出拉低,在关闭时 看起来具有高阻抗。 现在,无论每个 输出上存在哪种 高电平或低 电平组合, 都会安全地将输出 驱动至已知状态。 如果两个输出都为 低电平,那么两个 输出晶体管都会 导通,将总体输出 向下拉至大约 0 伏。 如果两个输出都为 高电平,那么两个 晶体管都关闭, 看起来具有高阻抗, 从而允许通过上拉 电阻器将输出向上拉至 逻辑高电平。 如果一个输出为高电平, 一个输出为低电平,那么 低电平状态将处于 支配地位,因为与上拉 电阻器可以提供以尝试 将输出驱动为高电平的 电流相比,导通的晶体管能够 灌入的电流要大得多, 从而将输出拉低。 您可以查看右侧的 真值表,以了解 全部四种可能输入 状态下的逻辑行为。 正如您可以看到的, 这等效于逻辑“或” 功能。 该采用比较器的 逻辑“或”实现 通常称为 线或配置。 我们最后将讨论 比较器直流参数, 从而结束该系列的 第一个视频,任何 了解运算放大器的 人都应非常熟悉 这些参数。 该图显示了基本 比较器原理图, 以及众多最常见的 直流参数,其中 包括输入失调 电压或 VOS,表示为 与同相输入 串联的电压源; 输入偏置电流 或 IB;以及输入 偏置电流或 IOS,表示为流入 或流出比较器 输入的电流源; 输入共模 电压范围 或 VCM,在输入 晶体管饱和 或截止之前允许的 输入共模电压范围, 在现代器件上通常 从一个电源轨扩展至 另一个电源轨; 输入差分电压范围 或 VDFF,+IN 和 -IN 上 允许的差分 电压最大值; 电源轨的电压 输出高电平 或 VOH;相对于正 电源的最大逻辑 高电压;电源轨的电压 输出低电平或 VOL, 相对于接地 或负电源的 最小逻辑低电压; 输出短路电流 或 ISC,输出级 晶体管可以 拉取或灌入的 最大输出电流; 静态电流 或 IQ,当输出 电流为 0 时 器件的典型 电流消耗; 电源电压 范围或 VS,指定 操作的允许电源 电压范围。 可以指定 其他参数, 如开环 增益、电压 温漂、共模 抑制和电源 抑制。 但相对于上述 规格而言,它们 对于比较器的重要性要 低一些,因此较少予以考虑。 最关键的 直流规格之一 是输入失调 电压 VOS。 由于比较器的 VOS 会生成 与同相输入 串联的附加 直流电压,因此它对 比较器输出更改 状态的阈值 有重大的影响。 让我们来分析 一下具有三种 不同 VOS 值的同相 比较器电路,从而 更好地了解该影响。 请记住,对于 同相比较器, 如果 VIN 大于 VREF, Vout 将为高电平, 如果 VIN 小于 VREF, Vout 将为低电平。 在该示例中,我们将向 反相输入施加 2.5 伏的 基准电压。 正如您在右侧图的 深蓝色波形中看到的, 输入信号是 缓慢移动的 斜坡,从 2.46 伏转换为 2.54 伏。 失调电压会 增加输入信号, 以生成等于 VIN 加 VOS 的总 有效输入信号。 如果 VOS 等于 0, 那么总输入 电压等于 VIN 加 0, 电路会正常运行。 当 VIN 大于 2.5 伏时, Vout 为高电平。 当 VIN 小于 2.5 伏时, Vout 为低电平, 如红色波形所示。 如果 VOS 等于 正 10 毫伏, 那么总输入 电压等于 VIN 加 10 毫伏。 现在,输出将 在更低的 VIN 电压下进行转换, 因为通过 VOS 增加的 电压使总输入电压 能够更早地达到 2.5 伏。 您可以在橙色 波形中看到, 当 VIN 大于 2.49 伏时, Vout 为高电平, 当 VIN 小于 2.49 伏时, Vout 为低电平。 最后,如果 VOS 等于负 10 毫伏, 那么总输入 电压等于 VIN 减 10 毫伏。 现在,由于负 VOS 减去了一部分电压, 因此输出将在更高的 VIN 电压下进行转换。 您可以在淡蓝色 波形中看到, 当 VIN 大于 2.51 伏时, Vout 为高电平, 当 VIN 小于 2.51 伏时, Vout 为低电平。 请记住,不仅是 阈值电压会因 VOS 而变化,输出 波形的时序也会 受到影响。 例如,当 VOS 等于正 10 毫伏时, 输出波形会持续大约 600 毫秒保持高电平。 当 VOS 等于 负 10 毫伏时, 输出波形保持高电平的 时长会小于 400 毫秒。 该时序行为可能会在 特定的设计中引发问题, 但本示例中极缓慢 移动的输入信号会导致 最糟糕的情形。 为了帮助防止产生 这些类型的误差, 可以增大输入 信号的频率。 许多习惯于使用 现代运算放大器 进行设计的 工程师可能会 习惯于微伏级至几毫伏 范围内的失调电压。 比较器通常 具有稍高的 失调电压, 其范围为 大约正负 2 毫伏至 正负 15 毫伏。 在某些情况下, 比较器的失调电压 可能会完全改变 其输出信号。 考虑左侧 显示的电路, 一个反相比较器, 其输入信号由 数模转换器 或 DAC 进行提供。 数模转换器 会生根据数字 代码成模拟 电压或电流。 因此其输出通常看起来 随时间的推移在不同的 直流电压之间转换。 让我们来分析 一下当我们提供 1.25 伏基准电压 并且失调电压 从正 5 毫伏变为 0 毫伏再变为 负 5 毫伏时 该电路的输出。 在该电路中,将 VOS 添加到 VREF, 因此总有效基准 电压变为 VREF 加 VOS。 当 VOS 等于 正 5 毫伏时, 总基准电压等于 1.25 伏加 5 毫伏, 或 1.255 伏。 由于基准电压 增加,因此比较器 输出仅在输入 波形中两次变低, 如右上角的 蓝色图中 所示。 当 VOS 等于 0 伏时, 总基准电压等于 1.25 伏。 右侧的红色图中 显示了比较器输出。 当 VOS 等于 负 5 毫伏时, 总基准电压 现在等于 1.25 伏减 5 毫伏, 或 1.245 伏。 比较器输出再次 改变,右下角的 绿色图对此 进行了显示。 该示例的小输入 信号范围显示了 由于 VOS 而导致的 误差最糟糕情形。 为了防止产生 这些类型的误差, 应设法增大相对于 失调电压的输入 信号范围。 不过,当输入信号 在基准电压附近 波动时,仍然 可能会遇到 该类型的行为。 请务必观看该系列中的 后续视频,以学习 可帮助防止 产生这些类型的 误差的简单 但非常有用的技术。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频 356

大家好,欢迎观看 TI 高精度实验室 视频系列,其中 介绍比较器应用。 比较器的作用是 比较两个模拟输入 信号并根据该比较 生成数字或逻辑 电平输出。 在本视频中,我们 将讨论模拟比较器的 基本功能及其 部分主要规格, 其中包括输入 失调电压或 VOS。 让我们首先 介绍比较器的 基本功能。 与标准运算放大器 类似,比较器具有 两个输入、一个输出 以及两个电源引脚。 从原理图的角度而言, 它与运算放大器类似, 但其预期功能 大不相同。 比较器之所以得此 名称,是因为它比较 施加到其输入端的 电压并根据输入 电平来设置 其输出电压。 一个输入被视为 主输入信号 或 VIN。 另一个 输入被 视为基准 信号 VREF。 这些输入可能具有 直流和交流分量。 可以将输出电压 Vout 设置为两种电平之一 -- 高电平或逻辑 1, 或者低电平或逻辑 0。 输出高电平 VH 接近于 V+,即正 电源电压。 输出低电平 VL 接近于 0 伏或接地,或双电源 配置中的负电源。 该幻灯片中 显示的比较器 针对同相操作 进行了配置。 在该情况下, 输入信号 VIN 连接到 同相输入 +IN,基准 信号 VREF 连接到反相 输入 -IN。 如果 VIN 大于 VREF, 则比较器输出为高电平。 如果 VIN 小于 VREF, 则比较器输出为低电平。 比较器还可以 用于反相配置。 在该情况下, 输入信号 VIN 连接到反相 输入 -IN, 基准 信号 VREF 连接到 同相输入 +IN。 由于我们 定义输入 信号方式的改变, 可以将输出行为 视为反相。 现在,如果 VIN 大于 VREF, 那么比较器输出为低电平。 如果 VIN 小于 VREF, 则输出为高电平。 让我们来看看 双极比较器 LM139 的简化 内部设计。 此处的目标不是 讲授晶体管理论 或比较器设计的 详细工作原理, 而是为您提供有关比较器 如何工作的一般概念。 蓝色框中 所示的输入级 包含一个 PNP 差分放大器。 该差分级的 每侧都使用 达林顿 PNP 晶体管。 使用达林顿 连接晶体管 可增大输入阻抗, 降低输入偏置电流, 允许共模 输入电压 向下扩展至 0 伏。 该级中每个晶体管的 发射极电路中都具有 电流源,用于设置 发射极电流。 差分输入级中 晶体管的集电极 连接到用作 动态负载的 NPN 晶体管,如 青绿色部分所示。 最后,动态负载级的 输出耦合到 NPN 驱动器和集电极 开路输出级,如紫色 部分所示。 在比较器的 正常运行期间, 差分输入信号 +IN 减去 -IN 由输入差分 放大器的电压 增益进行放大。 该差分级的 输出在 T6 上形成, 并用于打开或 关闭输出级, 具体取决于输入极性。 为了更好地理解 内部功能,现在 让我们向该比较器 施加一些变化的输入 信号,并查看内部 电压在各个级 是如何变化的。 在该示例中, 我们将使用 采用反相配置的 比较器,VREF 连接到 +IN,VIN 连接到 -IN。 让我们首先向 +IN 施加 2.5 伏的基准 电压,向 -IN 施加 2.4 伏的输入信号。 那么我们要将 2.4 伏 与 2.5 伏基准进行比较。 这些电压以红色 显示在各个节点上。 底部提供了输入 为 2.4 伏的情形。 查看 -IN,可以 发现连接到 差分输入对的 该侧的晶体管 连接到动态 负载晶体管 T6。 T6 集电极处的 电压等于由 晶体管 T7 的 基极-发射极 电压钳制的 0.3 伏。 晶体管 T7 现在处于 导通状态,从而通过 下拉晶体管 T8 的 基极电压而将其关闭。 由于 T8 关闭, 因此其集电极 看起来具有高 阻抗,比较器的 输出电压 被连接到 正电源的 2 千欧上拉 电阻器拉高。 现在,让我们在 +IN 上 保持2.5 伏的基准, 但将 -IN 上的输入 信号更改为 2.65 伏。 我们现在要将 2.65 伏 与 2.5 伏基准进行比较。 晶体管 T4 和 T6 将导通并饱和, 从而使 T6 上的 电压变得很低。 T7 现在关闭,从而 允许 T8 完全导通 并将比较器输出电压 向下驱动至约 0 伏, 即逻辑低电平。 比较器根据 其输出级设计 分为两种 主要的类型。 这两种类型称为漏极 开路或集电极开路和 推挽,也称为 漏极-漏极, 我们的集电极-集电极。 集电极开路和 集电极-集电极 比较器是使用 双极晶体管构建的。 而漏极开路和漏极-漏极 比较器是使用 FET 构建的。 左侧的比较器和 前一张幻灯片中的 LM139 示例具有 集电极开路 输出以及包含 单个 NPN 双极 晶体管的输出级。 当该晶体管导通时, 它会主动地将电流 从集电极灌入到 发射极,并将输出 电压 VO 下拉至非常 接近于接地,即 0 伏。 输出摆动至 接近于接地的 程度取决于 集电极-发射极 饱和电压。 当晶体管关闭时, 其集电极看起来 具有高阻抗, 对输出电压 基本上没有影响。 在这种情况下, 会通过上拉 电阻器从 V+ 拉取较小的电流, VO 升至 VOH, 即我们的逻辑 1。 如果不使用该 上拉电阻器,则 VO 可能会浮动至未知状态。 另一方面,推挽 比较器具有 包含一对 输出晶体管的 输出级。 该晶体管对中的 上部或下部晶体管 会导通,并主动拉取 或灌入电流,以根据 需要将输出驱动至 高电平或低电平。 在右侧的示例中, P 沟道上部 FET 导通,以拉取 电流并将输出 推至高电平。 同时 N 沟道 下部 FET 导通, 以灌入电流并将 输出拉至低电平。 该类型的比较器 不需要上拉电阻器。 比较器的常见期望 功能是生成逻辑“或”, 当其两个 输入中的 任一个打开时, 输出为逻辑低电平。 该功能块通常 可以通过将 两个比较器的 输出连接在 一起来实现。 不过,必须注意使用 正确类型的比较器, 我们以后会 讨论这一点。 让我们首先 考虑左侧的电路, 该电路具有两个输出 连接在一起的推挽器件。 请记住,推挽 比较器会主动 拉取或灌入电流,以将其 输出电压推高或拉低。 您可能已经 看出该电路 配置的问题。 但让我们来分析一下 其运行的不同可能性。 如果两个比较器的 输出都为高电平, 那么每个推挽 输出级中的顶部 晶体管会导通,输出 被驱动为高电平。 类似地,如果两个 输出都为低电平, 那么每个比较器中的 底部晶体管会导通, 输出被驱动为低电平。 当两个比较器试图 将输出驱动为不同的 状态时,问题 就出现了。 在这种情况下, 会发生冲突, 因为每个比较器 都试图拉取或灌入 电流,以强制输出 变为不同的电压。 这会导致出现高电流 情况,从而将输出驱动至 某种不确定的状态, 可能是高电平, 也可能是低电平。 正如您可以 想象的那样, 该情况是不利的, 甚至可能损坏器件。 因此,绝对不应 以这种方式 将推挽比较器 连接在一起。 另一方面,集电极 开路或漏极开路 比较器可以在该 方法下很好地工作。 请记住,集电极开路 或漏极开路比较器的 输出级是使用 单个晶体管 构建的,该晶体管 在导通时会将 输出拉低,在关闭时 看起来具有高阻抗。 现在,无论每个 输出上存在哪种 高电平或低 电平组合, 都会安全地将输出 驱动至已知状态。 如果两个输出都为 低电平,那么两个 输出晶体管都会 导通,将总体输出 向下拉至大约 0 伏。 如果两个输出都为 高电平,那么两个 晶体管都关闭, 看起来具有高阻抗, 从而允许通过上拉 电阻器将输出向上拉至 逻辑高电平。 如果一个输出为高电平, 一个输出为低电平,那么 低电平状态将处于 支配地位,因为与上拉 电阻器可以提供以尝试 将输出驱动为高电平的 电流相比,导通的晶体管能够 灌入的电流要大得多, 从而将输出拉低。 您可以查看右侧的 真值表,以了解 全部四种可能输入 状态下的逻辑行为。 正如您可以看到的, 这等效于逻辑“或” 功能。 该采用比较器的 逻辑“或”实现 通常称为 线或配置。 我们最后将讨论 比较器直流参数, 从而结束该系列的 第一个视频,任何 了解运算放大器的 人都应非常熟悉 这些参数。 该图显示了基本 比较器原理图, 以及众多最常见的 直流参数,其中 包括输入失调 电压或 VOS,表示为 与同相输入 串联的电压源; 输入偏置电流 或 IB;以及输入 偏置电流或 IOS,表示为流入 或流出比较器 输入的电流源; 输入共模 电压范围 或 VCM,在输入 晶体管饱和 或截止之前允许的 输入共模电压范围, 在现代器件上通常 从一个电源轨扩展至 另一个电源轨; 输入差分电压范围 或 VDFF,+IN 和 -IN 上 允许的差分 电压最大值; 电源轨的电压 输出高电平 或 VOH;相对于正 电源的最大逻辑 高电压;电源轨的电压 输出低电平或 VOL, 相对于接地 或负电源的 最小逻辑低电压; 输出短路电流 或 ISC,输出级 晶体管可以 拉取或灌入的 最大输出电流; 静态电流 或 IQ,当输出 电流为 0 时 器件的典型 电流消耗; 电源电压 范围或 VS,指定 操作的允许电源 电压范围。 可以指定 其他参数, 如开环 增益、电压 温漂、共模 抑制和电源 抑制。 但相对于上述 规格而言,它们 对于比较器的重要性要 低一些,因此较少予以考虑。 最关键的 直流规格之一 是输入失调 电压 VOS。 由于比较器的 VOS 会生成 与同相输入 串联的附加 直流电压,因此它对 比较器输出更改 状态的阈值 有重大的影响。 让我们来分析 一下具有三种 不同 VOS 值的同相 比较器电路,从而 更好地了解该影响。 请记住,对于 同相比较器, 如果 VIN 大于 VREF, Vout 将为高电平, 如果 VIN 小于 VREF, Vout 将为低电平。 在该示例中,我们将向 反相输入施加 2.5 伏的 基准电压。 正如您在右侧图的 深蓝色波形中看到的, 输入信号是 缓慢移动的 斜坡,从 2.46 伏转换为 2.54 伏。 失调电压会 增加输入信号, 以生成等于 VIN 加 VOS 的总 有效输入信号。 如果 VOS 等于 0, 那么总输入 电压等于 VIN 加 0, 电路会正常运行。 当 VIN 大于 2.5 伏时, Vout 为高电平。 当 VIN 小于 2.5 伏时, Vout 为低电平, 如红色波形所示。 如果 VOS 等于 正 10 毫伏, 那么总输入 电压等于 VIN 加 10 毫伏。 现在,输出将 在更低的 VIN 电压下进行转换, 因为通过 VOS 增加的 电压使总输入电压 能够更早地达到 2.5 伏。 您可以在橙色 波形中看到, 当 VIN 大于 2.49 伏时, Vout 为高电平, 当 VIN 小于 2.49 伏时, Vout 为低电平。 最后,如果 VOS 等于负 10 毫伏, 那么总输入 电压等于 VIN 减 10 毫伏。 现在,由于负 VOS 减去了一部分电压, 因此输出将在更高的 VIN 电压下进行转换。 您可以在淡蓝色 波形中看到, 当 VIN 大于 2.51 伏时, Vout 为高电平, 当 VIN 小于 2.51 伏时, Vout 为低电平。 请记住,不仅是 阈值电压会因 VOS 而变化,输出 波形的时序也会 受到影响。 例如,当 VOS 等于正 10 毫伏时, 输出波形会持续大约 600 毫秒保持高电平。 当 VOS 等于 负 10 毫伏时, 输出波形保持高电平的 时长会小于 400 毫秒。 该时序行为可能会在 特定的设计中引发问题, 但本示例中极缓慢 移动的输入信号会导致 最糟糕的情形。 为了帮助防止产生 这些类型的误差, 可以增大输入 信号的频率。 许多习惯于使用 现代运算放大器 进行设计的 工程师可能会 习惯于微伏级至几毫伏 范围内的失调电压。 比较器通常 具有稍高的 失调电压, 其范围为 大约正负 2 毫伏至 正负 15 毫伏。 在某些情况下, 比较器的失调电压 可能会完全改变 其输出信号。 考虑左侧 显示的电路, 一个反相比较器, 其输入信号由 数模转换器 或 DAC 进行提供。 数模转换器 会生根据数字 代码成模拟 电压或电流。 因此其输出通常看起来 随时间的推移在不同的 直流电压之间转换。 让我们来分析 一下当我们提供 1.25 伏基准电压 并且失调电压 从正 5 毫伏变为 0 毫伏再变为 负 5 毫伏时 该电路的输出。 在该电路中,将 VOS 添加到 VREF, 因此总有效基准 电压变为 VREF 加 VOS。 当 VOS 等于 正 5 毫伏时, 总基准电压等于 1.25 伏加 5 毫伏, 或 1.255 伏。 由于基准电压 增加,因此比较器 输出仅在输入 波形中两次变低, 如右上角的 蓝色图中 所示。 当 VOS 等于 0 伏时, 总基准电压等于 1.25 伏。 右侧的红色图中 显示了比较器输出。 当 VOS 等于 负 5 毫伏时, 总基准电压 现在等于 1.25 伏减 5 毫伏, 或 1.245 伏。 比较器输出再次 改变,右下角的 绿色图对此 进行了显示。 该示例的小输入 信号范围显示了 由于 VOS 而导致的 误差最糟糕情形。 为了防止产生 这些类型的误差, 应设法增大相对于 失调电压的输入 信号范围。 不过,当输入信号 在基准电压附近 波动时,仍然 可能会遇到 该类型的行为。 请务必观看该系列中的 后续视频,以学习 可帮助防止 产生这些类型的 误差的简单 但非常有用的技术。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频 356

大家好,欢迎观看 TI 高精度实验室

视频系列,其中 介绍比较器应用。

比较器的作用是 比较两个模拟输入

信号并根据该比较 生成数字或逻辑

电平输出。

在本视频中,我们 将讨论模拟比较器的

基本功能及其 部分主要规格,

其中包括输入 失调电压或 VOS。

让我们首先 介绍比较器的

基本功能。

与标准运算放大器 类似,比较器具有

两个输入、一个输出 以及两个电源引脚。

从原理图的角度而言, 它与运算放大器类似,

但其预期功能 大不相同。

比较器之所以得此 名称,是因为它比较

施加到其输入端的 电压并根据输入

电平来设置 其输出电压。

一个输入被视为 主输入信号

或 VIN。

另一个 输入被

视为基准 信号 VREF。

这些输入可能具有 直流和交流分量。

可以将输出电压 Vout 设置为两种电平之一 --

高电平或逻辑 1, 或者低电平或逻辑 0。

输出高电平 VH 接近于

V+,即正 电源电压。

输出低电平 VL 接近于 0

伏或接地,或双电源 配置中的负电源。

该幻灯片中 显示的比较器

针对同相操作 进行了配置。

在该情况下, 输入信号 VIN

连接到 同相输入

+IN,基准 信号 VREF

连接到反相 输入 -IN。

如果 VIN 大于 VREF, 则比较器输出为高电平。

如果 VIN 小于 VREF, 则比较器输出为低电平。

比较器还可以 用于反相配置。

在该情况下, 输入信号 VIN

连接到反相 输入 -IN,

基准 信号 VREF

连接到 同相输入 +IN。

由于我们 定义输入

信号方式的改变, 可以将输出行为

视为反相。

现在,如果 VIN 大于 VREF,

那么比较器输出为低电平。

如果 VIN 小于 VREF, 则输出为高电平。

让我们来看看 双极比较器

LM139 的简化 内部设计。

此处的目标不是 讲授晶体管理论

或比较器设计的 详细工作原理,

而是为您提供有关比较器 如何工作的一般概念。

蓝色框中 所示的输入级

包含一个 PNP 差分放大器。

该差分级的 每侧都使用

达林顿 PNP 晶体管。

使用达林顿 连接晶体管

可增大输入阻抗, 降低输入偏置电流,

允许共模 输入电压

向下扩展至 0 伏。

该级中每个晶体管的 发射极电路中都具有

电流源,用于设置 发射极电流。

差分输入级中 晶体管的集电极

连接到用作 动态负载的

NPN 晶体管,如 青绿色部分所示。

最后,动态负载级的 输出耦合到 NPN

驱动器和集电极 开路输出级,如紫色

部分所示。

在比较器的 正常运行期间,

差分输入信号 +IN 减去 -IN

由输入差分 放大器的电压

增益进行放大。

该差分级的 输出在 T6 上形成,

并用于打开或 关闭输出级,

具体取决于输入极性。

为了更好地理解 内部功能,现在

让我们向该比较器 施加一些变化的输入

信号,并查看内部 电压在各个级

是如何变化的。

在该示例中, 我们将使用

采用反相配置的 比较器,VREF 连接到

+IN,VIN 连接到 -IN。

让我们首先向 +IN 施加 2.5 伏的基准

电压,向 -IN 施加 2.4 伏的输入信号。

那么我们要将 2.4 伏 与 2.5 伏基准进行比较。

这些电压以红色 显示在各个节点上。

底部提供了输入 为 2.4 伏的情形。

查看 -IN,可以 发现连接到

差分输入对的 该侧的晶体管

连接到动态 负载晶体管 T6。

T6 集电极处的 电压等于由

晶体管 T7 的 基极-发射极

电压钳制的 0.3 伏。

晶体管 T7 现在处于 导通状态,从而通过

下拉晶体管 T8 的 基极电压而将其关闭。

由于 T8 关闭, 因此其集电极

看起来具有高 阻抗,比较器的

输出电压 被连接到

正电源的 2 千欧上拉

电阻器拉高。

现在,让我们在 +IN 上 保持2.5 伏的基准,

但将 -IN 上的输入 信号更改为 2.65 伏。

我们现在要将 2.65 伏 与 2.5 伏基准进行比较。

晶体管 T4 和 T6 将导通并饱和,

从而使 T6 上的 电压变得很低。

T7 现在关闭,从而 允许 T8 完全导通

并将比较器输出电压 向下驱动至约 0 伏,

即逻辑低电平。

比较器根据 其输出级设计

分为两种 主要的类型。

这两种类型称为漏极 开路或集电极开路和

推挽,也称为 漏极-漏极,

我们的集电极-集电极。

集电极开路和 集电极-集电极

比较器是使用 双极晶体管构建的。

而漏极开路和漏极-漏极 比较器是使用 FET

构建的。

左侧的比较器和 前一张幻灯片中的

LM139 示例具有 集电极开路

输出以及包含 单个 NPN 双极

晶体管的输出级。

当该晶体管导通时, 它会主动地将电流

从集电极灌入到 发射极,并将输出

电压 VO 下拉至非常 接近于接地,即 0 伏。

输出摆动至 接近于接地的

程度取决于 集电极-发射极

饱和电压。

当晶体管关闭时, 其集电极看起来

具有高阻抗, 对输出电压

基本上没有影响。

在这种情况下, 会通过上拉

电阻器从 V+ 拉取较小的电流,

VO 升至 VOH, 即我们的逻辑 1。

如果不使用该 上拉电阻器,则 VO

可能会浮动至未知状态。

另一方面,推挽 比较器具有

包含一对 输出晶体管的

输出级。

该晶体管对中的 上部或下部晶体管

会导通,并主动拉取 或灌入电流,以根据

需要将输出驱动至 高电平或低电平。

在右侧的示例中, P 沟道上部 FET

导通,以拉取 电流并将输出

推至高电平。

同时 N 沟道 下部 FET 导通,

以灌入电流并将 输出拉至低电平。

该类型的比较器 不需要上拉电阻器。

比较器的常见期望 功能是生成逻辑“或”,

当其两个 输入中的

任一个打开时, 输出为逻辑低电平。

该功能块通常 可以通过将

两个比较器的 输出连接在

一起来实现。

不过,必须注意使用 正确类型的比较器,

我们以后会 讨论这一点。

让我们首先 考虑左侧的电路,

该电路具有两个输出 连接在一起的推挽器件。

请记住,推挽 比较器会主动

拉取或灌入电流,以将其 输出电压推高或拉低。

您可能已经 看出该电路

配置的问题。

但让我们来分析一下 其运行的不同可能性。

如果两个比较器的 输出都为高电平,

那么每个推挽 输出级中的顶部

晶体管会导通,输出 被驱动为高电平。

类似地,如果两个 输出都为低电平,

那么每个比较器中的 底部晶体管会导通,

输出被驱动为低电平。

当两个比较器试图 将输出驱动为不同的

状态时,问题 就出现了。

在这种情况下, 会发生冲突,

因为每个比较器 都试图拉取或灌入

电流,以强制输出 变为不同的电压。

这会导致出现高电流 情况,从而将输出驱动至

某种不确定的状态, 可能是高电平,

也可能是低电平。

正如您可以 想象的那样,

该情况是不利的, 甚至可能损坏器件。

因此,绝对不应 以这种方式

将推挽比较器 连接在一起。

另一方面,集电极 开路或漏极开路

比较器可以在该 方法下很好地工作。

请记住,集电极开路 或漏极开路比较器的

输出级是使用 单个晶体管

构建的,该晶体管 在导通时会将

输出拉低,在关闭时 看起来具有高阻抗。

现在,无论每个 输出上存在哪种

高电平或低 电平组合,

都会安全地将输出 驱动至已知状态。

如果两个输出都为 低电平,那么两个

输出晶体管都会 导通,将总体输出

向下拉至大约 0 伏。

如果两个输出都为 高电平,那么两个

晶体管都关闭, 看起来具有高阻抗,

从而允许通过上拉 电阻器将输出向上拉至

逻辑高电平。

如果一个输出为高电平, 一个输出为低电平,那么

低电平状态将处于 支配地位,因为与上拉

电阻器可以提供以尝试 将输出驱动为高电平的

电流相比,导通的晶体管能够 灌入的电流要大得多,

从而将输出拉低。

您可以查看右侧的 真值表,以了解

全部四种可能输入 状态下的逻辑行为。

正如您可以看到的, 这等效于逻辑“或”

功能。

该采用比较器的 逻辑“或”实现

通常称为 线或配置。

我们最后将讨论 比较器直流参数,

从而结束该系列的 第一个视频,任何

了解运算放大器的 人都应非常熟悉

这些参数。

该图显示了基本 比较器原理图,

以及众多最常见的 直流参数,其中

包括输入失调 电压或 VOS,表示为

与同相输入 串联的电压源;

输入偏置电流 或 IB;以及输入

偏置电流或 IOS,表示为流入

或流出比较器 输入的电流源;

输入共模 电压范围

或 VCM,在输入 晶体管饱和

或截止之前允许的 输入共模电压范围,

在现代器件上通常 从一个电源轨扩展至

另一个电源轨; 输入差分电压范围

或 VDFF,+IN 和 -IN 上

允许的差分 电压最大值;

电源轨的电压 输出高电平

或 VOH;相对于正 电源的最大逻辑

高电压;电源轨的电压 输出低电平或 VOL,

相对于接地 或负电源的

最小逻辑低电压; 输出短路电流

或 ISC,输出级 晶体管可以

拉取或灌入的 最大输出电流;

静态电流 或 IQ,当输出

电流为 0 时 器件的典型

电流消耗; 电源电压

范围或 VS,指定 操作的允许电源

电压范围。

可以指定 其他参数,

如开环 增益、电压

温漂、共模 抑制和电源

抑制。

但相对于上述 规格而言,它们

对于比较器的重要性要 低一些,因此较少予以考虑。

最关键的 直流规格之一

是输入失调 电压 VOS。

由于比较器的 VOS 会生成

与同相输入 串联的附加

直流电压,因此它对 比较器输出更改

状态的阈值 有重大的影响。

让我们来分析 一下具有三种

不同 VOS 值的同相 比较器电路,从而

更好地了解该影响。

请记住,对于 同相比较器,

如果 VIN 大于 VREF, Vout 将为高电平,

如果 VIN 小于 VREF, Vout 将为低电平。

在该示例中,我们将向 反相输入施加 2.5 伏的

基准电压。

正如您在右侧图的 深蓝色波形中看到的,

输入信号是 缓慢移动的

斜坡,从 2.46 伏转换为

2.54 伏。

失调电压会 增加输入信号,

以生成等于 VIN 加 VOS 的总

有效输入信号。

如果 VOS 等于 0, 那么总输入

电压等于 VIN 加 0, 电路会正常运行。

当 VIN 大于 2.5 伏时, Vout 为高电平。

当 VIN 小于 2.5 伏时,

Vout 为低电平, 如红色波形所示。

如果 VOS 等于 正 10 毫伏,

那么总输入 电压等于 VIN

加 10 毫伏。

现在,输出将 在更低的 VIN

电压下进行转换, 因为通过 VOS 增加的

电压使总输入电压 能够更早地达到 2.5 伏。

您可以在橙色 波形中看到,

当 VIN 大于 2.49 伏时, Vout 为高电平,

当 VIN 小于 2.49 伏时, Vout 为低电平。

最后,如果 VOS 等于负 10 毫伏,

那么总输入 电压等于 VIN

减 10 毫伏。

现在,由于负 VOS 减去了一部分电压,

因此输出将在更高的 VIN 电压下进行转换。

您可以在淡蓝色 波形中看到,

当 VIN 大于 2.51 伏时, Vout 为高电平,

当 VIN 小于 2.51 伏时, Vout 为低电平。

请记住,不仅是 阈值电压会因

VOS 而变化,输出 波形的时序也会

受到影响。

例如,当 VOS 等于正 10 毫伏时,

输出波形会持续大约 600 毫秒保持高电平。

当 VOS 等于 负 10 毫伏时,

输出波形保持高电平的 时长会小于 400 毫秒。

该时序行为可能会在 特定的设计中引发问题,

但本示例中极缓慢 移动的输入信号会导致

最糟糕的情形。

为了帮助防止产生 这些类型的误差,

可以增大输入 信号的频率。

许多习惯于使用 现代运算放大器

进行设计的 工程师可能会

习惯于微伏级至几毫伏 范围内的失调电压。

比较器通常 具有稍高的

失调电压, 其范围为

大约正负 2 毫伏至

正负 15 毫伏。

在某些情况下, 比较器的失调电压

可能会完全改变 其输出信号。

考虑左侧 显示的电路,

一个反相比较器, 其输入信号由

数模转换器 或 DAC 进行提供。

数模转换器 会生根据数字

代码成模拟 电压或电流。

因此其输出通常看起来 随时间的推移在不同的

直流电压之间转换。

让我们来分析 一下当我们提供

1.25 伏基准电压 并且失调电压

从正 5 毫伏变为 0 毫伏再变为

负 5 毫伏时 该电路的输出。

在该电路中,将 VOS 添加到 VREF,

因此总有效基准 电压变为 VREF 加 VOS。

当 VOS 等于 正 5 毫伏时,

总基准电压等于 1.25 伏加 5 毫伏,

或 1.255 伏。

由于基准电压 增加,因此比较器

输出仅在输入 波形中两次变低,

如右上角的 蓝色图中

所示。

当 VOS 等于 0 伏时, 总基准电压等于

1.25 伏。

右侧的红色图中 显示了比较器输出。

当 VOS 等于 负 5 毫伏时,

总基准电压 现在等于 1.25

伏减 5 毫伏, 或 1.245 伏。

比较器输出再次 改变,右下角的

绿色图对此 进行了显示。

该示例的小输入 信号范围显示了

由于 VOS 而导致的 误差最糟糕情形。

为了防止产生 这些类型的误差,

应设法增大相对于 失调电压的输入

信号范围。

不过,当输入信号 在基准电压附近

波动时,仍然 可能会遇到

该类型的行为。

请务必观看该系列中的 后续视频,以学习

可帮助防止 产生这些类型的

误差的简单 但非常有用的技术。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频 356

大家好,欢迎观看 TI 高精度实验室 视频系列,其中 介绍比较器应用。 比较器的作用是 比较两个模拟输入 信号并根据该比较 生成数字或逻辑 电平输出。 在本视频中,我们 将讨论模拟比较器的 基本功能及其 部分主要规格, 其中包括输入 失调电压或 VOS。 让我们首先 介绍比较器的 基本功能。 与标准运算放大器 类似,比较器具有 两个输入、一个输出 以及两个电源引脚。 从原理图的角度而言, 它与运算放大器类似, 但其预期功能 大不相同。 比较器之所以得此 名称,是因为它比较 施加到其输入端的 电压并根据输入 电平来设置 其输出电压。 一个输入被视为 主输入信号 或 VIN。 另一个 输入被 视为基准 信号 VREF。 这些输入可能具有 直流和交流分量。 可以将输出电压 Vout 设置为两种电平之一 -- 高电平或逻辑 1, 或者低电平或逻辑 0。 输出高电平 VH 接近于 V+,即正 电源电压。 输出低电平 VL 接近于 0 伏或接地,或双电源 配置中的负电源。 该幻灯片中 显示的比较器 针对同相操作 进行了配置。 在该情况下, 输入信号 VIN 连接到 同相输入 +IN,基准 信号 VREF 连接到反相 输入 -IN。 如果 VIN 大于 VREF, 则比较器输出为高电平。 如果 VIN 小于 VREF, 则比较器输出为低电平。 比较器还可以 用于反相配置。 在该情况下, 输入信号 VIN 连接到反相 输入 -IN, 基准 信号 VREF 连接到 同相输入 +IN。 由于我们 定义输入 信号方式的改变, 可以将输出行为 视为反相。 现在,如果 VIN 大于 VREF, 那么比较器输出为低电平。 如果 VIN 小于 VREF, 则输出为高电平。 让我们来看看 双极比较器 LM139 的简化 内部设计。 此处的目标不是 讲授晶体管理论 或比较器设计的 详细工作原理, 而是为您提供有关比较器 如何工作的一般概念。 蓝色框中 所示的输入级 包含一个 PNP 差分放大器。 该差分级的 每侧都使用 达林顿 PNP 晶体管。 使用达林顿 连接晶体管 可增大输入阻抗, 降低输入偏置电流, 允许共模 输入电压 向下扩展至 0 伏。 该级中每个晶体管的 发射极电路中都具有 电流源,用于设置 发射极电流。 差分输入级中 晶体管的集电极 连接到用作 动态负载的 NPN 晶体管,如 青绿色部分所示。 最后,动态负载级的 输出耦合到 NPN 驱动器和集电极 开路输出级,如紫色 部分所示。 在比较器的 正常运行期间, 差分输入信号 +IN 减去 -IN 由输入差分 放大器的电压 增益进行放大。 该差分级的 输出在 T6 上形成, 并用于打开或 关闭输出级, 具体取决于输入极性。 为了更好地理解 内部功能,现在 让我们向该比较器 施加一些变化的输入 信号,并查看内部 电压在各个级 是如何变化的。 在该示例中, 我们将使用 采用反相配置的 比较器,VREF 连接到 +IN,VIN 连接到 -IN。 让我们首先向 +IN 施加 2.5 伏的基准 电压,向 -IN 施加 2.4 伏的输入信号。 那么我们要将 2.4 伏 与 2.5 伏基准进行比较。 这些电压以红色 显示在各个节点上。 底部提供了输入 为 2.4 伏的情形。 查看 -IN,可以 发现连接到 差分输入对的 该侧的晶体管 连接到动态 负载晶体管 T6。 T6 集电极处的 电压等于由 晶体管 T7 的 基极-发射极 电压钳制的 0.3 伏。 晶体管 T7 现在处于 导通状态,从而通过 下拉晶体管 T8 的 基极电压而将其关闭。 由于 T8 关闭, 因此其集电极 看起来具有高 阻抗,比较器的 输出电压 被连接到 正电源的 2 千欧上拉 电阻器拉高。 现在,让我们在 +IN 上 保持2.5 伏的基准, 但将 -IN 上的输入 信号更改为 2.65 伏。 我们现在要将 2.65 伏 与 2.5 伏基准进行比较。 晶体管 T4 和 T6 将导通并饱和, 从而使 T6 上的 电压变得很低。 T7 现在关闭,从而 允许 T8 完全导通 并将比较器输出电压 向下驱动至约 0 伏, 即逻辑低电平。 比较器根据 其输出级设计 分为两种 主要的类型。 这两种类型称为漏极 开路或集电极开路和 推挽,也称为 漏极-漏极, 我们的集电极-集电极。 集电极开路和 集电极-集电极 比较器是使用 双极晶体管构建的。 而漏极开路和漏极-漏极 比较器是使用 FET 构建的。 左侧的比较器和 前一张幻灯片中的 LM139 示例具有 集电极开路 输出以及包含 单个 NPN 双极 晶体管的输出级。 当该晶体管导通时, 它会主动地将电流 从集电极灌入到 发射极,并将输出 电压 VO 下拉至非常 接近于接地,即 0 伏。 输出摆动至 接近于接地的 程度取决于 集电极-发射极 饱和电压。 当晶体管关闭时, 其集电极看起来 具有高阻抗, 对输出电压 基本上没有影响。 在这种情况下, 会通过上拉 电阻器从 V+ 拉取较小的电流, VO 升至 VOH, 即我们的逻辑 1。 如果不使用该 上拉电阻器,则 VO 可能会浮动至未知状态。 另一方面,推挽 比较器具有 包含一对 输出晶体管的 输出级。 该晶体管对中的 上部或下部晶体管 会导通,并主动拉取 或灌入电流,以根据 需要将输出驱动至 高电平或低电平。 在右侧的示例中, P 沟道上部 FET 导通,以拉取 电流并将输出 推至高电平。 同时 N 沟道 下部 FET 导通, 以灌入电流并将 输出拉至低电平。 该类型的比较器 不需要上拉电阻器。 比较器的常见期望 功能是生成逻辑“或”, 当其两个 输入中的 任一个打开时, 输出为逻辑低电平。 该功能块通常 可以通过将 两个比较器的 输出连接在 一起来实现。 不过,必须注意使用 正确类型的比较器, 我们以后会 讨论这一点。 让我们首先 考虑左侧的电路, 该电路具有两个输出 连接在一起的推挽器件。 请记住,推挽 比较器会主动 拉取或灌入电流,以将其 输出电压推高或拉低。 您可能已经 看出该电路 配置的问题。 但让我们来分析一下 其运行的不同可能性。 如果两个比较器的 输出都为高电平, 那么每个推挽 输出级中的顶部 晶体管会导通,输出 被驱动为高电平。 类似地,如果两个 输出都为低电平, 那么每个比较器中的 底部晶体管会导通, 输出被驱动为低电平。 当两个比较器试图 将输出驱动为不同的 状态时,问题 就出现了。 在这种情况下, 会发生冲突, 因为每个比较器 都试图拉取或灌入 电流,以强制输出 变为不同的电压。 这会导致出现高电流 情况,从而将输出驱动至 某种不确定的状态, 可能是高电平, 也可能是低电平。 正如您可以 想象的那样, 该情况是不利的, 甚至可能损坏器件。 因此,绝对不应 以这种方式 将推挽比较器 连接在一起。 另一方面,集电极 开路或漏极开路 比较器可以在该 方法下很好地工作。 请记住,集电极开路 或漏极开路比较器的 输出级是使用 单个晶体管 构建的,该晶体管 在导通时会将 输出拉低,在关闭时 看起来具有高阻抗。 现在,无论每个 输出上存在哪种 高电平或低 电平组合, 都会安全地将输出 驱动至已知状态。 如果两个输出都为 低电平,那么两个 输出晶体管都会 导通,将总体输出 向下拉至大约 0 伏。 如果两个输出都为 高电平,那么两个 晶体管都关闭, 看起来具有高阻抗, 从而允许通过上拉 电阻器将输出向上拉至 逻辑高电平。 如果一个输出为高电平, 一个输出为低电平,那么 低电平状态将处于 支配地位,因为与上拉 电阻器可以提供以尝试 将输出驱动为高电平的 电流相比,导通的晶体管能够 灌入的电流要大得多, 从而将输出拉低。 您可以查看右侧的 真值表,以了解 全部四种可能输入 状态下的逻辑行为。 正如您可以看到的, 这等效于逻辑“或” 功能。 该采用比较器的 逻辑“或”实现 通常称为 线或配置。 我们最后将讨论 比较器直流参数, 从而结束该系列的 第一个视频,任何 了解运算放大器的 人都应非常熟悉 这些参数。 该图显示了基本 比较器原理图, 以及众多最常见的 直流参数,其中 包括输入失调 电压或 VOS,表示为 与同相输入 串联的电压源; 输入偏置电流 或 IB;以及输入 偏置电流或 IOS,表示为流入 或流出比较器 输入的电流源; 输入共模 电压范围 或 VCM,在输入 晶体管饱和 或截止之前允许的 输入共模电压范围, 在现代器件上通常 从一个电源轨扩展至 另一个电源轨; 输入差分电压范围 或 VDFF,+IN 和 -IN 上 允许的差分 电压最大值; 电源轨的电压 输出高电平 或 VOH;相对于正 电源的最大逻辑 高电压;电源轨的电压 输出低电平或 VOL, 相对于接地 或负电源的 最小逻辑低电压; 输出短路电流 或 ISC,输出级 晶体管可以 拉取或灌入的 最大输出电流; 静态电流 或 IQ,当输出 电流为 0 时 器件的典型 电流消耗; 电源电压 范围或 VS,指定 操作的允许电源 电压范围。 可以指定 其他参数, 如开环 增益、电压 温漂、共模 抑制和电源 抑制。 但相对于上述 规格而言,它们 对于比较器的重要性要 低一些,因此较少予以考虑。 最关键的 直流规格之一 是输入失调 电压 VOS。 由于比较器的 VOS 会生成 与同相输入 串联的附加 直流电压,因此它对 比较器输出更改 状态的阈值 有重大的影响。 让我们来分析 一下具有三种 不同 VOS 值的同相 比较器电路,从而 更好地了解该影响。 请记住,对于 同相比较器, 如果 VIN 大于 VREF, Vout 将为高电平, 如果 VIN 小于 VREF, Vout 将为低电平。 在该示例中,我们将向 反相输入施加 2.5 伏的 基准电压。 正如您在右侧图的 深蓝色波形中看到的, 输入信号是 缓慢移动的 斜坡,从 2.46 伏转换为 2.54 伏。 失调电压会 增加输入信号, 以生成等于 VIN 加 VOS 的总 有效输入信号。 如果 VOS 等于 0, 那么总输入 电压等于 VIN 加 0, 电路会正常运行。 当 VIN 大于 2.5 伏时, Vout 为高电平。 当 VIN 小于 2.5 伏时, Vout 为低电平, 如红色波形所示。 如果 VOS 等于 正 10 毫伏, 那么总输入 电压等于 VIN 加 10 毫伏。 现在,输出将 在更低的 VIN 电压下进行转换, 因为通过 VOS 增加的 电压使总输入电压 能够更早地达到 2.5 伏。 您可以在橙色 波形中看到, 当 VIN 大于 2.49 伏时, Vout 为高电平, 当 VIN 小于 2.49 伏时, Vout 为低电平。 最后,如果 VOS 等于负 10 毫伏, 那么总输入 电压等于 VIN 减 10 毫伏。 现在,由于负 VOS 减去了一部分电压, 因此输出将在更高的 VIN 电压下进行转换。 您可以在淡蓝色 波形中看到, 当 VIN 大于 2.51 伏时, Vout 为高电平, 当 VIN 小于 2.51 伏时, Vout 为低电平。 请记住,不仅是 阈值电压会因 VOS 而变化,输出 波形的时序也会 受到影响。 例如,当 VOS 等于正 10 毫伏时, 输出波形会持续大约 600 毫秒保持高电平。 当 VOS 等于 负 10 毫伏时, 输出波形保持高电平的 时长会小于 400 毫秒。 该时序行为可能会在 特定的设计中引发问题, 但本示例中极缓慢 移动的输入信号会导致 最糟糕的情形。 为了帮助防止产生 这些类型的误差, 可以增大输入 信号的频率。 许多习惯于使用 现代运算放大器 进行设计的 工程师可能会 习惯于微伏级至几毫伏 范围内的失调电压。 比较器通常 具有稍高的 失调电压, 其范围为 大约正负 2 毫伏至 正负 15 毫伏。 在某些情况下, 比较器的失调电压 可能会完全改变 其输出信号。 考虑左侧 显示的电路, 一个反相比较器, 其输入信号由 数模转换器 或 DAC 进行提供。 数模转换器 会生根据数字 代码成模拟 电压或电流。 因此其输出通常看起来 随时间的推移在不同的 直流电压之间转换。 让我们来分析 一下当我们提供 1.25 伏基准电压 并且失调电压 从正 5 毫伏变为 0 毫伏再变为 负 5 毫伏时 该电路的输出。 在该电路中,将 VOS 添加到 VREF, 因此总有效基准 电压变为 VREF 加 VOS。 当 VOS 等于 正 5 毫伏时, 总基准电压等于 1.25 伏加 5 毫伏, 或 1.255 伏。 由于基准电压 增加,因此比较器 输出仅在输入 波形中两次变低, 如右上角的 蓝色图中 所示。 当 VOS 等于 0 伏时, 总基准电压等于 1.25 伏。 右侧的红色图中 显示了比较器输出。 当 VOS 等于 负 5 毫伏时, 总基准电压 现在等于 1.25 伏减 5 毫伏, 或 1.245 伏。 比较器输出再次 改变,右下角的 绿色图对此 进行了显示。 该示例的小输入 信号范围显示了 由于 VOS 而导致的 误差最糟糕情形。 为了防止产生 这些类型的误差, 应设法增大相对于 失调电压的输入 信号范围。 不过,当输入信号 在基准电压附近 波动时,仍然 可能会遇到 该类型的行为。 请务必观看该系列中的 后续视频,以学习 可帮助防止 产生这些类型的 误差的简单 但非常有用的技术。 本视频到此结束。 谢谢观看。 请尝试完成测验以 检查您对本视频 356

大家好,欢迎观看 TI 高精度实验室

视频系列,其中 介绍比较器应用。

比较器的作用是 比较两个模拟输入

信号并根据该比较 生成数字或逻辑

电平输出。

在本视频中,我们 将讨论模拟比较器的

基本功能及其 部分主要规格,

其中包括输入 失调电压或 VOS。

让我们首先 介绍比较器的

基本功能。

与标准运算放大器 类似,比较器具有

两个输入、一个输出 以及两个电源引脚。

从原理图的角度而言, 它与运算放大器类似,

但其预期功能 大不相同。

比较器之所以得此 名称,是因为它比较

施加到其输入端的 电压并根据输入

电平来设置 其输出电压。

一个输入被视为 主输入信号

或 VIN。

另一个 输入被

视为基准 信号 VREF。

这些输入可能具有 直流和交流分量。

可以将输出电压 Vout 设置为两种电平之一 --

高电平或逻辑 1, 或者低电平或逻辑 0。

输出高电平 VH 接近于

V+,即正 电源电压。

输出低电平 VL 接近于 0

伏或接地,或双电源 配置中的负电源。

该幻灯片中 显示的比较器

针对同相操作 进行了配置。

在该情况下, 输入信号 VIN

连接到 同相输入

+IN,基准 信号 VREF

连接到反相 输入 -IN。

如果 VIN 大于 VREF, 则比较器输出为高电平。

如果 VIN 小于 VREF, 则比较器输出为低电平。

比较器还可以 用于反相配置。

在该情况下, 输入信号 VIN

连接到反相 输入 -IN,

基准 信号 VREF

连接到 同相输入 +IN。

由于我们 定义输入

信号方式的改变, 可以将输出行为

视为反相。

现在,如果 VIN 大于 VREF,

那么比较器输出为低电平。

如果 VIN 小于 VREF, 则输出为高电平。

让我们来看看 双极比较器

LM139 的简化 内部设计。

此处的目标不是 讲授晶体管理论

或比较器设计的 详细工作原理,

而是为您提供有关比较器 如何工作的一般概念。

蓝色框中 所示的输入级

包含一个 PNP 差分放大器。

该差分级的 每侧都使用

达林顿 PNP 晶体管。

使用达林顿 连接晶体管

可增大输入阻抗, 降低输入偏置电流,

允许共模 输入电压

向下扩展至 0 伏。

该级中每个晶体管的 发射极电路中都具有

电流源,用于设置 发射极电流。

差分输入级中 晶体管的集电极

连接到用作 动态负载的

NPN 晶体管,如 青绿色部分所示。

最后,动态负载级的 输出耦合到 NPN

驱动器和集电极 开路输出级,如紫色

部分所示。

在比较器的 正常运行期间,

差分输入信号 +IN 减去 -IN

由输入差分 放大器的电压

增益进行放大。

该差分级的 输出在 T6 上形成,

并用于打开或 关闭输出级,

具体取决于输入极性。

为了更好地理解 内部功能,现在

让我们向该比较器 施加一些变化的输入

信号,并查看内部 电压在各个级

是如何变化的。

在该示例中, 我们将使用

采用反相配置的 比较器,VREF 连接到

+IN,VIN 连接到 -IN。

让我们首先向 +IN 施加 2.5 伏的基准

电压,向 -IN 施加 2.4 伏的输入信号。

那么我们要将 2.4 伏 与 2.5 伏基准进行比较。

这些电压以红色 显示在各个节点上。

底部提供了输入 为 2.4 伏的情形。

查看 -IN,可以 发现连接到

差分输入对的 该侧的晶体管

连接到动态 负载晶体管 T6。

T6 集电极处的 电压等于由

晶体管 T7 的 基极-发射极

电压钳制的 0.3 伏。

晶体管 T7 现在处于 导通状态,从而通过

下拉晶体管 T8 的 基极电压而将其关闭。

由于 T8 关闭, 因此其集电极

看起来具有高 阻抗,比较器的

输出电压 被连接到

正电源的 2 千欧上拉

电阻器拉高。

现在,让我们在 +IN 上 保持2.5 伏的基准,

但将 -IN 上的输入 信号更改为 2.65 伏。

我们现在要将 2.65 伏 与 2.5 伏基准进行比较。

晶体管 T4 和 T6 将导通并饱和,

从而使 T6 上的 电压变得很低。

T7 现在关闭,从而 允许 T8 完全导通

并将比较器输出电压 向下驱动至约 0 伏,

即逻辑低电平。

比较器根据 其输出级设计

分为两种 主要的类型。

这两种类型称为漏极 开路或集电极开路和

推挽,也称为 漏极-漏极,

我们的集电极-集电极。

集电极开路和 集电极-集电极

比较器是使用 双极晶体管构建的。

而漏极开路和漏极-漏极 比较器是使用 FET

构建的。

左侧的比较器和 前一张幻灯片中的

LM139 示例具有 集电极开路

输出以及包含 单个 NPN 双极

晶体管的输出级。

当该晶体管导通时, 它会主动地将电流

从集电极灌入到 发射极,并将输出

电压 VO 下拉至非常 接近于接地,即 0 伏。

输出摆动至 接近于接地的

程度取决于 集电极-发射极

饱和电压。

当晶体管关闭时, 其集电极看起来

具有高阻抗, 对输出电压

基本上没有影响。

在这种情况下, 会通过上拉

电阻器从 V+ 拉取较小的电流,

VO 升至 VOH, 即我们的逻辑 1。

如果不使用该 上拉电阻器,则 VO

可能会浮动至未知状态。

另一方面,推挽 比较器具有

包含一对 输出晶体管的

输出级。

该晶体管对中的 上部或下部晶体管

会导通,并主动拉取 或灌入电流,以根据

需要将输出驱动至 高电平或低电平。

在右侧的示例中, P 沟道上部 FET

导通,以拉取 电流并将输出

推至高电平。

同时 N 沟道 下部 FET 导通,

以灌入电流并将 输出拉至低电平。

该类型的比较器 不需要上拉电阻器。

比较器的常见期望 功能是生成逻辑“或”,

当其两个 输入中的

任一个打开时, 输出为逻辑低电平。

该功能块通常 可以通过将

两个比较器的 输出连接在

一起来实现。

不过,必须注意使用 正确类型的比较器,

我们以后会 讨论这一点。

让我们首先 考虑左侧的电路,

该电路具有两个输出 连接在一起的推挽器件。

请记住,推挽 比较器会主动

拉取或灌入电流,以将其 输出电压推高或拉低。

您可能已经 看出该电路

配置的问题。

但让我们来分析一下 其运行的不同可能性。

如果两个比较器的 输出都为高电平,

那么每个推挽 输出级中的顶部

晶体管会导通,输出 被驱动为高电平。

类似地,如果两个 输出都为低电平,

那么每个比较器中的 底部晶体管会导通,

输出被驱动为低电平。

当两个比较器试图 将输出驱动为不同的

状态时,问题 就出现了。

在这种情况下, 会发生冲突,

因为每个比较器 都试图拉取或灌入

电流,以强制输出 变为不同的电压。

这会导致出现高电流 情况,从而将输出驱动至

某种不确定的状态, 可能是高电平,

也可能是低电平。

正如您可以 想象的那样,

该情况是不利的, 甚至可能损坏器件。

因此,绝对不应 以这种方式

将推挽比较器 连接在一起。

另一方面,集电极 开路或漏极开路

比较器可以在该 方法下很好地工作。

请记住,集电极开路 或漏极开路比较器的

输出级是使用 单个晶体管

构建的,该晶体管 在导通时会将

输出拉低,在关闭时 看起来具有高阻抗。

现在,无论每个 输出上存在哪种

高电平或低 电平组合,

都会安全地将输出 驱动至已知状态。

如果两个输出都为 低电平,那么两个

输出晶体管都会 导通,将总体输出

向下拉至大约 0 伏。

如果两个输出都为 高电平,那么两个

晶体管都关闭, 看起来具有高阻抗,

从而允许通过上拉 电阻器将输出向上拉至

逻辑高电平。

如果一个输出为高电平, 一个输出为低电平,那么

低电平状态将处于 支配地位,因为与上拉

电阻器可以提供以尝试 将输出驱动为高电平的

电流相比,导通的晶体管能够 灌入的电流要大得多,

从而将输出拉低。

您可以查看右侧的 真值表,以了解

全部四种可能输入 状态下的逻辑行为。

正如您可以看到的, 这等效于逻辑“或”

功能。

该采用比较器的 逻辑“或”实现

通常称为 线或配置。

我们最后将讨论 比较器直流参数,

从而结束该系列的 第一个视频,任何

了解运算放大器的 人都应非常熟悉

这些参数。

该图显示了基本 比较器原理图,

以及众多最常见的 直流参数,其中

包括输入失调 电压或 VOS,表示为

与同相输入 串联的电压源;

输入偏置电流 或 IB;以及输入

偏置电流或 IOS,表示为流入

或流出比较器 输入的电流源;

输入共模 电压范围

或 VCM,在输入 晶体管饱和

或截止之前允许的 输入共模电压范围,

在现代器件上通常 从一个电源轨扩展至

另一个电源轨; 输入差分电压范围

或 VDFF,+IN 和 -IN 上

允许的差分 电压最大值;

电源轨的电压 输出高电平

或 VOH;相对于正 电源的最大逻辑

高电压;电源轨的电压 输出低电平或 VOL,

相对于接地 或负电源的

最小逻辑低电压; 输出短路电流

或 ISC,输出级 晶体管可以

拉取或灌入的 最大输出电流;

静态电流 或 IQ,当输出

电流为 0 时 器件的典型

电流消耗; 电源电压

范围或 VS,指定 操作的允许电源

电压范围。

可以指定 其他参数,

如开环 增益、电压

温漂、共模 抑制和电源

抑制。

但相对于上述 规格而言,它们

对于比较器的重要性要 低一些,因此较少予以考虑。

最关键的 直流规格之一

是输入失调 电压 VOS。

由于比较器的 VOS 会生成

与同相输入 串联的附加

直流电压,因此它对 比较器输出更改

状态的阈值 有重大的影响。

让我们来分析 一下具有三种

不同 VOS 值的同相 比较器电路,从而

更好地了解该影响。

请记住,对于 同相比较器,

如果 VIN 大于 VREF, Vout 将为高电平,

如果 VIN 小于 VREF, Vout 将为低电平。

在该示例中,我们将向 反相输入施加 2.5 伏的

基准电压。

正如您在右侧图的 深蓝色波形中看到的,

输入信号是 缓慢移动的

斜坡,从 2.46 伏转换为

2.54 伏。

失调电压会 增加输入信号,

以生成等于 VIN 加 VOS 的总

有效输入信号。

如果 VOS 等于 0, 那么总输入

电压等于 VIN 加 0, 电路会正常运行。

当 VIN 大于 2.5 伏时, Vout 为高电平。

当 VIN 小于 2.5 伏时,

Vout 为低电平, 如红色波形所示。

如果 VOS 等于 正 10 毫伏,

那么总输入 电压等于 VIN

加 10 毫伏。

现在,输出将 在更低的 VIN

电压下进行转换, 因为通过 VOS 增加的

电压使总输入电压 能够更早地达到 2.5 伏。

您可以在橙色 波形中看到,

当 VIN 大于 2.49 伏时, Vout 为高电平,

当 VIN 小于 2.49 伏时, Vout 为低电平。

最后,如果 VOS 等于负 10 毫伏,

那么总输入 电压等于 VIN

减 10 毫伏。

现在,由于负 VOS 减去了一部分电压,

因此输出将在更高的 VIN 电压下进行转换。

您可以在淡蓝色 波形中看到,

当 VIN 大于 2.51 伏时, Vout 为高电平,

当 VIN 小于 2.51 伏时, Vout 为低电平。

请记住,不仅是 阈值电压会因

VOS 而变化,输出 波形的时序也会

受到影响。

例如,当 VOS 等于正 10 毫伏时,

输出波形会持续大约 600 毫秒保持高电平。

当 VOS 等于 负 10 毫伏时,

输出波形保持高电平的 时长会小于 400 毫秒。

该时序行为可能会在 特定的设计中引发问题,

但本示例中极缓慢 移动的输入信号会导致

最糟糕的情形。

为了帮助防止产生 这些类型的误差,

可以增大输入 信号的频率。

许多习惯于使用 现代运算放大器

进行设计的 工程师可能会

习惯于微伏级至几毫伏 范围内的失调电压。

比较器通常 具有稍高的

失调电压, 其范围为

大约正负 2 毫伏至

正负 15 毫伏。

在某些情况下, 比较器的失调电压

可能会完全改变 其输出信号。

考虑左侧 显示的电路,

一个反相比较器, 其输入信号由

数模转换器 或 DAC 进行提供。

数模转换器 会生根据数字

代码成模拟 电压或电流。

因此其输出通常看起来 随时间的推移在不同的

直流电压之间转换。

让我们来分析 一下当我们提供

1.25 伏基准电压 并且失调电压

从正 5 毫伏变为 0 毫伏再变为

负 5 毫伏时 该电路的输出。

在该电路中,将 VOS 添加到 VREF,

因此总有效基准 电压变为 VREF 加 VOS。

当 VOS 等于 正 5 毫伏时,

总基准电压等于 1.25 伏加 5 毫伏,

或 1.255 伏。

由于基准电压 增加,因此比较器

输出仅在输入 波形中两次变低,

如右上角的 蓝色图中

所示。

当 VOS 等于 0 伏时, 总基准电压等于

1.25 伏。

右侧的红色图中 显示了比较器输出。

当 VOS 等于 负 5 毫伏时,

总基准电压 现在等于 1.25

伏减 5 毫伏, 或 1.245 伏。

比较器输出再次 改变,右下角的

绿色图对此 进行了显示。

该示例的小输入 信号范围显示了

由于 VOS 而导致的 误差最糟糕情形。

为了防止产生 这些类型的误差,

应设法增大相对于 失调电压的输入

信号范围。

不过,当输入信号 在基准电压附近

波动时,仍然 可能会遇到

该类型的行为。

请务必观看该系列中的 后续视频,以学习

可帮助防止 产生这些类型的

误差的简单 但非常有用的技术。

本视频到此结束。

谢谢观看。

请尝试完成测验以 检查您对本视频 356

手机看

扫码用手机观看

视频简介

视频简介

比较器应用1

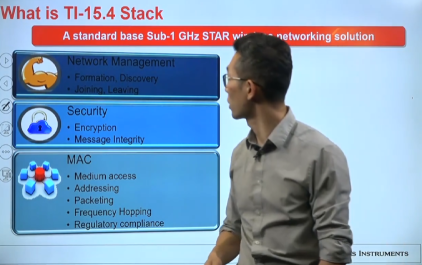

所属课程:TI 高精度实验室-比较器应用

发布时间:2020.05.28

视频集数:4

本节视频时长:00:17:29

了解比较器的理论,技术,应用等!

在本系列中,您将了解比较器的基本功能以及外部噪声的影响,单电源和双电源之间的差异,使用运算放大器作为比较器的利弊等等。