基于AMIC产品的工业通信总线设计方案-1.2 PRU Implement Industrial Communication

Loading the player...

将在30s后自动为您播放下一课程

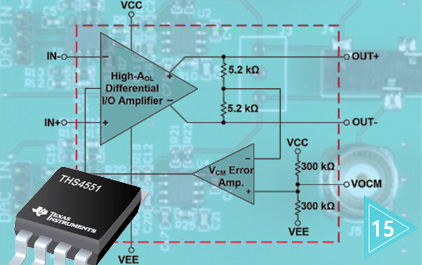

接下来的章节大家比较感兴趣了 如何用PR实现工业通讯总线协议 首先我想跟大家探讨一下 大家可以想一想 工业通讯总线协议为什么不容易做 或者说为什么用EtherCAT去做 刚才提到几点 扩展性好 应该不算是对于技术上的难点 吞吐量大 可以说我有一个 百兆网甚至是千兆网的载体 是不是就OK了 其实我们可以看一下 Ethercat这边的定义 有助于我们去理解工业通讯协议 去实现这个工业通讯协议中 你会遇到什么样的跳战 这样就能理解TI 的架构 为什么能满足你的设定需求 Ethercat目前在中国市场 铺的还是非常开的 Ethercat主站 我们直接看到下面 implementation这块 主站这方面的实现 往往是存储转发机制 很简单 就是我的每个数据包过来 相当于说每个CPU都会处理的 但是对于从站这个地方 大家看到了没有 它叫on-the-fly的processing 很简单 就是我是 free to capture 给大家一个简单的例子 我们有一个msater带六个节点 那我的Ethercat往往是由 总线或者是环型结构去做的 我们想一个总线结构 第一个master接着第二个的 一个master接着第一个slave接着 第二个slave接第三第四第五第六 每一个slave之间都是手拉手 一进一出的结构 大家可以看system level view 比如说我们最左上角的 就是第一个 紧接着第二个 第三个 第四个 我最后一个节点的 收到我master侧的数据时延 是由前面三个的slave节点的 时延的总和决定的 所以它是一个叠加的过程 这个叠加的过程带来一个什么问题 就是我的slave这边的时延必须要很快 必须要很小 如果我slave节点口比较大 那会有个什么情况 如果每个slave节点相对来说不可控 抖动比较大 就是我们说jitter 或者是抖动比较大的话 那我环路想要做到 比如说一毫秒同周期 我能带的节点就比较少了 因为我在算每个节点时延的时候 我都会每个节点时延中 最消耗资源或者抖动最差的情况 我才能保证环路的稳定 所以 Ethercat的slave节点这块 重要的特点就是我必须要 on the fly的去capture我的数据 这样我才能保证我的节点时延比较小 所以,对slave的 实质性要求是比较高的 对于master它是不会再说 像我们平常看一个 CPU去处理一个数据包 数据包过来了 我就解析 比如说ethernet ethercat net 我去比对 这些东西的mac地址和 我自己的IP地址这些东西 是不是我的 如果不是我的我再转发走 其实对于EtherCAT而言的话 它是没有办法去忍受这个时延的 它必须要on the fly动态的 去做一个capture 去做所谓的数据端的切片 数据端切片过后 我再去做所谓的数据处理 去拿到自己的 数据过后我再去做处理 然后在下一个同步轴器之中再去丢掉 再丢回去 所以对master侧的这一块来说 master侧的这一块其实有一个压力 就是我要保证在一个同步周期内 把我底下这些数据的处理 就是要去处理掉的信息及时处理掉 如果我只是简单做一个数据收集 那我master侧对于 CPU的性能就没有这么高 但倘若我master侧这块是 类似于做运动控制器的 那我要去规划 调整我 下面节点的运动控制轨迹 这时候master侧的对于arm 的运算能力以及对dsp的使用能力 就可能是你关注的一个焦点 而对于slave侧的话 最主要的一点就是 我要非常快的把数据端切片拿下来 一般来说 我们CPU体系之中的接口 我们可以看一下 下一张 一般来说 我们CPU的 外设接口是很难做到的 而pru单独这块体系中 它是怎么去做到这块 这张图能够给大家一个解释 大家可以看到 一般来说 比如说我们就拿gpl口做解释好了 这里有一个gpl口 我们的arm侧 最左侧的是我们的arm核 arm核我想访问这个gpl口 往往是挂在很多总线上 每一条总线上都会有自己的总线带宽 也会有总线仲裁 那我arm想要访问到 一个gpl口的外设状态的话 我是要通过L4 L3 然后再通过各种数据指令集的缓存 最终才能够拿到这个接口 所以这就是为什么外面普通以太网 cpsw 就是我们的普通以太网 很难以实施高效做处理的一个原因 对于pru来说 它有什么差别呢 pru是跟arm相对来说独立的一个体系 这个体系跟arm的位置是等同的 而且它有自己独立的instruction RAM 还有Data RAM 所以它能自己独立的运转 当你把固件这些东西 去load到pru核里后 它能够很快的自己 capture到外面io电频的变换 因为pru这边的io口 与这个不同 这个是挂在总线上的 一级一级进去的 这边是io口 直通寄存器的 pru到io口直通寄存器 代表着什么含义 这里边我们是200兆的pru 我一个指令周期就是五个纳秒 pru的汇编大多数指令 都是单指令周期的运算 也就是说五个纳秒一个周期 往往 我就能capture到外面的变换了 所以,这样子的话 只要外面有数据进来 我的pru能够很迅速的capture到 而且 pru这里面往往 就像是单片机一样 我就是一个从上往下的顺序执行结构 就跟我们原来学习hello world一样 就是一个主man 你一个主man下来过后 是什么样子就是什么样子 所有的逻辑控制 你都可以去按照指令周期去算出来的 所以它的指令执行会非常高效 在pru的这一点上 就保证了它独立的处理暗核 不会 受到外界CPU loading干扰这个特性 所以它能够去做我们 刚才提到的on the fly capture 有人可能问这地方只是io 难道我要把Ethercat作为io去做吗 其实不是大家看 黄色的peripherals就包含了 上页这张图里面的 黄色的里面就包括了 我们这方有mii的接口 这个就是我们的百兆以太网 所以它跟gpl口也是一样的 都是直通到我们pru这侧的 除了mii之外 我们还会有uart 这就是为什么我们还可以去做 类似于periphery bus这些东西的原因 而periphery net Ethercat之类的 都要依赖于我们的mii接口 和pru核 往往是一个pru核做一进 另一个pru核和mii做一出 所以等于是单核单用 基本上我们看到在a8 体系架构中的一个pru子系统中 我们都是两个核 一个pru子系统两个核 这两个核 一个进 一个出 这两个核之间是可以相互发中断的 并且pru拥有对全局的访问权限 当然 在这地方能访问是一回事 但是arm这块要规划好 我不要发生资源冲突 比如说我一直在做一些接口的轮循 pru进来够后 可能会有打架的情况 这个我们在系统 设计层面上是会去避免的 但是从功能上来说 它是有访问全局的 它就可以通过电路dma 去把我的数据实时的 从内部的RAM空间之中 搬到外部的ddr上 它跟arm之间 也可以有一个中断去做访问 给arm一个中断 我的处理机制就可以 变成pru把所有的数据capture完 处理完了过后 丢到我的ddr上 最后给arm一个中断 每一次接到这个中断的时候 对它来讲没有loading 它就把刚才提到的那些复杂的切片 和这些实时的算法 在ddr上的数据 把它这个算法中的数据全都拿到了 直接去处理职业数据就OK了 然后发的话 也是有pru这边 去通过自己独立的ram 去运行 去发的 所以这样一来 pru就能做到 实时 高效的通信 所以 我们回到这张图上来 所以,刚才我提到的这点 就是“pru为什么在这样一个体系 架构之中能够做工业通信的ltave” 作为主站来说 它有没有什么好处呢 大家可以看到 主站我刚刚提到的一点是 主站,并不要求说 你立刻就要去保证节点时延 因为节点时延的保障 是有slave去进行的 那首先我刚才提到了一点 一个就是说CPU的性能 你做算法和处理数据的能力 这是非常重要的 对通信上来讲 它 一般来讲会怎么去做 目前来讲我们看到有两种方式 一种就是在普通的以太网上 通过所谓软的方式 加载一层Ethercat的通信 Ethercat的协议 去完成Ethercat master的功能 还有一个就是用pru去实现 pru实现的好处是什么 刚才我们提到pru的 实时控制性能力非常强 所以在这个地方的话 我们pru可以去做到一个功能 叫Time trick set TTS的这样一个功能 包括后面的Time sensitivity network 这个tsn的一些能力 都是可以在pru这个体系上实现的 如果你把pru换成对外界的io口 就是相当于说挂在 L3 L4上这些东西的能力 那它插的东西就不止一个等级了 一个是总线上带宽通信的仲裁的时间 这个东西被节约掉了 另外的就是指令周期方面的时间 排队时间被节约掉了 单指令周期 L口直通进行器 这是它的特点 这也是为什么它能够成为 工业通信上一个重要应用手段的原因 这里给大家一个 重要的叫bench Mark 一个数据对比 大家可以看到 左侧我们用arm的gpio 做了一些测试 我们在一个arm上拉了gpio 这边是直接使用汇编 去写的一个拉高拉低 右边是我们在pru体系上 去用了汇编去写的拉高拉低 事实上 从测试结果看 之间的速度差距可以达到40倍之差 通过这张图 希望大家能够 更加理解住pru它的实时特性 相对来说还是比arm 这边的外设处理器 还是强大了和好几个等级的 所以它能够作比较多的事情 回到我们实现的这个层面上 有人可能问了 如果arm pru这块都是用去汇编写的 我要怎么去hold这个事情 这开发难度对我来说有多大 事实上 TI在这边的话 是把所有的固件和相关应用程序和api都已经写好了 所有第三方的资源都已经囊括在内了 真正对于用户的时候用来说 他只需要使用上层的api就OK 下层的改动会非常小 特别是针对固件这边的改动 基本上大家不太会碰到 如果说一定会碰到的场景是什么样的 TI现在目前为了 很多工业客户去开放的出来的 这个开源性的Ethernet架构 因为现在很多客户想去做 自己自定义的 工业控制通讯协议 比如说我们看看国内 几个大的运动控制器的生产厂商 都有自定义的协议 都是 基于百兆甚至千兆以太网去做的 TI有一套开源的 基于pru的协议框架 这个(听不清) 也是release在了官网上 大家感兴趣的话 可以同过pru的关键字眼去搜索 能够找到这个东西 这里面能够把pru内部的汇编 包括整个汇编工程 拉出来给到大家 大家可以在汇编工程上去做修改 它是直接把连接的建立到连接的协商 到很多内部连接数据 交换机制之类的都给规划出来了 你是可以直接跳进去 改里面汇编的机制的 改汇编对于有些朋友来说会比较陌生 这个其实在TI这边来讲 首先提供了两种方式 一种是汇编 一种是C语言 因为C语言我们已经实现了 在pru上有一个pru的编译器 可以把你的C语言转成汇编 这样对于很多初级和终极玩家来说 会比较容易上手 汇编主要的一个好处就是 在处理这种复杂的通讯协议的时候 你的实时性可以 精确到每一个指令周期 这个对于很多朋友 老鸟来说 这个还是比较重要的 很多人在这个基础上 去做二次开发的时候 会需要很多的资料 这种资料我们已经把它收集到 我们当前的pru的Tools complier上了 大家可以在我们的 Wiki上去搜一下prucomplier 和pru的汇编 我们用(听不清) 编译的那套体系和流程 这个讲说的非常明白 其实总的汇编 指令大概也就是二三十条 总的来说不是很困难 上手给大家一点信心 就是在TI这边 之前带实习生 就是有来做毕设的 我们曾经有一个毕设的学生 做一个pru camera的一个应用 大概是用了两个多月 在我们资深FAE的带领下 他就独立完成了对于pru 实现摄像头的一个功能 所以这个东西的实现并没有 大家想象的这么困难 感兴趣的话大家可以会后去看一看 在我看目前TI的方案之中 我们回到这一点上 pru的特性刚才跟大家介绍过了 它实现工业通讯协议的优势 其实从整体成本上来说 这个为大家节省的还是比较多的 我们知道ASICs跟FPGAs现在的 价格相对来说是比较昂贵的 基本上在TI的arm+pru架构中 我们推出了amic110的产品 以及am335系列的产品 就是想在这个市场上 给大家带来一个福利 基本上能够做到整体的 BOM成本节约大概20%—30% 在右边的产品构架上 我们在不同的应用领域内 我们可以有不同的玩法 比如说刚才提到的motion control 如果是motion control+ 带有Ethercat master的 就可以选择用 arm+dsp+pru这种完善的体系 我们am57系列就可以做到这些事情 如果说你响应的 只是简单的逻辑控制器 或者是带有小motion功能的plc 那又要有Ethercat 那我们的an335系列的 产品就可以满足需求 如果你说其实 我想要做的是一个兼容性的平台 我的工业通讯协议可能在 我以后的路标设备之中 现在我只是想预留这样一个可能性 我现在想做的 只是一些中低端的 比如说 做一些can 485 一些很平常的这种通讯方式的 那一样 我们的纯arm核的产品 也是比较适合发展 也是比较适应大家选择的 因为我们的arm+pru+dsp这套架构 往往设计的理念都是PIN 2 PIN结合 特别是在我们amic110这代产品之中 它基本上是把a8整个芯片 做到了PIN2 PIN的兼容 所以不管是面对 高端的应用还是中低端的应用 都是比较合适的 这张就是我们am335x的系统框图 am335x这种框图之中 点几个重点去讲 大家可能会关心到的 一个是a8的主频 a8的主频的话 这边有300 600 800 1G 当然了 如果你做所谓工业通信的时候 肯定是不需要lcd的 但是对于下面经常被问到的can通信 spi通信 UR的通信 pru这些东西肯定是必备的 然后这些东西会不会有 以太网通信会不会有 这些东西都是可配选项 所以amic110也是在这个市场上 应运而生出来的新的产品 它基本上就是把刚才我们提到的 因为你pru这块 已经能做工业通信控制了 那么我们的a8其实本身的工业通信 能力在外设的基础上并没有这么强 这就是为什么之前 单ASIC去做的功能全在这儿了 我们配了一个a8的300兆的mpu 关于3D加速器 lcd显示这一块全都被除掉了 包括之前的一些音频接口 包括之前的一些pw 不好意思 这个是EtherCap和千兆以太网 千兆以太网这边可能就不太需要了 所以定制化 出来了一个amic110的产品 amic110的产品的话相对来说 对于335的性价比就会高很多 除此之外的话 如果说我们还需要更高端一点的 比如刚才提到的带有 运动控制器的motion control 然后可能是arm+dsp+pru架构的 那就是am57x系列 然后plc逻辑控制器这块 我们可以用335 可以用437 可以用57 这个差异点也是在于说 你有没有复杂的联动算法 你有没有工业通讯的需求 所以 在这一套体系架构中 通过sitara系列的产品能为 大家带来相应的设计价值 能让大家使用一个规划的平台 去完善整个系统解决方案 大家知道 其实在工业上面 去验证一个平台的稳定性 往往是 需要花费两年 三年甚至更多时间 这种时间的积累对 各位研发来说也是一笔财富 所以如果能够通过 同样一套体系架构让你玩转整套产品 这个对开发来说的价值是不言而喻的 那TI在立足于这一点 除了在我们当前的 a8 a9 a15的芯片每一代之间 就是每一代产品系列之间 做到了PIN2 PIN 在跨代 比如说a8升a9 a9升a15 包括 后面我们升到a53的体系架构之中 我们也考虑了软件的兼容性这一点 希望大家把软件开发的门槛降到最低 目前的peocessor SDK 便是针对于我们当前的 a8 a9 a15全系列支持的一个SDK 它把所有目录的解析 所有dts文件的架构和位置 基本上都是使用了同样的框架 这样对于已经开发过a8的兄弟们而言 你网上走a9或者a15还是比较容易的

接下来的章节大家比较感兴趣了 如何用PR实现工业通讯总线协议 首先我想跟大家探讨一下 大家可以想一想 工业通讯总线协议为什么不容易做 或者说为什么用EtherCAT去做 刚才提到几点 扩展性好 应该不算是对于技术上的难点 吞吐量大 可以说我有一个 百兆网甚至是千兆网的载体 是不是就OK了 其实我们可以看一下 Ethercat这边的定义 有助于我们去理解工业通讯协议 去实现这个工业通讯协议中 你会遇到什么样的跳战 这样就能理解TI 的架构 为什么能满足你的设定需求 Ethercat目前在中国市场 铺的还是非常开的 Ethercat主站 我们直接看到下面 implementation这块 主站这方面的实现 往往是存储转发机制 很简单 就是我的每个数据包过来 相当于说每个CPU都会处理的 但是对于从站这个地方 大家看到了没有 它叫on-the-fly的processing 很简单 就是我是 free to capture 给大家一个简单的例子 我们有一个msater带六个节点 那我的Ethercat往往是由 总线或者是环型结构去做的 我们想一个总线结构 第一个master接着第二个的 一个master接着第一个slave接着 第二个slave接第三第四第五第六 每一个slave之间都是手拉手 一进一出的结构 大家可以看system level view 比如说我们最左上角的 就是第一个 紧接着第二个 第三个 第四个 我最后一个节点的 收到我master侧的数据时延 是由前面三个的slave节点的 时延的总和决定的 所以它是一个叠加的过程 这个叠加的过程带来一个什么问题 就是我的slave这边的时延必须要很快 必须要很小 如果我slave节点口比较大 那会有个什么情况 如果每个slave节点相对来说不可控 抖动比较大 就是我们说jitter 或者是抖动比较大的话 那我环路想要做到 比如说一毫秒同周期 我能带的节点就比较少了 因为我在算每个节点时延的时候 我都会每个节点时延中 最消耗资源或者抖动最差的情况 我才能保证环路的稳定 所以 Ethercat的slave节点这块 重要的特点就是我必须要 on the fly的去capture我的数据 这样我才能保证我的节点时延比较小 所以,对slave的 实质性要求是比较高的 对于master它是不会再说 像我们平常看一个 CPU去处理一个数据包 数据包过来了 我就解析 比如说ethernet ethercat net 我去比对 这些东西的mac地址和 我自己的IP地址这些东西 是不是我的 如果不是我的我再转发走 其实对于EtherCAT而言的话 它是没有办法去忍受这个时延的 它必须要on the fly动态的 去做一个capture 去做所谓的数据端的切片 数据端切片过后 我再去做所谓的数据处理 去拿到自己的 数据过后我再去做处理 然后在下一个同步轴器之中再去丢掉 再丢回去 所以对master侧的这一块来说 master侧的这一块其实有一个压力 就是我要保证在一个同步周期内 把我底下这些数据的处理 就是要去处理掉的信息及时处理掉 如果我只是简单做一个数据收集 那我master侧对于 CPU的性能就没有这么高 但倘若我master侧这块是 类似于做运动控制器的 那我要去规划 调整我 下面节点的运动控制轨迹 这时候master侧的对于arm 的运算能力以及对dsp的使用能力 就可能是你关注的一个焦点 而对于slave侧的话 最主要的一点就是 我要非常快的把数据端切片拿下来 一般来说 我们CPU体系之中的接口 我们可以看一下 下一张 一般来说 我们CPU的 外设接口是很难做到的 而pru单独这块体系中 它是怎么去做到这块 这张图能够给大家一个解释 大家可以看到 一般来说 比如说我们就拿gpl口做解释好了 这里有一个gpl口 我们的arm侧 最左侧的是我们的arm核 arm核我想访问这个gpl口 往往是挂在很多总线上 每一条总线上都会有自己的总线带宽 也会有总线仲裁 那我arm想要访问到 一个gpl口的外设状态的话 我是要通过L4 L3 然后再通过各种数据指令集的缓存 最终才能够拿到这个接口 所以这就是为什么外面普通以太网 cpsw 就是我们的普通以太网 很难以实施高效做处理的一个原因 对于pru来说 它有什么差别呢 pru是跟arm相对来说独立的一个体系 这个体系跟arm的位置是等同的 而且它有自己独立的instruction RAM 还有Data RAM 所以它能自己独立的运转 当你把固件这些东西 去load到pru核里后 它能够很快的自己 capture到外面io电频的变换 因为pru这边的io口 与这个不同 这个是挂在总线上的 一级一级进去的 这边是io口 直通寄存器的 pru到io口直通寄存器 代表着什么含义 这里边我们是200兆的pru 我一个指令周期就是五个纳秒 pru的汇编大多数指令 都是单指令周期的运算 也就是说五个纳秒一个周期 往往 我就能capture到外面的变换了 所以,这样子的话 只要外面有数据进来 我的pru能够很迅速的capture到 而且 pru这里面往往 就像是单片机一样 我就是一个从上往下的顺序执行结构 就跟我们原来学习hello world一样 就是一个主man 你一个主man下来过后 是什么样子就是什么样子 所有的逻辑控制 你都可以去按照指令周期去算出来的 所以它的指令执行会非常高效 在pru的这一点上 就保证了它独立的处理暗核 不会 受到外界CPU loading干扰这个特性 所以它能够去做我们 刚才提到的on the fly capture 有人可能问这地方只是io 难道我要把Ethercat作为io去做吗 其实不是大家看 黄色的peripherals就包含了 上页这张图里面的 黄色的里面就包括了 我们这方有mii的接口 这个就是我们的百兆以太网 所以它跟gpl口也是一样的 都是直通到我们pru这侧的 除了mii之外 我们还会有uart 这就是为什么我们还可以去做 类似于periphery bus这些东西的原因 而periphery net Ethercat之类的 都要依赖于我们的mii接口 和pru核 往往是一个pru核做一进 另一个pru核和mii做一出 所以等于是单核单用 基本上我们看到在a8 体系架构中的一个pru子系统中 我们都是两个核 一个pru子系统两个核 这两个核 一个进 一个出 这两个核之间是可以相互发中断的 并且pru拥有对全局的访问权限 当然 在这地方能访问是一回事 但是arm这块要规划好 我不要发生资源冲突 比如说我一直在做一些接口的轮循 pru进来够后 可能会有打架的情况 这个我们在系统 设计层面上是会去避免的 但是从功能上来说 它是有访问全局的 它就可以通过电路dma 去把我的数据实时的 从内部的RAM空间之中 搬到外部的ddr上 它跟arm之间 也可以有一个中断去做访问 给arm一个中断 我的处理机制就可以 变成pru把所有的数据capture完 处理完了过后 丢到我的ddr上 最后给arm一个中断 每一次接到这个中断的时候 对它来讲没有loading 它就把刚才提到的那些复杂的切片 和这些实时的算法 在ddr上的数据 把它这个算法中的数据全都拿到了 直接去处理职业数据就OK了 然后发的话 也是有pru这边 去通过自己独立的ram 去运行 去发的 所以这样一来 pru就能做到 实时 高效的通信 所以 我们回到这张图上来 所以,刚才我提到的这点 就是“pru为什么在这样一个体系 架构之中能够做工业通信的ltave” 作为主站来说 它有没有什么好处呢 大家可以看到 主站我刚刚提到的一点是 主站,并不要求说 你立刻就要去保证节点时延 因为节点时延的保障 是有slave去进行的 那首先我刚才提到了一点 一个就是说CPU的性能 你做算法和处理数据的能力 这是非常重要的 对通信上来讲 它 一般来讲会怎么去做 目前来讲我们看到有两种方式 一种就是在普通的以太网上 通过所谓软的方式 加载一层Ethercat的通信 Ethercat的协议 去完成Ethercat master的功能 还有一个就是用pru去实现 pru实现的好处是什么 刚才我们提到pru的 实时控制性能力非常强 所以在这个地方的话 我们pru可以去做到一个功能 叫Time trick set TTS的这样一个功能 包括后面的Time sensitivity network 这个tsn的一些能力 都是可以在pru这个体系上实现的 如果你把pru换成对外界的io口 就是相当于说挂在 L3 L4上这些东西的能力 那它插的东西就不止一个等级了 一个是总线上带宽通信的仲裁的时间 这个东西被节约掉了 另外的就是指令周期方面的时间 排队时间被节约掉了 单指令周期 L口直通进行器 这是它的特点 这也是为什么它能够成为 工业通信上一个重要应用手段的原因 这里给大家一个 重要的叫bench Mark 一个数据对比 大家可以看到 左侧我们用arm的gpio 做了一些测试 我们在一个arm上拉了gpio 这边是直接使用汇编 去写的一个拉高拉低 右边是我们在pru体系上 去用了汇编去写的拉高拉低 事实上 从测试结果看 之间的速度差距可以达到40倍之差 通过这张图 希望大家能够 更加理解住pru它的实时特性 相对来说还是比arm 这边的外设处理器 还是强大了和好几个等级的 所以它能够作比较多的事情 回到我们实现的这个层面上 有人可能问了 如果arm pru这块都是用去汇编写的 我要怎么去hold这个事情 这开发难度对我来说有多大 事实上 TI在这边的话 是把所有的固件和相关应用程序和api都已经写好了 所有第三方的资源都已经囊括在内了 真正对于用户的时候用来说 他只需要使用上层的api就OK 下层的改动会非常小 特别是针对固件这边的改动 基本上大家不太会碰到 如果说一定会碰到的场景是什么样的 TI现在目前为了 很多工业客户去开放的出来的 这个开源性的Ethernet架构 因为现在很多客户想去做 自己自定义的 工业控制通讯协议 比如说我们看看国内 几个大的运动控制器的生产厂商 都有自定义的协议 都是 基于百兆甚至千兆以太网去做的 TI有一套开源的 基于pru的协议框架 这个(听不清) 也是release在了官网上 大家感兴趣的话 可以同过pru的关键字眼去搜索 能够找到这个东西 这里面能够把pru内部的汇编 包括整个汇编工程 拉出来给到大家 大家可以在汇编工程上去做修改 它是直接把连接的建立到连接的协商 到很多内部连接数据 交换机制之类的都给规划出来了 你是可以直接跳进去 改里面汇编的机制的 改汇编对于有些朋友来说会比较陌生 这个其实在TI这边来讲 首先提供了两种方式 一种是汇编 一种是C语言 因为C语言我们已经实现了 在pru上有一个pru的编译器 可以把你的C语言转成汇编 这样对于很多初级和终极玩家来说 会比较容易上手 汇编主要的一个好处就是 在处理这种复杂的通讯协议的时候 你的实时性可以 精确到每一个指令周期 这个对于很多朋友 老鸟来说 这个还是比较重要的 很多人在这个基础上 去做二次开发的时候 会需要很多的资料 这种资料我们已经把它收集到 我们当前的pru的Tools complier上了 大家可以在我们的 Wiki上去搜一下prucomplier 和pru的汇编 我们用(听不清) 编译的那套体系和流程 这个讲说的非常明白 其实总的汇编 指令大概也就是二三十条 总的来说不是很困难 上手给大家一点信心 就是在TI这边 之前带实习生 就是有来做毕设的 我们曾经有一个毕设的学生 做一个pru camera的一个应用 大概是用了两个多月 在我们资深FAE的带领下 他就独立完成了对于pru 实现摄像头的一个功能 所以这个东西的实现并没有 大家想象的这么困难 感兴趣的话大家可以会后去看一看 在我看目前TI的方案之中 我们回到这一点上 pru的特性刚才跟大家介绍过了 它实现工业通讯协议的优势 其实从整体成本上来说 这个为大家节省的还是比较多的 我们知道ASICs跟FPGAs现在的 价格相对来说是比较昂贵的 基本上在TI的arm+pru架构中 我们推出了amic110的产品 以及am335系列的产品 就是想在这个市场上 给大家带来一个福利 基本上能够做到整体的 BOM成本节约大概20%—30% 在右边的产品构架上 我们在不同的应用领域内 我们可以有不同的玩法 比如说刚才提到的motion control 如果是motion control+ 带有Ethercat master的 就可以选择用 arm+dsp+pru这种完善的体系 我们am57系列就可以做到这些事情 如果说你响应的 只是简单的逻辑控制器 或者是带有小motion功能的plc 那又要有Ethercat 那我们的an335系列的 产品就可以满足需求 如果你说其实 我想要做的是一个兼容性的平台 我的工业通讯协议可能在 我以后的路标设备之中 现在我只是想预留这样一个可能性 我现在想做的 只是一些中低端的 比如说 做一些can 485 一些很平常的这种通讯方式的 那一样 我们的纯arm核的产品 也是比较适合发展 也是比较适应大家选择的 因为我们的arm+pru+dsp这套架构 往往设计的理念都是PIN 2 PIN结合 特别是在我们amic110这代产品之中 它基本上是把a8整个芯片 做到了PIN2 PIN的兼容 所以不管是面对 高端的应用还是中低端的应用 都是比较合适的 这张就是我们am335x的系统框图 am335x这种框图之中 点几个重点去讲 大家可能会关心到的 一个是a8的主频 a8的主频的话 这边有300 600 800 1G 当然了 如果你做所谓工业通信的时候 肯定是不需要lcd的 但是对于下面经常被问到的can通信 spi通信 UR的通信 pru这些东西肯定是必备的 然后这些东西会不会有 以太网通信会不会有 这些东西都是可配选项 所以amic110也是在这个市场上 应运而生出来的新的产品 它基本上就是把刚才我们提到的 因为你pru这块 已经能做工业通信控制了 那么我们的a8其实本身的工业通信 能力在外设的基础上并没有这么强 这就是为什么之前 单ASIC去做的功能全在这儿了 我们配了一个a8的300兆的mpu 关于3D加速器 lcd显示这一块全都被除掉了 包括之前的一些音频接口 包括之前的一些pw 不好意思 这个是EtherCap和千兆以太网 千兆以太网这边可能就不太需要了 所以定制化 出来了一个amic110的产品 amic110的产品的话相对来说 对于335的性价比就会高很多 除此之外的话 如果说我们还需要更高端一点的 比如刚才提到的带有 运动控制器的motion control 然后可能是arm+dsp+pru架构的 那就是am57x系列 然后plc逻辑控制器这块 我们可以用335 可以用437 可以用57 这个差异点也是在于说 你有没有复杂的联动算法 你有没有工业通讯的需求 所以 在这一套体系架构中 通过sitara系列的产品能为 大家带来相应的设计价值 能让大家使用一个规划的平台 去完善整个系统解决方案 大家知道 其实在工业上面 去验证一个平台的稳定性 往往是 需要花费两年 三年甚至更多时间 这种时间的积累对 各位研发来说也是一笔财富 所以如果能够通过 同样一套体系架构让你玩转整套产品 这个对开发来说的价值是不言而喻的 那TI在立足于这一点 除了在我们当前的 a8 a9 a15的芯片每一代之间 就是每一代产品系列之间 做到了PIN2 PIN 在跨代 比如说a8升a9 a9升a15 包括 后面我们升到a53的体系架构之中 我们也考虑了软件的兼容性这一点 希望大家把软件开发的门槛降到最低 目前的peocessor SDK 便是针对于我们当前的 a8 a9 a15全系列支持的一个SDK 它把所有目录的解析 所有dts文件的架构和位置 基本上都是使用了同样的框架 这样对于已经开发过a8的兄弟们而言 你网上走a9或者a15还是比较容易的

接下来的章节大家比较感兴趣了

如何用PR实现工业通讯总线协议

首先我想跟大家探讨一下

大家可以想一想

工业通讯总线协议为什么不容易做

或者说为什么用EtherCAT去做

刚才提到几点 扩展性好 应该不算是对于技术上的难点

吞吐量大 可以说我有一个 百兆网甚至是千兆网的载体

是不是就OK了

其实我们可以看一下 Ethercat这边的定义

有助于我们去理解工业通讯协议

去实现这个工业通讯协议中 你会遇到什么样的跳战

这样就能理解TI 的架构 为什么能满足你的设定需求

Ethercat目前在中国市场 铺的还是非常开的

Ethercat主站 我们直接看到下面

implementation这块

主站这方面的实现 往往是存储转发机制

很简单 就是我的每个数据包过来 相当于说每个CPU都会处理的

但是对于从站这个地方 大家看到了没有

它叫on-the-fly的processing

很简单 就是我是 free to capture

给大家一个简单的例子

我们有一个msater带六个节点

那我的Ethercat往往是由 总线或者是环型结构去做的

我们想一个总线结构

第一个master接着第二个的

一个master接着第一个slave接着 第二个slave接第三第四第五第六

每一个slave之间都是手拉手 一进一出的结构

大家可以看system level view

比如说我们最左上角的 就是第一个

紧接着第二个 第三个 第四个

我最后一个节点的 收到我master侧的数据时延

是由前面三个的slave节点的 时延的总和决定的

所以它是一个叠加的过程

这个叠加的过程带来一个什么问题

就是我的slave这边的时延必须要很快

必须要很小

如果我slave节点口比较大

那会有个什么情况

如果每个slave节点相对来说不可控

抖动比较大 就是我们说jitter

或者是抖动比较大的话

那我环路想要做到 比如说一毫秒同周期

我能带的节点就比较少了

因为我在算每个节点时延的时候 我都会每个节点时延中

最消耗资源或者抖动最差的情况 我才能保证环路的稳定

所以 Ethercat的slave节点这块

重要的特点就是我必须要 on the fly的去capture我的数据

这样我才能保证我的节点时延比较小

所以,对slave的 实质性要求是比较高的

对于master它是不会再说

像我们平常看一个 CPU去处理一个数据包

数据包过来了 我就解析

比如说ethernet

ethercat net 我去比对

这些东西的mac地址和 我自己的IP地址这些东西

是不是我的 如果不是我的我再转发走

其实对于EtherCAT而言的话

它是没有办法去忍受这个时延的

它必须要on the fly动态的 去做一个capture

去做所谓的数据端的切片

数据端切片过后 我再去做所谓的数据处理

去拿到自己的 数据过后我再去做处理

然后在下一个同步轴器之中再去丢掉

再丢回去

所以对master侧的这一块来说

master侧的这一块其实有一个压力

就是我要保证在一个同步周期内

把我底下这些数据的处理

就是要去处理掉的信息及时处理掉

如果我只是简单做一个数据收集

那我master侧对于 CPU的性能就没有这么高

但倘若我master侧这块是 类似于做运动控制器的

那我要去规划 调整我 下面节点的运动控制轨迹

这时候master侧的对于arm

的运算能力以及对dsp的使用能力 就可能是你关注的一个焦点

而对于slave侧的话 最主要的一点就是

我要非常快的把数据端切片拿下来

一般来说 我们CPU体系之中的接口

我们可以看一下 下一张

一般来说 我们CPU的 外设接口是很难做到的

而pru单独这块体系中 它是怎么去做到这块

这张图能够给大家一个解释

大家可以看到 一般来说 比如说我们就拿gpl口做解释好了

这里有一个gpl口

我们的arm侧 最左侧的是我们的arm核

arm核我想访问这个gpl口 往往是挂在很多总线上

每一条总线上都会有自己的总线带宽

也会有总线仲裁

那我arm想要访问到 一个gpl口的外设状态的话

我是要通过L4 L3

然后再通过各种数据指令集的缓存

最终才能够拿到这个接口

所以这就是为什么外面普通以太网

cpsw 就是我们的普通以太网 很难以实施高效做处理的一个原因

对于pru来说 它有什么差别呢

pru是跟arm相对来说独立的一个体系

这个体系跟arm的位置是等同的

而且它有自己独立的instruction RAM

还有Data RAM

所以它能自己独立的运转

当你把固件这些东西 去load到pru核里后

它能够很快的自己 capture到外面io电频的变换

因为pru这边的io口

与这个不同

这个是挂在总线上的 一级一级进去的

这边是io口 直通寄存器的

pru到io口直通寄存器

代表着什么含义

这里边我们是200兆的pru

我一个指令周期就是五个纳秒

pru的汇编大多数指令 都是单指令周期的运算

也就是说五个纳秒一个周期 往往 我就能capture到外面的变换了

所以,这样子的话 只要外面有数据进来

我的pru能够很迅速的capture到

而且 pru这里面往往 就像是单片机一样

我就是一个从上往下的顺序执行结构

就跟我们原来学习hello world一样

就是一个主man

你一个主man下来过后 是什么样子就是什么样子

所有的逻辑控制

你都可以去按照指令周期去算出来的

所以它的指令执行会非常高效

在pru的这一点上

就保证了它独立的处理暗核 不会 受到外界CPU loading干扰这个特性

所以它能够去做我们 刚才提到的on the fly capture

有人可能问这地方只是io

难道我要把Ethercat作为io去做吗

其实不是大家看 黄色的peripherals就包含了

上页这张图里面的

黄色的里面就包括了

我们这方有mii的接口

这个就是我们的百兆以太网

所以它跟gpl口也是一样的

都是直通到我们pru这侧的

除了mii之外 我们还会有uart

这就是为什么我们还可以去做 类似于periphery bus这些东西的原因

而periphery net Ethercat之类的 都要依赖于我们的mii接口

和pru核

往往是一个pru核做一进 另一个pru核和mii做一出

所以等于是单核单用

基本上我们看到在a8 体系架构中的一个pru子系统中

我们都是两个核

一个pru子系统两个核

这两个核 一个进 一个出

这两个核之间是可以相互发中断的

并且pru拥有对全局的访问权限

当然 在这地方能访问是一回事

但是arm这块要规划好

我不要发生资源冲突

比如说我一直在做一些接口的轮循

pru进来够后 可能会有打架的情况

这个我们在系统 设计层面上是会去避免的

但是从功能上来说 它是有访问全局的

它就可以通过电路dma

去把我的数据实时的 从内部的RAM空间之中

搬到外部的ddr上

它跟arm之间 也可以有一个中断去做访问

给arm一个中断

我的处理机制就可以 变成pru把所有的数据capture完

处理完了过后

丢到我的ddr上

最后给arm一个中断

每一次接到这个中断的时候 对它来讲没有loading

它就把刚才提到的那些复杂的切片

和这些实时的算法 在ddr上的数据

把它这个算法中的数据全都拿到了

直接去处理职业数据就OK了

然后发的话 也是有pru这边

去通过自己独立的ram

去运行 去发的

所以这样一来 pru就能做到 实时 高效的通信

所以 我们回到这张图上来

所以,刚才我提到的这点

就是“pru为什么在这样一个体系 架构之中能够做工业通信的ltave”

作为主站来说 它有没有什么好处呢

大家可以看到 主站我刚刚提到的一点是

主站,并不要求说

你立刻就要去保证节点时延

因为节点时延的保障 是有slave去进行的

那首先我刚才提到了一点

一个就是说CPU的性能

你做算法和处理数据的能力

这是非常重要的

对通信上来讲

它 一般来讲会怎么去做

目前来讲我们看到有两种方式

一种就是在普通的以太网上

通过所谓软的方式 加载一层Ethercat的通信

Ethercat的协议

去完成Ethercat master的功能

还有一个就是用pru去实现

pru实现的好处是什么

刚才我们提到pru的 实时控制性能力非常强

所以在这个地方的话 我们pru可以去做到一个功能

叫Time trick set TTS的这样一个功能

包括后面的Time sensitivity network 这个tsn的一些能力

都是可以在pru这个体系上实现的

如果你把pru换成对外界的io口

就是相当于说挂在 L3 L4上这些东西的能力

那它插的东西就不止一个等级了

一个是总线上带宽通信的仲裁的时间

这个东西被节约掉了

另外的就是指令周期方面的时间

排队时间被节约掉了

单指令周期 L口直通进行器 这是它的特点

这也是为什么它能够成为 工业通信上一个重要应用手段的原因

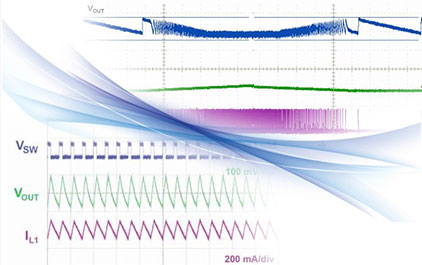

这里给大家一个 重要的叫bench Mark 一个数据对比

大家可以看到 左侧我们用arm的gpio

做了一些测试

我们在一个arm上拉了gpio

这边是直接使用汇编

去写的一个拉高拉低

右边是我们在pru体系上

去用了汇编去写的拉高拉低

事实上 从测试结果看

之间的速度差距可以达到40倍之差

通过这张图 希望大家能够 更加理解住pru它的实时特性

相对来说还是比arm 这边的外设处理器

还是强大了和好几个等级的

所以它能够作比较多的事情

回到我们实现的这个层面上

有人可能问了

如果arm pru这块都是用去汇编写的 我要怎么去hold这个事情

这开发难度对我来说有多大

事实上 TI在这边的话 是把所有的固件和相关应用程序和api都已经写好了

所有第三方的资源都已经囊括在内了

真正对于用户的时候用来说 他只需要使用上层的api就OK

下层的改动会非常小

特别是针对固件这边的改动

基本上大家不太会碰到

如果说一定会碰到的场景是什么样的

TI现在目前为了 很多工业客户去开放的出来的

这个开源性的Ethernet架构

因为现在很多客户想去做

自己自定义的 工业控制通讯协议

比如说我们看看国内 几个大的运动控制器的生产厂商

都有自定义的协议 都是 基于百兆甚至千兆以太网去做的

TI有一套开源的 基于pru的协议框架

这个(听不清)

也是release在了官网上

大家感兴趣的话 可以同过pru的关键字眼去搜索

能够找到这个东西

这里面能够把pru内部的汇编

包括整个汇编工程

拉出来给到大家

大家可以在汇编工程上去做修改

它是直接把连接的建立到连接的协商

到很多内部连接数据 交换机制之类的都给规划出来了

你是可以直接跳进去 改里面汇编的机制的

改汇编对于有些朋友来说会比较陌生

这个其实在TI这边来讲 首先提供了两种方式

一种是汇编 一种是C语言

因为C语言我们已经实现了 在pru上有一个pru的编译器

可以把你的C语言转成汇编 这样对于很多初级和终极玩家来说

会比较容易上手

汇编主要的一个好处就是

在处理这种复杂的通讯协议的时候

你的实时性可以 精确到每一个指令周期

这个对于很多朋友 老鸟来说

这个还是比较重要的

很多人在这个基础上

去做二次开发的时候

会需要很多的资料

这种资料我们已经把它收集到 我们当前的pru的Tools complier上了

大家可以在我们的 Wiki上去搜一下prucomplier

和pru的汇编

我们用(听不清) 编译的那套体系和流程

这个讲说的非常明白

其实总的汇编 指令大概也就是二三十条

总的来说不是很困难

上手给大家一点信心

就是在TI这边 之前带实习生

就是有来做毕设的

我们曾经有一个毕设的学生 做一个pru camera的一个应用

大概是用了两个多月

在我们资深FAE的带领下

他就独立完成了对于pru 实现摄像头的一个功能

所以这个东西的实现并没有 大家想象的这么困难

感兴趣的话大家可以会后去看一看

在我看目前TI的方案之中

我们回到这一点上

pru的特性刚才跟大家介绍过了

它实现工业通讯协议的优势

其实从整体成本上来说

这个为大家节省的还是比较多的

我们知道ASICs跟FPGAs现在的 价格相对来说是比较昂贵的

基本上在TI的arm+pru架构中

我们推出了amic110的产品

以及am335系列的产品

就是想在这个市场上 给大家带来一个福利

基本上能够做到整体的 BOM成本节约大概20%—30%

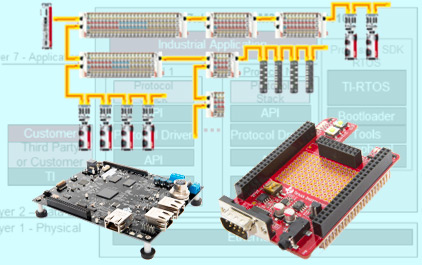

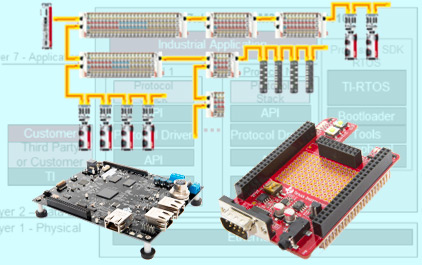

在右边的产品构架上

我们在不同的应用领域内

我们可以有不同的玩法

比如说刚才提到的motion control

如果是motion control+ 带有Ethercat master的

就可以选择用 arm+dsp+pru这种完善的体系

我们am57系列就可以做到这些事情

如果说你响应的 只是简单的逻辑控制器

或者是带有小motion功能的plc

那又要有Ethercat

那我们的an335系列的 产品就可以满足需求

如果你说其实 我想要做的是一个兼容性的平台

我的工业通讯协议可能在 我以后的路标设备之中

现在我只是想预留这样一个可能性

我现在想做的 只是一些中低端的 比如说

做一些can 485 一些很平常的这种通讯方式的

那一样 我们的纯arm核的产品

也是比较适合发展

也是比较适应大家选择的

因为我们的arm+pru+dsp这套架构

往往设计的理念都是PIN 2 PIN结合

特别是在我们amic110这代产品之中

它基本上是把a8整个芯片 做到了PIN2 PIN的兼容

所以不管是面对 高端的应用还是中低端的应用

都是比较合适的

这张就是我们am335x的系统框图

am335x这种框图之中

点几个重点去讲

大家可能会关心到的 一个是a8的主频

a8的主频的话 这边有300 600 800 1G

当然了 如果你做所谓工业通信的时候

肯定是不需要lcd的

但是对于下面经常被问到的can通信

spi通信 UR的通信 pru这些东西肯定是必备的

然后这些东西会不会有

以太网通信会不会有

这些东西都是可配选项

所以amic110也是在这个市场上 应运而生出来的新的产品

它基本上就是把刚才我们提到的

因为你pru这块 已经能做工业通信控制了

那么我们的a8其实本身的工业通信 能力在外设的基础上并没有这么强

这就是为什么之前 单ASIC去做的功能全在这儿了

我们配了一个a8的300兆的mpu

关于3D加速器 lcd显示这一块全都被除掉了

包括之前的一些音频接口

包括之前的一些pw

不好意思 这个是EtherCap和千兆以太网

千兆以太网这边可能就不太需要了

所以定制化 出来了一个amic110的产品

amic110的产品的话相对来说

对于335的性价比就会高很多

除此之外的话

如果说我们还需要更高端一点的

比如刚才提到的带有 运动控制器的motion control

然后可能是arm+dsp+pru架构的

那就是am57x系列

然后plc逻辑控制器这块

我们可以用335 可以用437 可以用57

这个差异点也是在于说 你有没有复杂的联动算法

你有没有工业通讯的需求

所以 在这一套体系架构中

通过sitara系列的产品能为 大家带来相应的设计价值

能让大家使用一个规划的平台

去完善整个系统解决方案

大家知道 其实在工业上面

去验证一个平台的稳定性 往往是 需要花费两年 三年甚至更多时间

这种时间的积累对 各位研发来说也是一笔财富

所以如果能够通过 同样一套体系架构让你玩转整套产品

这个对开发来说的价值是不言而喻的

那TI在立足于这一点

除了在我们当前的 a8 a9 a15的芯片每一代之间

就是每一代产品系列之间

做到了PIN2 PIN

在跨代 比如说a8升a9 a9升a15 包括 后面我们升到a53的体系架构之中

我们也考虑了软件的兼容性这一点

希望大家把软件开发的门槛降到最低

目前的peocessor SDK 便是针对于我们当前的

a8 a9 a15全系列支持的一个SDK

它把所有目录的解析

所有dts文件的架构和位置

基本上都是使用了同样的框架

这样对于已经开发过a8的兄弟们而言

你网上走a9或者a15还是比较容易的

接下来的章节大家比较感兴趣了 如何用PR实现工业通讯总线协议 首先我想跟大家探讨一下 大家可以想一想 工业通讯总线协议为什么不容易做 或者说为什么用EtherCAT去做 刚才提到几点 扩展性好 应该不算是对于技术上的难点 吞吐量大 可以说我有一个 百兆网甚至是千兆网的载体 是不是就OK了 其实我们可以看一下 Ethercat这边的定义 有助于我们去理解工业通讯协议 去实现这个工业通讯协议中 你会遇到什么样的跳战 这样就能理解TI 的架构 为什么能满足你的设定需求 Ethercat目前在中国市场 铺的还是非常开的 Ethercat主站 我们直接看到下面 implementation这块 主站这方面的实现 往往是存储转发机制 很简单 就是我的每个数据包过来 相当于说每个CPU都会处理的 但是对于从站这个地方 大家看到了没有 它叫on-the-fly的processing 很简单 就是我是 free to capture 给大家一个简单的例子 我们有一个msater带六个节点 那我的Ethercat往往是由 总线或者是环型结构去做的 我们想一个总线结构 第一个master接着第二个的 一个master接着第一个slave接着 第二个slave接第三第四第五第六 每一个slave之间都是手拉手 一进一出的结构 大家可以看system level view 比如说我们最左上角的 就是第一个 紧接着第二个 第三个 第四个 我最后一个节点的 收到我master侧的数据时延 是由前面三个的slave节点的 时延的总和决定的 所以它是一个叠加的过程 这个叠加的过程带来一个什么问题 就是我的slave这边的时延必须要很快 必须要很小 如果我slave节点口比较大 那会有个什么情况 如果每个slave节点相对来说不可控 抖动比较大 就是我们说jitter 或者是抖动比较大的话 那我环路想要做到 比如说一毫秒同周期 我能带的节点就比较少了 因为我在算每个节点时延的时候 我都会每个节点时延中 最消耗资源或者抖动最差的情况 我才能保证环路的稳定 所以 Ethercat的slave节点这块 重要的特点就是我必须要 on the fly的去capture我的数据 这样我才能保证我的节点时延比较小 所以,对slave的 实质性要求是比较高的 对于master它是不会再说 像我们平常看一个 CPU去处理一个数据包 数据包过来了 我就解析 比如说ethernet ethercat net 我去比对 这些东西的mac地址和 我自己的IP地址这些东西 是不是我的 如果不是我的我再转发走 其实对于EtherCAT而言的话 它是没有办法去忍受这个时延的 它必须要on the fly动态的 去做一个capture 去做所谓的数据端的切片 数据端切片过后 我再去做所谓的数据处理 去拿到自己的 数据过后我再去做处理 然后在下一个同步轴器之中再去丢掉 再丢回去 所以对master侧的这一块来说 master侧的这一块其实有一个压力 就是我要保证在一个同步周期内 把我底下这些数据的处理 就是要去处理掉的信息及时处理掉 如果我只是简单做一个数据收集 那我master侧对于 CPU的性能就没有这么高 但倘若我master侧这块是 类似于做运动控制器的 那我要去规划 调整我 下面节点的运动控制轨迹 这时候master侧的对于arm 的运算能力以及对dsp的使用能力 就可能是你关注的一个焦点 而对于slave侧的话 最主要的一点就是 我要非常快的把数据端切片拿下来 一般来说 我们CPU体系之中的接口 我们可以看一下 下一张 一般来说 我们CPU的 外设接口是很难做到的 而pru单独这块体系中 它是怎么去做到这块 这张图能够给大家一个解释 大家可以看到 一般来说 比如说我们就拿gpl口做解释好了 这里有一个gpl口 我们的arm侧 最左侧的是我们的arm核 arm核我想访问这个gpl口 往往是挂在很多总线上 每一条总线上都会有自己的总线带宽 也会有总线仲裁 那我arm想要访问到 一个gpl口的外设状态的话 我是要通过L4 L3 然后再通过各种数据指令集的缓存 最终才能够拿到这个接口 所以这就是为什么外面普通以太网 cpsw 就是我们的普通以太网 很难以实施高效做处理的一个原因 对于pru来说 它有什么差别呢 pru是跟arm相对来说独立的一个体系 这个体系跟arm的位置是等同的 而且它有自己独立的instruction RAM 还有Data RAM 所以它能自己独立的运转 当你把固件这些东西 去load到pru核里后 它能够很快的自己 capture到外面io电频的变换 因为pru这边的io口 与这个不同 这个是挂在总线上的 一级一级进去的 这边是io口 直通寄存器的 pru到io口直通寄存器 代表着什么含义 这里边我们是200兆的pru 我一个指令周期就是五个纳秒 pru的汇编大多数指令 都是单指令周期的运算 也就是说五个纳秒一个周期 往往 我就能capture到外面的变换了 所以,这样子的话 只要外面有数据进来 我的pru能够很迅速的capture到 而且 pru这里面往往 就像是单片机一样 我就是一个从上往下的顺序执行结构 就跟我们原来学习hello world一样 就是一个主man 你一个主man下来过后 是什么样子就是什么样子 所有的逻辑控制 你都可以去按照指令周期去算出来的 所以它的指令执行会非常高效 在pru的这一点上 就保证了它独立的处理暗核 不会 受到外界CPU loading干扰这个特性 所以它能够去做我们 刚才提到的on the fly capture 有人可能问这地方只是io 难道我要把Ethercat作为io去做吗 其实不是大家看 黄色的peripherals就包含了 上页这张图里面的 黄色的里面就包括了 我们这方有mii的接口 这个就是我们的百兆以太网 所以它跟gpl口也是一样的 都是直通到我们pru这侧的 除了mii之外 我们还会有uart 这就是为什么我们还可以去做 类似于periphery bus这些东西的原因 而periphery net Ethercat之类的 都要依赖于我们的mii接口 和pru核 往往是一个pru核做一进 另一个pru核和mii做一出 所以等于是单核单用 基本上我们看到在a8 体系架构中的一个pru子系统中 我们都是两个核 一个pru子系统两个核 这两个核 一个进 一个出 这两个核之间是可以相互发中断的 并且pru拥有对全局的访问权限 当然 在这地方能访问是一回事 但是arm这块要规划好 我不要发生资源冲突 比如说我一直在做一些接口的轮循 pru进来够后 可能会有打架的情况 这个我们在系统 设计层面上是会去避免的 但是从功能上来说 它是有访问全局的 它就可以通过电路dma 去把我的数据实时的 从内部的RAM空间之中 搬到外部的ddr上 它跟arm之间 也可以有一个中断去做访问 给arm一个中断 我的处理机制就可以 变成pru把所有的数据capture完 处理完了过后 丢到我的ddr上 最后给arm一个中断 每一次接到这个中断的时候 对它来讲没有loading 它就把刚才提到的那些复杂的切片 和这些实时的算法 在ddr上的数据 把它这个算法中的数据全都拿到了 直接去处理职业数据就OK了 然后发的话 也是有pru这边 去通过自己独立的ram 去运行 去发的 所以这样一来 pru就能做到 实时 高效的通信 所以 我们回到这张图上来 所以,刚才我提到的这点 就是“pru为什么在这样一个体系 架构之中能够做工业通信的ltave” 作为主站来说 它有没有什么好处呢 大家可以看到 主站我刚刚提到的一点是 主站,并不要求说 你立刻就要去保证节点时延 因为节点时延的保障 是有slave去进行的 那首先我刚才提到了一点 一个就是说CPU的性能 你做算法和处理数据的能力 这是非常重要的 对通信上来讲 它 一般来讲会怎么去做 目前来讲我们看到有两种方式 一种就是在普通的以太网上 通过所谓软的方式 加载一层Ethercat的通信 Ethercat的协议 去完成Ethercat master的功能 还有一个就是用pru去实现 pru实现的好处是什么 刚才我们提到pru的 实时控制性能力非常强 所以在这个地方的话 我们pru可以去做到一个功能 叫Time trick set TTS的这样一个功能 包括后面的Time sensitivity network 这个tsn的一些能力 都是可以在pru这个体系上实现的 如果你把pru换成对外界的io口 就是相当于说挂在 L3 L4上这些东西的能力 那它插的东西就不止一个等级了 一个是总线上带宽通信的仲裁的时间 这个东西被节约掉了 另外的就是指令周期方面的时间 排队时间被节约掉了 单指令周期 L口直通进行器 这是它的特点 这也是为什么它能够成为 工业通信上一个重要应用手段的原因 这里给大家一个 重要的叫bench Mark 一个数据对比 大家可以看到 左侧我们用arm的gpio 做了一些测试 我们在一个arm上拉了gpio 这边是直接使用汇编 去写的一个拉高拉低 右边是我们在pru体系上 去用了汇编去写的拉高拉低 事实上 从测试结果看 之间的速度差距可以达到40倍之差 通过这张图 希望大家能够 更加理解住pru它的实时特性 相对来说还是比arm 这边的外设处理器 还是强大了和好几个等级的 所以它能够作比较多的事情 回到我们实现的这个层面上 有人可能问了 如果arm pru这块都是用去汇编写的 我要怎么去hold这个事情 这开发难度对我来说有多大 事实上 TI在这边的话 是把所有的固件和相关应用程序和api都已经写好了 所有第三方的资源都已经囊括在内了 真正对于用户的时候用来说 他只需要使用上层的api就OK 下层的改动会非常小 特别是针对固件这边的改动 基本上大家不太会碰到 如果说一定会碰到的场景是什么样的 TI现在目前为了 很多工业客户去开放的出来的 这个开源性的Ethernet架构 因为现在很多客户想去做 自己自定义的 工业控制通讯协议 比如说我们看看国内 几个大的运动控制器的生产厂商 都有自定义的协议 都是 基于百兆甚至千兆以太网去做的 TI有一套开源的 基于pru的协议框架 这个(听不清) 也是release在了官网上 大家感兴趣的话 可以同过pru的关键字眼去搜索 能够找到这个东西 这里面能够把pru内部的汇编 包括整个汇编工程 拉出来给到大家 大家可以在汇编工程上去做修改 它是直接把连接的建立到连接的协商 到很多内部连接数据 交换机制之类的都给规划出来了 你是可以直接跳进去 改里面汇编的机制的 改汇编对于有些朋友来说会比较陌生 这个其实在TI这边来讲 首先提供了两种方式 一种是汇编 一种是C语言 因为C语言我们已经实现了 在pru上有一个pru的编译器 可以把你的C语言转成汇编 这样对于很多初级和终极玩家来说 会比较容易上手 汇编主要的一个好处就是 在处理这种复杂的通讯协议的时候 你的实时性可以 精确到每一个指令周期 这个对于很多朋友 老鸟来说 这个还是比较重要的 很多人在这个基础上 去做二次开发的时候 会需要很多的资料 这种资料我们已经把它收集到 我们当前的pru的Tools complier上了 大家可以在我们的 Wiki上去搜一下prucomplier 和pru的汇编 我们用(听不清) 编译的那套体系和流程 这个讲说的非常明白 其实总的汇编 指令大概也就是二三十条 总的来说不是很困难 上手给大家一点信心 就是在TI这边 之前带实习生 就是有来做毕设的 我们曾经有一个毕设的学生 做一个pru camera的一个应用 大概是用了两个多月 在我们资深FAE的带领下 他就独立完成了对于pru 实现摄像头的一个功能 所以这个东西的实现并没有 大家想象的这么困难 感兴趣的话大家可以会后去看一看 在我看目前TI的方案之中 我们回到这一点上 pru的特性刚才跟大家介绍过了 它实现工业通讯协议的优势 其实从整体成本上来说 这个为大家节省的还是比较多的 我们知道ASICs跟FPGAs现在的 价格相对来说是比较昂贵的 基本上在TI的arm+pru架构中 我们推出了amic110的产品 以及am335系列的产品 就是想在这个市场上 给大家带来一个福利 基本上能够做到整体的 BOM成本节约大概20%—30% 在右边的产品构架上 我们在不同的应用领域内 我们可以有不同的玩法 比如说刚才提到的motion control 如果是motion control+ 带有Ethercat master的 就可以选择用 arm+dsp+pru这种完善的体系 我们am57系列就可以做到这些事情 如果说你响应的 只是简单的逻辑控制器 或者是带有小motion功能的plc 那又要有Ethercat 那我们的an335系列的 产品就可以满足需求 如果你说其实 我想要做的是一个兼容性的平台 我的工业通讯协议可能在 我以后的路标设备之中 现在我只是想预留这样一个可能性 我现在想做的 只是一些中低端的 比如说 做一些can 485 一些很平常的这种通讯方式的 那一样 我们的纯arm核的产品 也是比较适合发展 也是比较适应大家选择的 因为我们的arm+pru+dsp这套架构 往往设计的理念都是PIN 2 PIN结合 特别是在我们amic110这代产品之中 它基本上是把a8整个芯片 做到了PIN2 PIN的兼容 所以不管是面对 高端的应用还是中低端的应用 都是比较合适的 这张就是我们am335x的系统框图 am335x这种框图之中 点几个重点去讲 大家可能会关心到的 一个是a8的主频 a8的主频的话 这边有300 600 800 1G 当然了 如果你做所谓工业通信的时候 肯定是不需要lcd的 但是对于下面经常被问到的can通信 spi通信 UR的通信 pru这些东西肯定是必备的 然后这些东西会不会有 以太网通信会不会有 这些东西都是可配选项 所以amic110也是在这个市场上 应运而生出来的新的产品 它基本上就是把刚才我们提到的 因为你pru这块 已经能做工业通信控制了 那么我们的a8其实本身的工业通信 能力在外设的基础上并没有这么强 这就是为什么之前 单ASIC去做的功能全在这儿了 我们配了一个a8的300兆的mpu 关于3D加速器 lcd显示这一块全都被除掉了 包括之前的一些音频接口 包括之前的一些pw 不好意思 这个是EtherCap和千兆以太网 千兆以太网这边可能就不太需要了 所以定制化 出来了一个amic110的产品 amic110的产品的话相对来说 对于335的性价比就会高很多 除此之外的话 如果说我们还需要更高端一点的 比如刚才提到的带有 运动控制器的motion control 然后可能是arm+dsp+pru架构的 那就是am57x系列 然后plc逻辑控制器这块 我们可以用335 可以用437 可以用57 这个差异点也是在于说 你有没有复杂的联动算法 你有没有工业通讯的需求 所以 在这一套体系架构中 通过sitara系列的产品能为 大家带来相应的设计价值 能让大家使用一个规划的平台 去完善整个系统解决方案 大家知道 其实在工业上面 去验证一个平台的稳定性 往往是 需要花费两年 三年甚至更多时间 这种时间的积累对 各位研发来说也是一笔财富 所以如果能够通过 同样一套体系架构让你玩转整套产品 这个对开发来说的价值是不言而喻的 那TI在立足于这一点 除了在我们当前的 a8 a9 a15的芯片每一代之间 就是每一代产品系列之间 做到了PIN2 PIN 在跨代 比如说a8升a9 a9升a15 包括 后面我们升到a53的体系架构之中 我们也考虑了软件的兼容性这一点 希望大家把软件开发的门槛降到最低 目前的peocessor SDK 便是针对于我们当前的 a8 a9 a15全系列支持的一个SDK 它把所有目录的解析 所有dts文件的架构和位置 基本上都是使用了同样的框架 这样对于已经开发过a8的兄弟们而言 你网上走a9或者a15还是比较容易的

接下来的章节大家比较感兴趣了

如何用PR实现工业通讯总线协议

首先我想跟大家探讨一下

大家可以想一想

工业通讯总线协议为什么不容易做

或者说为什么用EtherCAT去做

刚才提到几点 扩展性好 应该不算是对于技术上的难点

吞吐量大 可以说我有一个 百兆网甚至是千兆网的载体

是不是就OK了

其实我们可以看一下 Ethercat这边的定义

有助于我们去理解工业通讯协议

去实现这个工业通讯协议中 你会遇到什么样的跳战

这样就能理解TI 的架构 为什么能满足你的设定需求

Ethercat目前在中国市场 铺的还是非常开的

Ethercat主站 我们直接看到下面

implementation这块

主站这方面的实现 往往是存储转发机制

很简单 就是我的每个数据包过来 相当于说每个CPU都会处理的

但是对于从站这个地方 大家看到了没有

它叫on-the-fly的processing

很简单 就是我是 free to capture

给大家一个简单的例子

我们有一个msater带六个节点

那我的Ethercat往往是由 总线或者是环型结构去做的

我们想一个总线结构

第一个master接着第二个的

一个master接着第一个slave接着 第二个slave接第三第四第五第六

每一个slave之间都是手拉手 一进一出的结构

大家可以看system level view

比如说我们最左上角的 就是第一个

紧接着第二个 第三个 第四个

我最后一个节点的 收到我master侧的数据时延

是由前面三个的slave节点的 时延的总和决定的

所以它是一个叠加的过程

这个叠加的过程带来一个什么问题

就是我的slave这边的时延必须要很快

必须要很小

如果我slave节点口比较大

那会有个什么情况

如果每个slave节点相对来说不可控

抖动比较大 就是我们说jitter

或者是抖动比较大的话

那我环路想要做到 比如说一毫秒同周期

我能带的节点就比较少了

因为我在算每个节点时延的时候 我都会每个节点时延中

最消耗资源或者抖动最差的情况 我才能保证环路的稳定

所以 Ethercat的slave节点这块

重要的特点就是我必须要 on the fly的去capture我的数据

这样我才能保证我的节点时延比较小

所以,对slave的 实质性要求是比较高的

对于master它是不会再说

像我们平常看一个 CPU去处理一个数据包

数据包过来了 我就解析

比如说ethernet

ethercat net 我去比对

这些东西的mac地址和 我自己的IP地址这些东西

是不是我的 如果不是我的我再转发走

其实对于EtherCAT而言的话

它是没有办法去忍受这个时延的

它必须要on the fly动态的 去做一个capture

去做所谓的数据端的切片

数据端切片过后 我再去做所谓的数据处理

去拿到自己的 数据过后我再去做处理

然后在下一个同步轴器之中再去丢掉

再丢回去

所以对master侧的这一块来说

master侧的这一块其实有一个压力

就是我要保证在一个同步周期内

把我底下这些数据的处理

就是要去处理掉的信息及时处理掉

如果我只是简单做一个数据收集

那我master侧对于 CPU的性能就没有这么高

但倘若我master侧这块是 类似于做运动控制器的

那我要去规划 调整我 下面节点的运动控制轨迹

这时候master侧的对于arm

的运算能力以及对dsp的使用能力 就可能是你关注的一个焦点

而对于slave侧的话 最主要的一点就是

我要非常快的把数据端切片拿下来

一般来说 我们CPU体系之中的接口

我们可以看一下 下一张

一般来说 我们CPU的 外设接口是很难做到的

而pru单独这块体系中 它是怎么去做到这块

这张图能够给大家一个解释

大家可以看到 一般来说 比如说我们就拿gpl口做解释好了

这里有一个gpl口

我们的arm侧 最左侧的是我们的arm核

arm核我想访问这个gpl口 往往是挂在很多总线上

每一条总线上都会有自己的总线带宽

也会有总线仲裁

那我arm想要访问到 一个gpl口的外设状态的话

我是要通过L4 L3

然后再通过各种数据指令集的缓存

最终才能够拿到这个接口

所以这就是为什么外面普通以太网

cpsw 就是我们的普通以太网 很难以实施高效做处理的一个原因

对于pru来说 它有什么差别呢

pru是跟arm相对来说独立的一个体系

这个体系跟arm的位置是等同的

而且它有自己独立的instruction RAM

还有Data RAM

所以它能自己独立的运转

当你把固件这些东西 去load到pru核里后

它能够很快的自己 capture到外面io电频的变换

因为pru这边的io口

与这个不同

这个是挂在总线上的 一级一级进去的

这边是io口 直通寄存器的

pru到io口直通寄存器

代表着什么含义

这里边我们是200兆的pru

我一个指令周期就是五个纳秒

pru的汇编大多数指令 都是单指令周期的运算

也就是说五个纳秒一个周期 往往 我就能capture到外面的变换了

所以,这样子的话 只要外面有数据进来

我的pru能够很迅速的capture到

而且 pru这里面往往 就像是单片机一样

我就是一个从上往下的顺序执行结构

就跟我们原来学习hello world一样

就是一个主man

你一个主man下来过后 是什么样子就是什么样子

所有的逻辑控制

你都可以去按照指令周期去算出来的

所以它的指令执行会非常高效

在pru的这一点上

就保证了它独立的处理暗核 不会 受到外界CPU loading干扰这个特性

所以它能够去做我们 刚才提到的on the fly capture

有人可能问这地方只是io

难道我要把Ethercat作为io去做吗

其实不是大家看 黄色的peripherals就包含了

上页这张图里面的

黄色的里面就包括了

我们这方有mii的接口

这个就是我们的百兆以太网

所以它跟gpl口也是一样的

都是直通到我们pru这侧的

除了mii之外 我们还会有uart

这就是为什么我们还可以去做 类似于periphery bus这些东西的原因

而periphery net Ethercat之类的 都要依赖于我们的mii接口

和pru核

往往是一个pru核做一进 另一个pru核和mii做一出

所以等于是单核单用

基本上我们看到在a8 体系架构中的一个pru子系统中

我们都是两个核

一个pru子系统两个核

这两个核 一个进 一个出

这两个核之间是可以相互发中断的

并且pru拥有对全局的访问权限

当然 在这地方能访问是一回事

但是arm这块要规划好

我不要发生资源冲突

比如说我一直在做一些接口的轮循

pru进来够后 可能会有打架的情况

这个我们在系统 设计层面上是会去避免的

但是从功能上来说 它是有访问全局的

它就可以通过电路dma

去把我的数据实时的 从内部的RAM空间之中

搬到外部的ddr上

它跟arm之间 也可以有一个中断去做访问

给arm一个中断

我的处理机制就可以 变成pru把所有的数据capture完

处理完了过后

丢到我的ddr上

最后给arm一个中断

每一次接到这个中断的时候 对它来讲没有loading

它就把刚才提到的那些复杂的切片

和这些实时的算法 在ddr上的数据

把它这个算法中的数据全都拿到了

直接去处理职业数据就OK了

然后发的话 也是有pru这边

去通过自己独立的ram

去运行 去发的

所以这样一来 pru就能做到 实时 高效的通信

所以 我们回到这张图上来

所以,刚才我提到的这点

就是“pru为什么在这样一个体系 架构之中能够做工业通信的ltave”

作为主站来说 它有没有什么好处呢

大家可以看到 主站我刚刚提到的一点是

主站,并不要求说

你立刻就要去保证节点时延

因为节点时延的保障 是有slave去进行的

那首先我刚才提到了一点

一个就是说CPU的性能

你做算法和处理数据的能力

这是非常重要的

对通信上来讲

它 一般来讲会怎么去做

目前来讲我们看到有两种方式

一种就是在普通的以太网上

通过所谓软的方式 加载一层Ethercat的通信

Ethercat的协议

去完成Ethercat master的功能

还有一个就是用pru去实现

pru实现的好处是什么

刚才我们提到pru的 实时控制性能力非常强

所以在这个地方的话 我们pru可以去做到一个功能

叫Time trick set TTS的这样一个功能

包括后面的Time sensitivity network 这个tsn的一些能力

都是可以在pru这个体系上实现的

如果你把pru换成对外界的io口

就是相当于说挂在 L3 L4上这些东西的能力

那它插的东西就不止一个等级了

一个是总线上带宽通信的仲裁的时间

这个东西被节约掉了

另外的就是指令周期方面的时间

排队时间被节约掉了

单指令周期 L口直通进行器 这是它的特点

这也是为什么它能够成为 工业通信上一个重要应用手段的原因

这里给大家一个 重要的叫bench Mark 一个数据对比

大家可以看到 左侧我们用arm的gpio

做了一些测试

我们在一个arm上拉了gpio

这边是直接使用汇编

去写的一个拉高拉低

右边是我们在pru体系上

去用了汇编去写的拉高拉低

事实上 从测试结果看

之间的速度差距可以达到40倍之差

通过这张图 希望大家能够 更加理解住pru它的实时特性

相对来说还是比arm 这边的外设处理器

还是强大了和好几个等级的

所以它能够作比较多的事情

回到我们实现的这个层面上

有人可能问了

如果arm pru这块都是用去汇编写的 我要怎么去hold这个事情

这开发难度对我来说有多大

事实上 TI在这边的话 是把所有的固件和相关应用程序和api都已经写好了

所有第三方的资源都已经囊括在内了

真正对于用户的时候用来说 他只需要使用上层的api就OK

下层的改动会非常小

特别是针对固件这边的改动

基本上大家不太会碰到

如果说一定会碰到的场景是什么样的

TI现在目前为了 很多工业客户去开放的出来的

这个开源性的Ethernet架构

因为现在很多客户想去做

自己自定义的 工业控制通讯协议

比如说我们看看国内 几个大的运动控制器的生产厂商

都有自定义的协议 都是 基于百兆甚至千兆以太网去做的

TI有一套开源的 基于pru的协议框架

这个(听不清)

也是release在了官网上

大家感兴趣的话 可以同过pru的关键字眼去搜索

能够找到这个东西

这里面能够把pru内部的汇编

包括整个汇编工程

拉出来给到大家

大家可以在汇编工程上去做修改

它是直接把连接的建立到连接的协商

到很多内部连接数据 交换机制之类的都给规划出来了

你是可以直接跳进去 改里面汇编的机制的

改汇编对于有些朋友来说会比较陌生

这个其实在TI这边来讲 首先提供了两种方式

一种是汇编 一种是C语言

因为C语言我们已经实现了 在pru上有一个pru的编译器

可以把你的C语言转成汇编 这样对于很多初级和终极玩家来说

会比较容易上手

汇编主要的一个好处就是

在处理这种复杂的通讯协议的时候

你的实时性可以 精确到每一个指令周期

这个对于很多朋友 老鸟来说

这个还是比较重要的

很多人在这个基础上

去做二次开发的时候

会需要很多的资料

这种资料我们已经把它收集到 我们当前的pru的Tools complier上了

大家可以在我们的 Wiki上去搜一下prucomplier

和pru的汇编

我们用(听不清) 编译的那套体系和流程

这个讲说的非常明白

其实总的汇编 指令大概也就是二三十条

总的来说不是很困难

上手给大家一点信心

就是在TI这边 之前带实习生

就是有来做毕设的

我们曾经有一个毕设的学生 做一个pru camera的一个应用

大概是用了两个多月

在我们资深FAE的带领下

他就独立完成了对于pru 实现摄像头的一个功能

所以这个东西的实现并没有 大家想象的这么困难

感兴趣的话大家可以会后去看一看

在我看目前TI的方案之中

我们回到这一点上

pru的特性刚才跟大家介绍过了

它实现工业通讯协议的优势

其实从整体成本上来说

这个为大家节省的还是比较多的

我们知道ASICs跟FPGAs现在的 价格相对来说是比较昂贵的

基本上在TI的arm+pru架构中

我们推出了amic110的产品

以及am335系列的产品

就是想在这个市场上 给大家带来一个福利

基本上能够做到整体的 BOM成本节约大概20%—30%

在右边的产品构架上

我们在不同的应用领域内

我们可以有不同的玩法

比如说刚才提到的motion control

如果是motion control+ 带有Ethercat master的

就可以选择用 arm+dsp+pru这种完善的体系

我们am57系列就可以做到这些事情

如果说你响应的 只是简单的逻辑控制器

或者是带有小motion功能的plc

那又要有Ethercat

那我们的an335系列的 产品就可以满足需求

如果你说其实 我想要做的是一个兼容性的平台

我的工业通讯协议可能在 我以后的路标设备之中

现在我只是想预留这样一个可能性

我现在想做的 只是一些中低端的 比如说

做一些can 485 一些很平常的这种通讯方式的

那一样 我们的纯arm核的产品

也是比较适合发展

也是比较适应大家选择的

因为我们的arm+pru+dsp这套架构

往往设计的理念都是PIN 2 PIN结合

特别是在我们amic110这代产品之中

它基本上是把a8整个芯片 做到了PIN2 PIN的兼容

所以不管是面对 高端的应用还是中低端的应用

都是比较合适的

这张就是我们am335x的系统框图

am335x这种框图之中

点几个重点去讲

大家可能会关心到的 一个是a8的主频

a8的主频的话 这边有300 600 800 1G

当然了 如果你做所谓工业通信的时候

肯定是不需要lcd的

但是对于下面经常被问到的can通信

spi通信 UR的通信 pru这些东西肯定是必备的

然后这些东西会不会有

以太网通信会不会有

这些东西都是可配选项

所以amic110也是在这个市场上 应运而生出来的新的产品

它基本上就是把刚才我们提到的

因为你pru这块 已经能做工业通信控制了

那么我们的a8其实本身的工业通信 能力在外设的基础上并没有这么强

这就是为什么之前 单ASIC去做的功能全在这儿了

我们配了一个a8的300兆的mpu

关于3D加速器 lcd显示这一块全都被除掉了

包括之前的一些音频接口

包括之前的一些pw

不好意思 这个是EtherCap和千兆以太网

千兆以太网这边可能就不太需要了

所以定制化 出来了一个amic110的产品

amic110的产品的话相对来说

对于335的性价比就会高很多

除此之外的话

如果说我们还需要更高端一点的

比如刚才提到的带有 运动控制器的motion control

然后可能是arm+dsp+pru架构的

那就是am57x系列

然后plc逻辑控制器这块

我们可以用335 可以用437 可以用57

这个差异点也是在于说 你有没有复杂的联动算法

你有没有工业通讯的需求

所以 在这一套体系架构中

通过sitara系列的产品能为 大家带来相应的设计价值

能让大家使用一个规划的平台

去完善整个系统解决方案

大家知道 其实在工业上面

去验证一个平台的稳定性 往往是 需要花费两年 三年甚至更多时间

这种时间的积累对 各位研发来说也是一笔财富

所以如果能够通过 同样一套体系架构让你玩转整套产品

这个对开发来说的价值是不言而喻的

那TI在立足于这一点

除了在我们当前的 a8 a9 a15的芯片每一代之间

就是每一代产品系列之间

做到了PIN2 PIN

在跨代 比如说a8升a9 a9升a15 包括 后面我们升到a53的体系架构之中

我们也考虑了软件的兼容性这一点

希望大家把软件开发的门槛降到最低

目前的peocessor SDK 便是针对于我们当前的

a8 a9 a15全系列支持的一个SDK

它把所有目录的解析

所有dts文件的架构和位置

基本上都是使用了同样的框架

这样对于已经开发过a8的兄弟们而言

你网上走a9或者a15还是比较容易的

手机看

扫码用手机观看

视频简介

视频简介

基于AMIC产品的工业通信总线设计方案-1.2 PRU Implement Industrial Communication

所属课程: TI - 基于 AMIC 产品的工业通信总线设计方案

发布时间:2018.05.28

视频集数:6

本节视频时长:00:22:10

随着工业通信的不断发展,各种通信协议百花齐放,各类驱动器、控制器产品支持 EtherCAT, ProfiNET 的趋势也越发明显。本次直播通过对 TI Sitara 的工业通信方案及产品的介绍,通过实例演示让大家了解TI方案的实现原理及优势。

未学习 基于AMIC产品的工业通信总线设计方案-1.2 PRU Implement Industrial Communication

未学习 基于AMIC产品的工业通信总线设计方案-1.2 PRU Implement Industrial Communication

未学习 基于AMIC产品的工业通信总线设计方案-1.3 Industrial Slave Protocols

未学习 基于AMIC产品的工业通信总线设计方案-1.3 Industrial Slave Protocols

未学习 基于AMIC产品的工业通信总线设计方案-1.4 EtherCAT Master

未学习 基于AMIC产品的工业通信总线设计方案-1.4 EtherCAT Master

未学习 基于AMIC产品的工业通信总线设计方案-1.5 TI Devices

未学习 基于AMIC产品的工业通信总线设计方案-1.5 TI Devices

未学习 基于AMIC产品的工业通信总线设计方案-1.6 TI Sitara Product Overview

未学习 基于AMIC产品的工业通信总线设计方案-1.6 TI Sitara Product Overview

未学习 基于AMIC产品的工业通信总线设计方案-1.1 Industrial Communication

未学习 基于AMIC产品的工业通信总线设计方案-1.1 Industrial Communication