1.1 F28004x功能和性能介绍

Loading the player...

将在30s后自动为您播放下一课程

大家好 我是张万凌 目前主要负责 C2000 微控制器产品 在电机控制和数字电源等工业控制领域的推广和支持 本次培训我们将通过介绍最新产品系列 F28004x 来展示 C2000 微控制器在实时控制系统中的新特性 F28004x 是最新的 Piccolo 系列产品 它实现了模拟、控制和通信的更高性能集成 使得不同应用的设计都可以在系统层面减少外围器件 降低系统成本,提高产品效率 因此也可以作为 F2803x 和 F2806x 的完美升级和替代 本次培训会以三个典型应用 电机控制、数字电源和工业驱动应用 为例来说明它的一些新特性 本课程针对的是有一定 C2000 应用背景的 数字处理器和系统应用相关的工程师 因此可以说是一个中级培训教程 今天的主题大致包括 F28004x 的整体介绍 和三个典型用例相关重要新特性的增强说明 首先看一下 F28004x 总的资源列表和差异化的新特性总括 处理器层面 支持 100M 的 C28x 主 CPU 和相同处理能力的 CLA 协处理器 支持硬件 32 位浮点三角运算和除法运算的 TMU 内存部分 提供 256K 带 ECC 功能的闪存 Flash 和 100K 带奇偶校验功能的 SRAM 外设角度 片上集成主要分三个部分 第一,模拟接口 包括三个独立的 3.5M 采样速度的 12 位精度 ADC 模块 两个 12 位精度的 DAC 输出模块 七个可编程运放 PGA 和七个窗口比较器 CMPSS 各自带两个 12 位精度的 DAC 用于高低比较阈值的设定 第二,数字控制接口 包括 8 对共 16 路 Type4 ePWM 输出通道 全部支持高精度 150 个 ps 输出 两个 eQEP 模块 七个 Capture 模块和四路 Sigma Delta 数字采样滤波接口 第三,通信接口 包括三个 UART 模块 两个 SPI 模块 两个 CAN 模块 一个 I2C 模块 一个 PMBus 模块和一个 FSI 快速串行通讯接口 系统来看 片上集成 VREG 和 DCDC 用于产生 1.2V 内核电源 优化 JTAG 调试接口为 cJTAG 系统功耗降低至 F2806x 的一半以下 集成 instaSPIN FOC 和 instaSPIN Motion 算法 提供 56-Pin QFN,64-Pin LQFP 和 100-Pin LQFP 3 个封装 同时支持汽车级 接下来是整个芯片的系统框图 独立的 C28x 主 CPU 和 CLA 控制内核 C28x、CLA 和 DMA 3 条独立的数据连接总线 可以操作 Flash 闪存和 SRAM 以及各个模拟、数字控制和通信接口 具体的内核、内存和外设的改进和升级 首先是 Type 2 CLA 内核 在 F2837x 和 F2807x Type 1 CLA 的基础上 使能了后台任务的支持和两个硬件断点的支持 用户可以配置 Task 8 作为传统的最低优先级中断任务 或者是后台任务 由外设或软件进行触发 Task 1 到 7 都可以打断它优先执行 如果有需要 也可以将 Task 8 的部分代码设置为不可打断 MDEBUGSTOP1 指令作为 MDEBUGSTOP 的升级 可以用作软件断点 直接冲掉流水线 在执行到语句时直接读取结果 而硬件断点跟 C28x 一样 可以在 CCS 里直接操作用于仿真 CPU/CLA 和 DMA 的访问权限 相比于 F2837x 和 07x 只能在初始化时提前设定 DMA 或 CLA 之一访问外设 F28004x 支持两者在有仲裁机制的前提下同时访问 实现了 CLA 可以直接读取 DMA 搬运结果的功能 大大提高了访问效率 节省了 CPU 的带宽 内存的改进在于将 256K 闪存分成了两个 bank 有各自独立的泵提供电源 可以支持在运行应用程序的同时 实现应用程序的代码现场在线升级 同时增加的 ECC 功能 可以实现一位数据错误检测和纠正 或者两位数据错误检测 另外专门的硬件状态机替代 CPU 指令执行 来确保烧入时序 可以节省 CPU 带宽 用于应用程序执行和中断的响应 外设部分 ADC 模块增加了 PPB 后端处理单元 可以对采样时序和采样结果进行处理 包括采样延时检测 单通道零偏较准 抬升幅度加减和高低阈值比较等 后者还可以直接产生中断和事件 用于应用程序的处理和经过 X-bar 传输送至 ePWM 模块进行 TRIP 的硬件保护 比较器单元 CMPSS 升级至 Type 1 在 2803x 只能对单侧信号进行比较的基础上 增加了高低阈值双路比较 同样支持经过 X-bar 将比较结果 传输送至 ePWM 模块进行 TRIP 的硬件保护 而且可以选择直接传输或者进行数字滤波后传输 相比于 F2837x 和 F2807x CMPSS 可以在 EPI 模块技术边界点进行事件的清除和复位 确保在有必要的情况下下 一个周期仍然能够检测有效沿口 进行下一轮动作 同时也支持正负两端信号单独选择和设置 解决了 F2837x 和 F2807x 里两者必须同时选择和配置的尴尬 可缓冲的 DAC 数模转换输出单元同样升级至 Type 1 在 F2837x 和 F2807x 的基础上 去掉了输出端的下拉电阻 增加了一倍和两倍的增益选择 用于支持内部 DAC 参考选择 2.5V 或者 3.3V 同时也增强了负载能力 最后在可编程运放 PGA 部分 是在 F2805x 的基础上改进升级至 Type 1 增加了 24x 的增益选择 同时支持输出端低通滤波 只需要根据截止频率在外部增加电容 内部计算机选择对应的匹配电阻即可 在使能输出端低通滤波功能的情况下 运放可以通过不同通道选择 输出滤波或无滤波信号至 ADC 和 CMPSS 模块 而在不使能输出端低通滤波功能的情况下 输出滤波引脚也可以作为普通的 ADC 或者 CMPSS 引脚 同时如果 PGA 模块未使用即被 bypass 它的输入通道也可以直接到 ADC 或 CMPSS 引脚

大家好 我是张万凌 目前主要负责 C2000 微控制器产品 在电机控制和数字电源等工业控制领域的推广和支持 本次培训我们将通过介绍最新产品系列 F28004x 来展示 C2000 微控制器在实时控制系统中的新特性 F28004x 是最新的 Piccolo 系列产品 它实现了模拟、控制和通信的更高性能集成 使得不同应用的设计都可以在系统层面减少外围器件 降低系统成本,提高产品效率 因此也可以作为 F2803x 和 F2806x 的完美升级和替代 本次培训会以三个典型应用 电机控制、数字电源和工业驱动应用 为例来说明它的一些新特性 本课程针对的是有一定 C2000 应用背景的 数字处理器和系统应用相关的工程师 因此可以说是一个中级培训教程 今天的主题大致包括 F28004x 的整体介绍 和三个典型用例相关重要新特性的增强说明 首先看一下 F28004x 总的资源列表和差异化的新特性总括 处理器层面 支持 100M 的 C28x 主 CPU 和相同处理能力的 CLA 协处理器 支持硬件 32 位浮点三角运算和除法运算的 TMU 内存部分 提供 256K 带 ECC 功能的闪存 Flash 和 100K 带奇偶校验功能的 SRAM 外设角度 片上集成主要分三个部分 第一,模拟接口 包括三个独立的 3.5M 采样速度的 12 位精度 ADC 模块 两个 12 位精度的 DAC 输出模块 七个可编程运放 PGA 和七个窗口比较器 CMPSS 各自带两个 12 位精度的 DAC 用于高低比较阈值的设定 第二,数字控制接口 包括 8 对共 16 路 Type4 ePWM 输出通道 全部支持高精度 150 个 ps 输出 两个 eQEP 模块 七个 Capture 模块和四路 Sigma Delta 数字采样滤波接口 第三,通信接口 包括三个 UART 模块 两个 SPI 模块 两个 CAN 模块 一个 I2C 模块 一个 PMBus 模块和一个 FSI 快速串行通讯接口 系统来看 片上集成 VREG 和 DCDC 用于产生 1.2V 内核电源 优化 JTAG 调试接口为 cJTAG 系统功耗降低至 F2806x 的一半以下 集成 instaSPIN FOC 和 instaSPIN Motion 算法 提供 56-Pin QFN,64-Pin LQFP 和 100-Pin LQFP 3 个封装 同时支持汽车级 接下来是整个芯片的系统框图 独立的 C28x 主 CPU 和 CLA 控制内核 C28x、CLA 和 DMA 3 条独立的数据连接总线 可以操作 Flash 闪存和 SRAM 以及各个模拟、数字控制和通信接口 具体的内核、内存和外设的改进和升级 首先是 Type 2 CLA 内核 在 F2837x 和 F2807x Type 1 CLA 的基础上 使能了后台任务的支持和两个硬件断点的支持 用户可以配置 Task 8 作为传统的最低优先级中断任务 或者是后台任务 由外设或软件进行触发 Task 1 到 7 都可以打断它优先执行 如果有需要 也可以将 Task 8 的部分代码设置为不可打断 MDEBUGSTOP1 指令作为 MDEBUGSTOP 的升级 可以用作软件断点 直接冲掉流水线 在执行到语句时直接读取结果 而硬件断点跟 C28x 一样 可以在 CCS 里直接操作用于仿真 CPU/CLA 和 DMA 的访问权限 相比于 F2837x 和 07x 只能在初始化时提前设定 DMA 或 CLA 之一访问外设 F28004x 支持两者在有仲裁机制的前提下同时访问 实现了 CLA 可以直接读取 DMA 搬运结果的功能 大大提高了访问效率 节省了 CPU 的带宽 内存的改进在于将 256K 闪存分成了两个 bank 有各自独立的泵提供电源 可以支持在运行应用程序的同时 实现应用程序的代码现场在线升级 同时增加的 ECC 功能 可以实现一位数据错误检测和纠正 或者两位数据错误检测 另外专门的硬件状态机替代 CPU 指令执行 来确保烧入时序 可以节省 CPU 带宽 用于应用程序执行和中断的响应 外设部分 ADC 模块增加了 PPB 后端处理单元 可以对采样时序和采样结果进行处理 包括采样延时检测 单通道零偏较准 抬升幅度加减和高低阈值比较等 后者还可以直接产生中断和事件 用于应用程序的处理和经过 X-bar 传输送至 ePWM 模块进行 TRIP 的硬件保护 比较器单元 CMPSS 升级至 Type 1 在 2803x 只能对单侧信号进行比较的基础上 增加了高低阈值双路比较 同样支持经过 X-bar 将比较结果 传输送至 ePWM 模块进行 TRIP 的硬件保护 而且可以选择直接传输或者进行数字滤波后传输 相比于 F2837x 和 F2807x CMPSS 可以在 EPI 模块技术边界点进行事件的清除和复位 确保在有必要的情况下下 一个周期仍然能够检测有效沿口 进行下一轮动作 同时也支持正负两端信号单独选择和设置 解决了 F2837x 和 F2807x 里两者必须同时选择和配置的尴尬 可缓冲的 DAC 数模转换输出单元同样升级至 Type 1 在 F2837x 和 F2807x 的基础上 去掉了输出端的下拉电阻 增加了一倍和两倍的增益选择 用于支持内部 DAC 参考选择 2.5V 或者 3.3V 同时也增强了负载能力 最后在可编程运放 PGA 部分 是在 F2805x 的基础上改进升级至 Type 1 增加了 24x 的增益选择 同时支持输出端低通滤波 只需要根据截止频率在外部增加电容 内部计算机选择对应的匹配电阻即可 在使能输出端低通滤波功能的情况下 运放可以通过不同通道选择 输出滤波或无滤波信号至 ADC 和 CMPSS 模块 而在不使能输出端低通滤波功能的情况下 输出滤波引脚也可以作为普通的 ADC 或者 CMPSS 引脚 同时如果 PGA 模块未使用即被 bypass 它的输入通道也可以直接到 ADC 或 CMPSS 引脚

大家好

我是张万凌

目前主要负责 C2000 微控制器产品

在电机控制和数字电源等工业控制领域的推广和支持

本次培训我们将通过介绍最新产品系列 F28004x

来展示 C2000 微控制器在实时控制系统中的新特性

F28004x 是最新的 Piccolo 系列产品

它实现了模拟、控制和通信的更高性能集成

使得不同应用的设计都可以在系统层面减少外围器件

降低系统成本,提高产品效率

因此也可以作为 F2803x 和 F2806x 的完美升级和替代

本次培训会以三个典型应用

电机控制、数字电源和工业驱动应用

为例来说明它的一些新特性

本课程针对的是有一定 C2000 应用背景的

数字处理器和系统应用相关的工程师

因此可以说是一个中级培训教程

今天的主题大致包括 F28004x 的整体介绍

和三个典型用例相关重要新特性的增强说明

首先看一下 F28004x 总的资源列表和差异化的新特性总括

处理器层面

支持 100M 的 C28x 主 CPU

和相同处理能力的 CLA 协处理器

支持硬件 32 位浮点三角运算和除法运算的 TMU

内存部分

提供 256K 带 ECC 功能的闪存 Flash

和 100K 带奇偶校验功能的 SRAM

外设角度

片上集成主要分三个部分

第一,模拟接口

包括三个独立的 3.5M 采样速度的 12 位精度 ADC 模块

两个 12 位精度的 DAC 输出模块

七个可编程运放 PGA 和七个窗口比较器 CMPSS

各自带两个 12 位精度的 DAC 用于高低比较阈值的设定

第二,数字控制接口

包括 8 对共 16 路 Type4 ePWM 输出通道

全部支持高精度 150 个 ps 输出

两个 eQEP 模块

七个 Capture 模块和四路 Sigma Delta 数字采样滤波接口

第三,通信接口

包括三个 UART 模块

两个 SPI 模块

两个 CAN 模块

一个 I2C 模块

一个 PMBus 模块和一个 FSI 快速串行通讯接口

系统来看

片上集成 VREG 和 DCDC 用于产生 1.2V 内核电源

优化 JTAG 调试接口为 cJTAG

系统功耗降低至 F2806x 的一半以下

集成 instaSPIN FOC 和 instaSPIN Motion 算法

提供 56-Pin QFN,64-Pin LQFP 和 100-Pin LQFP 3 个封装

同时支持汽车级

接下来是整个芯片的系统框图

独立的 C28x 主 CPU 和 CLA 控制内核

C28x、CLA 和 DMA 3 条独立的数据连接总线

可以操作 Flash 闪存和 SRAM

以及各个模拟、数字控制和通信接口

具体的内核、内存和外设的改进和升级

首先是 Type 2 CLA 内核

在 F2837x 和 F2807x Type 1 CLA 的基础上

使能了后台任务的支持和两个硬件断点的支持

用户可以配置 Task 8 作为传统的最低优先级中断任务

或者是后台任务

由外设或软件进行触发

Task 1 到 7 都可以打断它优先执行

如果有需要

也可以将 Task 8 的部分代码设置为不可打断

MDEBUGSTOP1 指令作为 MDEBUGSTOP 的升级

可以用作软件断点

直接冲掉流水线

在执行到语句时直接读取结果

而硬件断点跟 C28x 一样

可以在 CCS 里直接操作用于仿真

CPU/CLA 和 DMA 的访问权限

相比于 F2837x 和 07x

只能在初始化时提前设定 DMA 或 CLA 之一访问外设

F28004x 支持两者在有仲裁机制的前提下同时访问

实现了 CLA 可以直接读取 DMA 搬运结果的功能

大大提高了访问效率

节省了 CPU 的带宽

内存的改进在于将 256K 闪存分成了两个 bank

有各自独立的泵提供电源

可以支持在运行应用程序的同时

实现应用程序的代码现场在线升级

同时增加的 ECC 功能

可以实现一位数据错误检测和纠正

或者两位数据错误检测

另外专门的硬件状态机替代 CPU 指令执行

来确保烧入时序

可以节省 CPU 带宽

用于应用程序执行和中断的响应

外设部分

ADC 模块增加了 PPB 后端处理单元

可以对采样时序和采样结果进行处理

包括采样延时检测

单通道零偏较准

抬升幅度加减和高低阈值比较等

后者还可以直接产生中断和事件

用于应用程序的处理和经过 X-bar

传输送至 ePWM 模块进行 TRIP 的硬件保护

比较器单元 CMPSS 升级至 Type 1

在 2803x 只能对单侧信号进行比较的基础上

增加了高低阈值双路比较

同样支持经过 X-bar 将比较结果

传输送至 ePWM 模块进行 TRIP 的硬件保护

而且可以选择直接传输或者进行数字滤波后传输

相比于 F2837x 和 F2807x

CMPSS 可以在 EPI 模块技术边界点进行事件的清除和复位

确保在有必要的情况下下

一个周期仍然能够检测有效沿口

进行下一轮动作

同时也支持正负两端信号单独选择和设置

解决了 F2837x 和 F2807x 里两者必须同时选择和配置的尴尬

可缓冲的 DAC 数模转换输出单元同样升级至 Type 1

在 F2837x 和 F2807x 的基础上

去掉了输出端的下拉电阻

增加了一倍和两倍的增益选择

用于支持内部 DAC 参考选择 2.5V 或者 3.3V

同时也增强了负载能力

最后在可编程运放 PGA 部分

是在 F2805x 的基础上改进升级至 Type 1

增加了 24x 的增益选择

同时支持输出端低通滤波

只需要根据截止频率在外部增加电容

内部计算机选择对应的匹配电阻即可

在使能输出端低通滤波功能的情况下

运放可以通过不同通道选择

输出滤波或无滤波信号至 ADC 和 CMPSS 模块

而在不使能输出端低通滤波功能的情况下

输出滤波引脚也可以作为普通的 ADC 或者 CMPSS 引脚

同时如果 PGA 模块未使用即被 bypass

它的输入通道也可以直接到 ADC 或 CMPSS 引脚

大家好 我是张万凌 目前主要负责 C2000 微控制器产品 在电机控制和数字电源等工业控制领域的推广和支持 本次培训我们将通过介绍最新产品系列 F28004x 来展示 C2000 微控制器在实时控制系统中的新特性 F28004x 是最新的 Piccolo 系列产品 它实现了模拟、控制和通信的更高性能集成 使得不同应用的设计都可以在系统层面减少外围器件 降低系统成本,提高产品效率 因此也可以作为 F2803x 和 F2806x 的完美升级和替代 本次培训会以三个典型应用 电机控制、数字电源和工业驱动应用 为例来说明它的一些新特性 本课程针对的是有一定 C2000 应用背景的 数字处理器和系统应用相关的工程师 因此可以说是一个中级培训教程 今天的主题大致包括 F28004x 的整体介绍 和三个典型用例相关重要新特性的增强说明 首先看一下 F28004x 总的资源列表和差异化的新特性总括 处理器层面 支持 100M 的 C28x 主 CPU 和相同处理能力的 CLA 协处理器 支持硬件 32 位浮点三角运算和除法运算的 TMU 内存部分 提供 256K 带 ECC 功能的闪存 Flash 和 100K 带奇偶校验功能的 SRAM 外设角度 片上集成主要分三个部分 第一,模拟接口 包括三个独立的 3.5M 采样速度的 12 位精度 ADC 模块 两个 12 位精度的 DAC 输出模块 七个可编程运放 PGA 和七个窗口比较器 CMPSS 各自带两个 12 位精度的 DAC 用于高低比较阈值的设定 第二,数字控制接口 包括 8 对共 16 路 Type4 ePWM 输出通道 全部支持高精度 150 个 ps 输出 两个 eQEP 模块 七个 Capture 模块和四路 Sigma Delta 数字采样滤波接口 第三,通信接口 包括三个 UART 模块 两个 SPI 模块 两个 CAN 模块 一个 I2C 模块 一个 PMBus 模块和一个 FSI 快速串行通讯接口 系统来看 片上集成 VREG 和 DCDC 用于产生 1.2V 内核电源 优化 JTAG 调试接口为 cJTAG 系统功耗降低至 F2806x 的一半以下 集成 instaSPIN FOC 和 instaSPIN Motion 算法 提供 56-Pin QFN,64-Pin LQFP 和 100-Pin LQFP 3 个封装 同时支持汽车级 接下来是整个芯片的系统框图 独立的 C28x 主 CPU 和 CLA 控制内核 C28x、CLA 和 DMA 3 条独立的数据连接总线 可以操作 Flash 闪存和 SRAM 以及各个模拟、数字控制和通信接口 具体的内核、内存和外设的改进和升级 首先是 Type 2 CLA 内核 在 F2837x 和 F2807x Type 1 CLA 的基础上 使能了后台任务的支持和两个硬件断点的支持 用户可以配置 Task 8 作为传统的最低优先级中断任务 或者是后台任务 由外设或软件进行触发 Task 1 到 7 都可以打断它优先执行 如果有需要 也可以将 Task 8 的部分代码设置为不可打断 MDEBUGSTOP1 指令作为 MDEBUGSTOP 的升级 可以用作软件断点 直接冲掉流水线 在执行到语句时直接读取结果 而硬件断点跟 C28x 一样 可以在 CCS 里直接操作用于仿真 CPU/CLA 和 DMA 的访问权限 相比于 F2837x 和 07x 只能在初始化时提前设定 DMA 或 CLA 之一访问外设 F28004x 支持两者在有仲裁机制的前提下同时访问 实现了 CLA 可以直接读取 DMA 搬运结果的功能 大大提高了访问效率 节省了 CPU 的带宽 内存的改进在于将 256K 闪存分成了两个 bank 有各自独立的泵提供电源 可以支持在运行应用程序的同时 实现应用程序的代码现场在线升级 同时增加的 ECC 功能 可以实现一位数据错误检测和纠正 或者两位数据错误检测 另外专门的硬件状态机替代 CPU 指令执行 来确保烧入时序 可以节省 CPU 带宽 用于应用程序执行和中断的响应 外设部分 ADC 模块增加了 PPB 后端处理单元 可以对采样时序和采样结果进行处理 包括采样延时检测 单通道零偏较准 抬升幅度加减和高低阈值比较等 后者还可以直接产生中断和事件 用于应用程序的处理和经过 X-bar 传输送至 ePWM 模块进行 TRIP 的硬件保护 比较器单元 CMPSS 升级至 Type 1 在 2803x 只能对单侧信号进行比较的基础上 增加了高低阈值双路比较 同样支持经过 X-bar 将比较结果 传输送至 ePWM 模块进行 TRIP 的硬件保护 而且可以选择直接传输或者进行数字滤波后传输 相比于 F2837x 和 F2807x CMPSS 可以在 EPI 模块技术边界点进行事件的清除和复位 确保在有必要的情况下下 一个周期仍然能够检测有效沿口 进行下一轮动作 同时也支持正负两端信号单独选择和设置 解决了 F2837x 和 F2807x 里两者必须同时选择和配置的尴尬 可缓冲的 DAC 数模转换输出单元同样升级至 Type 1 在 F2837x 和 F2807x 的基础上 去掉了输出端的下拉电阻 增加了一倍和两倍的增益选择 用于支持内部 DAC 参考选择 2.5V 或者 3.3V 同时也增强了负载能力 最后在可编程运放 PGA 部分 是在 F2805x 的基础上改进升级至 Type 1 增加了 24x 的增益选择 同时支持输出端低通滤波 只需要根据截止频率在外部增加电容 内部计算机选择对应的匹配电阻即可 在使能输出端低通滤波功能的情况下 运放可以通过不同通道选择 输出滤波或无滤波信号至 ADC 和 CMPSS 模块 而在不使能输出端低通滤波功能的情况下 输出滤波引脚也可以作为普通的 ADC 或者 CMPSS 引脚 同时如果 PGA 模块未使用即被 bypass 它的输入通道也可以直接到 ADC 或 CMPSS 引脚

大家好

我是张万凌

目前主要负责 C2000 微控制器产品

在电机控制和数字电源等工业控制领域的推广和支持

本次培训我们将通过介绍最新产品系列 F28004x

来展示 C2000 微控制器在实时控制系统中的新特性

F28004x 是最新的 Piccolo 系列产品

它实现了模拟、控制和通信的更高性能集成

使得不同应用的设计都可以在系统层面减少外围器件

降低系统成本,提高产品效率

因此也可以作为 F2803x 和 F2806x 的完美升级和替代

本次培训会以三个典型应用

电机控制、数字电源和工业驱动应用

为例来说明它的一些新特性

本课程针对的是有一定 C2000 应用背景的

数字处理器和系统应用相关的工程师

因此可以说是一个中级培训教程

今天的主题大致包括 F28004x 的整体介绍

和三个典型用例相关重要新特性的增强说明

首先看一下 F28004x 总的资源列表和差异化的新特性总括

处理器层面

支持 100M 的 C28x 主 CPU

和相同处理能力的 CLA 协处理器

支持硬件 32 位浮点三角运算和除法运算的 TMU

内存部分

提供 256K 带 ECC 功能的闪存 Flash

和 100K 带奇偶校验功能的 SRAM

外设角度

片上集成主要分三个部分

第一,模拟接口

包括三个独立的 3.5M 采样速度的 12 位精度 ADC 模块

两个 12 位精度的 DAC 输出模块

七个可编程运放 PGA 和七个窗口比较器 CMPSS

各自带两个 12 位精度的 DAC 用于高低比较阈值的设定

第二,数字控制接口

包括 8 对共 16 路 Type4 ePWM 输出通道

全部支持高精度 150 个 ps 输出

两个 eQEP 模块

七个 Capture 模块和四路 Sigma Delta 数字采样滤波接口

第三,通信接口

包括三个 UART 模块

两个 SPI 模块

两个 CAN 模块

一个 I2C 模块

一个 PMBus 模块和一个 FSI 快速串行通讯接口

系统来看

片上集成 VREG 和 DCDC 用于产生 1.2V 内核电源

优化 JTAG 调试接口为 cJTAG

系统功耗降低至 F2806x 的一半以下

集成 instaSPIN FOC 和 instaSPIN Motion 算法

提供 56-Pin QFN,64-Pin LQFP 和 100-Pin LQFP 3 个封装

同时支持汽车级

接下来是整个芯片的系统框图

独立的 C28x 主 CPU 和 CLA 控制内核

C28x、CLA 和 DMA 3 条独立的数据连接总线

可以操作 Flash 闪存和 SRAM

以及各个模拟、数字控制和通信接口

具体的内核、内存和外设的改进和升级

首先是 Type 2 CLA 内核

在 F2837x 和 F2807x Type 1 CLA 的基础上

使能了后台任务的支持和两个硬件断点的支持

用户可以配置 Task 8 作为传统的最低优先级中断任务

或者是后台任务

由外设或软件进行触发

Task 1 到 7 都可以打断它优先执行

如果有需要

也可以将 Task 8 的部分代码设置为不可打断

MDEBUGSTOP1 指令作为 MDEBUGSTOP 的升级

可以用作软件断点

直接冲掉流水线

在执行到语句时直接读取结果

而硬件断点跟 C28x 一样

可以在 CCS 里直接操作用于仿真

CPU/CLA 和 DMA 的访问权限

相比于 F2837x 和 07x

只能在初始化时提前设定 DMA 或 CLA 之一访问外设

F28004x 支持两者在有仲裁机制的前提下同时访问

实现了 CLA 可以直接读取 DMA 搬运结果的功能

大大提高了访问效率

节省了 CPU 的带宽

内存的改进在于将 256K 闪存分成了两个 bank

有各自独立的泵提供电源

可以支持在运行应用程序的同时

实现应用程序的代码现场在线升级

同时增加的 ECC 功能

可以实现一位数据错误检测和纠正

或者两位数据错误检测

另外专门的硬件状态机替代 CPU 指令执行

来确保烧入时序

可以节省 CPU 带宽

用于应用程序执行和中断的响应

外设部分

ADC 模块增加了 PPB 后端处理单元

可以对采样时序和采样结果进行处理

包括采样延时检测

单通道零偏较准

抬升幅度加减和高低阈值比较等

后者还可以直接产生中断和事件

用于应用程序的处理和经过 X-bar

传输送至 ePWM 模块进行 TRIP 的硬件保护

比较器单元 CMPSS 升级至 Type 1

在 2803x 只能对单侧信号进行比较的基础上

增加了高低阈值双路比较

同样支持经过 X-bar 将比较结果

传输送至 ePWM 模块进行 TRIP 的硬件保护

而且可以选择直接传输或者进行数字滤波后传输

相比于 F2837x 和 F2807x

CMPSS 可以在 EPI 模块技术边界点进行事件的清除和复位

确保在有必要的情况下下

一个周期仍然能够检测有效沿口

进行下一轮动作

同时也支持正负两端信号单独选择和设置

解决了 F2837x 和 F2807x 里两者必须同时选择和配置的尴尬

可缓冲的 DAC 数模转换输出单元同样升级至 Type 1

在 F2837x 和 F2807x 的基础上

去掉了输出端的下拉电阻

增加了一倍和两倍的增益选择

用于支持内部 DAC 参考选择 2.5V 或者 3.3V

同时也增强了负载能力

最后在可编程运放 PGA 部分

是在 F2805x 的基础上改进升级至 Type 1

增加了 24x 的增益选择

同时支持输出端低通滤波

只需要根据截止频率在外部增加电容

内部计算机选择对应的匹配电阻即可

在使能输出端低通滤波功能的情况下

运放可以通过不同通道选择

输出滤波或无滤波信号至 ADC 和 CMPSS 模块

而在不使能输出端低通滤波功能的情况下

输出滤波引脚也可以作为普通的 ADC 或者 CMPSS 引脚

同时如果 PGA 模块未使用即被 bypass

它的输入通道也可以直接到 ADC 或 CMPSS 引脚

手机看

扫码用手机观看

视频简介

视频简介

1.1 F28004x功能和性能介绍

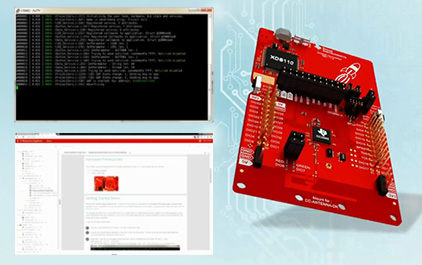

所属课程:TI C2000 F28004x 在实时控制系统中的新特性

发布时间:2017.08.24

视频集数:2

本节视频时长:00:08:40

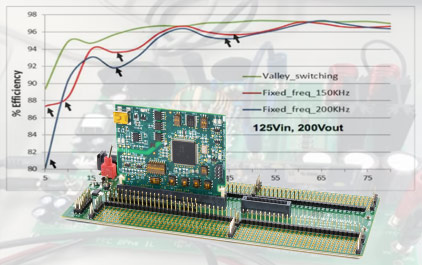

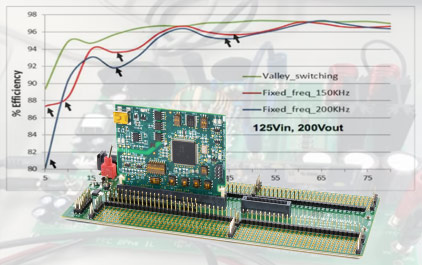

实时控制系统是存在于各种模拟和嵌入元件中复杂实时控制问题的复合解决方案。通过集成各种高性能模块(包括模拟、控制和通信外设),C2000已为多种系统解决方案设计出F28004x Potenza系列,以帮助减少组件总量(降低硬件成本)或提高系统核心功能的执行效率。

本课程将概述如何在根据以下应用的每一外设目标子集设计基于F28004x的系统解决方案的过程中向客户说明价值定位:2个电机+ PFC(3个PGA/电机和1个PFC)、DC/DC和AC/DC数字电源、双相交错返驰和单相返驰微型太阳能逆变器和高速连接驱动器(突出显示FSI通信)。

未学习 1.1 F28004x功能和性能介绍

未学习 1.1 F28004x功能和性能介绍

未学习 1.2 F28004x在多种应用中的优势

未学习 1.2 F28004x在多种应用中的优势