Sigma Delta ADC 工作原理介绍

Loading the player...

将在30s后自动为您播放下一课程

大家好 欢迎大家参加TI工业研讨会 我是TI Century FAE Igor An 主要负责数字电源以及 相关算法的开发 今天我给大家介绍TI在电压电流采样中的相关采样技术 主要是利用不同类型的ADC 对电压电流进行采样 这一章节我们介绍Delta Sigma ADC 的采样基本原理 和具体的实现方式 首先 为什么要引入 delta sigma ADC 采样 之前我们了解到SAR ADC 其实在大部分的工业应用中已经 能够比较好的满足 我们对于ADC的要求 那我们为什么还要考虑引入新的技术 去进一步提升我们的ADC的性能指标 那下面我们要介绍的这个概念其实还是一个比较重要的原因 那就是我们的quantization noise 就是我们的量化噪声 那大家看这个图中的斜线 代表的是我们的模拟信号 我们连续的模拟信号 当我将SAR ADC或者其他ADC把它离散化的时候 我得到一个台阶性的信号 那如果我将原始的模拟信号和得到的台阶性的信号相减的话 我们永远会得到这样的一个锯齿波的形式 那这个Q的大小 +1/2Q -1/2Q Q的大小其实就是我们的量化值 我如果采样的频率越快 那我两个Q之间的间距越小 那我两个Q之间的浮值就越小 我得到的这个锯齿波的正负的浮值就越低 相当于我量化噪声的浮值就会越低 当然我们看 整个包围的面积 不管高和低 浮值变低了 但密度变密了 那整个的乘积包围的面积是不变的 我们可以理解为不管量化的频率如何变化 那可以改变浮值 但不能改变造成的能量 或总量是不会变的 那这个量化噪声是无论如何都无法完全消除的 对于这个时间轴上看的话 我们得到的这个 采样信号 就是一个一个的锯齿信号 一个台阶 我们可以把这个锯齿变得很细很密 接近于连续但还是有量化噪声存在的 但这种和实际的连续的 模拟信号之间的差距 这个量化的 锯齿就是我们在数字化 或者采样过程中 丢失的信息 就是我们整个采样过程中 所损失的原始信号的信息 那我们来看看这个频谱 量化噪声 在我的量化频率的时候 它的量化浮值是最大的 会有一些底噪 那我们通过一些信噪比的计算 可以得到 一个固定的公式 就是量化信息的 信噪比系数 signal noise ration 信噪比就是 6.02N+1.76 N代表的是我们离散或者数字采样 到底有多少位 12位就等于12 我用16位 N就等于16 那如果我把N提高 就是我的 AD采样变数变大的话 信噪比是变大的 也就是 说我采样的质量是变好的 就是信噪比系数更高 噪声更低 所以我提高我的AD采样位数 是对我改善我的采样质量 起码在 消除量化噪声方面是有利的 那我们进一步去看 我在数字离散的时候 会有一个Nyquist 频率 或者我们之前比较熟悉的也叫做 香浓频率 就是我们著名的 Nyquist 香浓采样定理 就是说我的浮线 这个红色是我们关心的 这个信号的频率 那为了浮现这个信号 我的采样率至少是这个 信号频率的两倍以上 我才能完整浮现这个信号 那这就是Nyquist采样定理的核心内容 那我们再定义一个FS 就是我们的采样频率 二分之一FS就是一半 然后我们把这些量定义好 那在这个FS采样率采样的情况下 我会有一个噪声平台 这个噪声平台里面 我们这里 主要考虑量化噪声 其他的外界的噪声 我们在这个讨论里暂时不考虑 那我们刚才从上面的信噪比 知道我提高采样的位数 会对我提高 采样有帮助 那其他的 我单纯的 提高采样位数 意味着我用更高成本的ADC采样环节 和芯片 意味着成本的上升 有没有其他办法 在不增加ADC采样位数的情况下 去提高采样的信噪比 下面就是一个理论上的 分析 基于如果我把我的采样率提高 K倍 我的RFs就变成KFS 在这个情况下 可以从分析上看到 整个噪声平台的浮值 从这边这么高 降低了 但相当于是被拉长了拉扁了 所以它的包围面积是不变的 就是说 结合上面一张图看到的和分析到的 就是量化噪声包围的面积 和总量是不变的 无论采样频率的增加减少 所以这里也是一样的 我采样频率增加 整个的噪声总量是不变的 但是 我的噪声浮值降低了 那信噪比 就是我信号的浮值 和噪声的浮值去比 虽然总量没变 但浮值降低了 在我得到原生信号的频率点上它的信噪比就得到了提高和增加 所以这也是一个有效办法 就是进一步提高采样频率 好 下面介绍Delta Sigma的具体实现方式 来解释为何使用它的采样技术 它的采样技术和SAR采样技术相比 优缺点在哪里 帮助大家了解为什么 有这些优缺点 我们首先来看delta sigma的一个典型的采样 首先有个调制环节 delta sigma modulator 这个有点像我们在无线电里面了解到的调制技术 将一个连续的模拟信号经过调制后 变成一个类似PWM的方波信号 频率信号 这个调制很像我们在电源 电机控制里面 发生PWM的方式 这机制相当于我们的 载波和我们高频的调制波 去比较生成一个占空比固定 频率变化的 这么一个频率信号 然后这个信号经过一定的数字滤波 再解调 得到一个数字化的 这个模拟信号的放映 我们看到delta sigma的调制 一般是外挂的独立的调制芯片 这部分 虚线框里面的 数字滤波器加解调这个环节 一般在我们的C2000芯片里面集成 这个就是C2000里面讲的 delta sigma的模块 我们现在很清楚 我们在[听不清]的delta sigma 是数字滤波加解调 并不是完整的 delta sigma采样的整个环节 这里有一个调制环节 必须外挂一个芯片 好 这个有两个 有两个频率 第一个 FS 就是我们的 调制频率 相当于整个调制波的调制频率 FD是我最终解调之后得出的 数据的频率 首先 我们重点看看modulator 调制器是如何工作的 在对一个信号进行delta sigma调制的时候 我们是用下面这个环路 去实现数字化调制 那整个环路的传递函数 我们用下面的两个式子去推导 具体输出等于输入 两个差乘前面两项的积分环节 再加上量化噪声产生的这个点 把DOUT两边解出来 得到的这个式子 量化噪声乘以 这个表达式 相当于一个高滤波器 那输入的模拟的信号通过的相当于一个 低通的滤波器 那这样 我们在[听不清]段 就可以实现 实现的效果类似这样 我们的有效信号 通过一个低通滤波器 我们的量化噪声通过的是一个高通滤波器 我们的量化噪声刚才看到是一个平的平台 那我通过一个高通滤波器 就是在低频段 还是被削弱的 被滤掉的 高频段是会通过去的 所以在高频段会有量化噪声的信息 通过整个调制环节 在低频段 就是我们的有效信息所处段 它的量化噪声被进一步削减 所以通过这个环路后 我们的有效信息所处的频带 它的信噪比 进一步被优化 这就是我们整个的 delta sigma的基本实现原理 是通过比较 最终实现展播这样的信息 那我们调制器的最终输出 其实是这样的波形 里面包含的信息 其实就是我们之前例子中的正旋信息 频率的图形波形就是这样的 在调制器这个环节 对调制器的选择 我们可以选择不同节数的 我们可以选择一节二节三节的 节数越高 浮频特性越好 在低频段 它的衰减就越厉害 在高频段 通过性就越好 但基数越高 我带来的延迟也越大 这是一个权衡 我要更好的 浮频特性 还是 更快的速率响应 这是一个权衡的问题 下面要介绍芯片内部的 数字滤波器加上 解调环节 那数字滤波器呢 其实我们可以用上面调制的浮值特性 我可以用上面调制之后 得到浮频特性 如果我设计一个 数字滤波器是这样的话 那么这个数字滤波器更高频段的信息 类似于低通的数字滤波器 输出掉 那剩下的 就是我有效的数字信息 那我的数字滤波器 它的带宽 浮频特性 我们是可以通过参数和节数来调解的 它的浮频特性是取决于 到底是一节二节还是三节 然后去选择它的截止频率 从而去选择我到底要 多少个频带的信息 通过 把剩下的信息如何滤掉 这是根据我们的应用选择的 但我们知道如果加 这种简单的低通的话 浮频特性上是可以保留有效的信号 但我们在角度特性上 会引入一个相交延迟 这是低通滤波器的一个特点 在这里 如果有相交延迟 相当于是我们的一个缺点 所以我们要想办法解决 如何相交延迟的问题 就是简单的低通滤波器的 相交延迟问题 那我们想 如何实现刚才的浮值特性的特点呢 同时不引入我们 不希望的这种相交延迟 这里有两种大的选择 对数字滤波器来说 第一个 就是我们的sinc filter 我们看这个波形图 把它叫待通滤波器 就是这部分的信号可以通过去 剩下的信号是被衰减掉的 或者就叫陷波滤波器 就是在这些陷下去的点 频点的信号我们把它滤掉 其他频段的信息会通过去 另外一种叫flat passband filter 其中从波形图看 非常类似一个标准的低通滤波器 但是这种呢 我们后面会对比这两种 滤波器 各自的优缺点 对于sync filter来说呢 在半导体里面是性价比更高的 需要的半导体的面积会更少 所消耗的能量更少 延迟会小 因为我们知道 它只对 陷下去的频点的信号进行抑制 其他地方基本上不抑制 更多的这种相交延迟 典型的就是我们的notch filter 典型的公平道滤波器 就是利用50赫兹 60赫兹 对频率非常敏感 比如我们设计一个50赫兹的sync filter或notch filter 如果我通过这个滤波器的信号是51赫兹 那这个滤波效果就会大打折扣 所以它对你设计的陷波的频点 和你的实际信号的频率 要非常一致 才能达到非常好的滤波效果 缺点就是我在这一点上 我把所有点的信号都滤除掉 那其中也可能包含我的有效信息 也是被同样滤除掉了 flat passband呢 我们理解就是一个 标准的低通滤波器 只是它的实现方式是使用非常多节数的FIR LIR滤波器形式来实现这个 波形图的形状 那我们知道 如果你的节数非常高的话 你的延迟也会非常厉害 比如我们这里举例的这个缺点 例子里面 比如我们用50节的FIR实现了 flat passband 那它的延迟就有50个cycle 但如果我用低的节数 比如用10节 5节 那它的波形图的浮频响应就 不会这么理想和完美 低频段就不会是一条直线 可能是一条斜线下来的 它的浮值特性就会受到影响 不是这么理想的低通 那这个图里面 我们就是 更加形象为大家介绍了 让大家看到 这个延迟是如何产生的 那这个最直接的解释就是你有几节 那你就有几个cycle的延迟 因为我们说的节数就是从 就是S的次数 或者就是存储的深度 数字就是它存储的深度 那很容易理解 有几节 就有几个cycle的延迟 那这个就是flat passband 内部的实现原理图 比如我们的这个ADS1672的芯片 它的实现方式就是FIR filter block 有很多节的FIR 实现了最终的波特图 这个芯片需要55个 cycle来settle 去稳定住 但每个cycle会非常短 频率非常快 但仍然需要55个cycle 相对来讲 是会有一定的延迟的 好的 对于delta sigma的 基本实现方式呢 我们先介绍到这里 欢迎大家继续关注后续的章节

大家好 欢迎大家参加TI工业研讨会 我是TI Century FAE Igor An 主要负责数字电源以及 相关算法的开发 今天我给大家介绍TI在电压电流采样中的相关采样技术 主要是利用不同类型的ADC 对电压电流进行采样 这一章节我们介绍Delta Sigma ADC 的采样基本原理 和具体的实现方式 首先 为什么要引入 delta sigma ADC 采样 之前我们了解到SAR ADC 其实在大部分的工业应用中已经 能够比较好的满足 我们对于ADC的要求 那我们为什么还要考虑引入新的技术 去进一步提升我们的ADC的性能指标 那下面我们要介绍的这个概念其实还是一个比较重要的原因 那就是我们的quantization noise 就是我们的量化噪声 那大家看这个图中的斜线 代表的是我们的模拟信号 我们连续的模拟信号 当我将SAR ADC或者其他ADC把它离散化的时候 我得到一个台阶性的信号 那如果我将原始的模拟信号和得到的台阶性的信号相减的话 我们永远会得到这样的一个锯齿波的形式 那这个Q的大小 +1/2Q -1/2Q Q的大小其实就是我们的量化值 我如果采样的频率越快 那我两个Q之间的间距越小 那我两个Q之间的浮值就越小 我得到的这个锯齿波的正负的浮值就越低 相当于我量化噪声的浮值就会越低 当然我们看 整个包围的面积 不管高和低 浮值变低了 但密度变密了 那整个的乘积包围的面积是不变的 我们可以理解为不管量化的频率如何变化 那可以改变浮值 但不能改变造成的能量 或总量是不会变的 那这个量化噪声是无论如何都无法完全消除的 对于这个时间轴上看的话 我们得到的这个 采样信号 就是一个一个的锯齿信号 一个台阶 我们可以把这个锯齿变得很细很密 接近于连续但还是有量化噪声存在的 但这种和实际的连续的 模拟信号之间的差距 这个量化的 锯齿就是我们在数字化 或者采样过程中 丢失的信息 就是我们整个采样过程中 所损失的原始信号的信息 那我们来看看这个频谱 量化噪声 在我的量化频率的时候 它的量化浮值是最大的 会有一些底噪 那我们通过一些信噪比的计算 可以得到 一个固定的公式 就是量化信息的 信噪比系数 signal noise ration 信噪比就是 6.02N+1.76 N代表的是我们离散或者数字采样 到底有多少位 12位就等于12 我用16位 N就等于16 那如果我把N提高 就是我的 AD采样变数变大的话 信噪比是变大的 也就是 说我采样的质量是变好的 就是信噪比系数更高 噪声更低 所以我提高我的AD采样位数 是对我改善我的采样质量 起码在 消除量化噪声方面是有利的 那我们进一步去看 我在数字离散的时候 会有一个Nyquist 频率 或者我们之前比较熟悉的也叫做 香浓频率 就是我们著名的 Nyquist 香浓采样定理 就是说我的浮线 这个红色是我们关心的 这个信号的频率 那为了浮现这个信号 我的采样率至少是这个 信号频率的两倍以上 我才能完整浮现这个信号 那这就是Nyquist采样定理的核心内容 那我们再定义一个FS 就是我们的采样频率 二分之一FS就是一半 然后我们把这些量定义好 那在这个FS采样率采样的情况下 我会有一个噪声平台 这个噪声平台里面 我们这里 主要考虑量化噪声 其他的外界的噪声 我们在这个讨论里暂时不考虑 那我们刚才从上面的信噪比 知道我提高采样的位数 会对我提高 采样有帮助 那其他的 我单纯的 提高采样位数 意味着我用更高成本的ADC采样环节 和芯片 意味着成本的上升 有没有其他办法 在不增加ADC采样位数的情况下 去提高采样的信噪比 下面就是一个理论上的 分析 基于如果我把我的采样率提高 K倍 我的RFs就变成KFS 在这个情况下 可以从分析上看到 整个噪声平台的浮值 从这边这么高 降低了 但相当于是被拉长了拉扁了 所以它的包围面积是不变的 就是说 结合上面一张图看到的和分析到的 就是量化噪声包围的面积 和总量是不变的 无论采样频率的增加减少 所以这里也是一样的 我采样频率增加 整个的噪声总量是不变的 但是 我的噪声浮值降低了 那信噪比 就是我信号的浮值 和噪声的浮值去比 虽然总量没变 但浮值降低了 在我得到原生信号的频率点上它的信噪比就得到了提高和增加 所以这也是一个有效办法 就是进一步提高采样频率 好 下面介绍Delta Sigma的具体实现方式 来解释为何使用它的采样技术 它的采样技术和SAR采样技术相比 优缺点在哪里 帮助大家了解为什么 有这些优缺点 我们首先来看delta sigma的一个典型的采样 首先有个调制环节 delta sigma modulator 这个有点像我们在无线电里面了解到的调制技术 将一个连续的模拟信号经过调制后 变成一个类似PWM的方波信号 频率信号 这个调制很像我们在电源 电机控制里面 发生PWM的方式 这机制相当于我们的 载波和我们高频的调制波 去比较生成一个占空比固定 频率变化的 这么一个频率信号 然后这个信号经过一定的数字滤波 再解调 得到一个数字化的 这个模拟信号的放映 我们看到delta sigma的调制 一般是外挂的独立的调制芯片 这部分 虚线框里面的 数字滤波器加解调这个环节 一般在我们的C2000芯片里面集成 这个就是C2000里面讲的 delta sigma的模块 我们现在很清楚 我们在[听不清]的delta sigma 是数字滤波加解调 并不是完整的 delta sigma采样的整个环节 这里有一个调制环节 必须外挂一个芯片 好 这个有两个 有两个频率 第一个 FS 就是我们的 调制频率 相当于整个调制波的调制频率 FD是我最终解调之后得出的 数据的频率 首先 我们重点看看modulator 调制器是如何工作的 在对一个信号进行delta sigma调制的时候 我们是用下面这个环路 去实现数字化调制 那整个环路的传递函数 我们用下面的两个式子去推导 具体输出等于输入 两个差乘前面两项的积分环节 再加上量化噪声产生的这个点 把DOUT两边解出来 得到的这个式子 量化噪声乘以 这个表达式 相当于一个高滤波器 那输入的模拟的信号通过的相当于一个 低通的滤波器 那这样 我们在[听不清]段 就可以实现 实现的效果类似这样 我们的有效信号 通过一个低通滤波器 我们的量化噪声通过的是一个高通滤波器 我们的量化噪声刚才看到是一个平的平台 那我通过一个高通滤波器 就是在低频段 还是被削弱的 被滤掉的 高频段是会通过去的 所以在高频段会有量化噪声的信息 通过整个调制环节 在低频段 就是我们的有效信息所处段 它的量化噪声被进一步削减 所以通过这个环路后 我们的有效信息所处的频带 它的信噪比 进一步被优化 这就是我们整个的 delta sigma的基本实现原理 是通过比较 最终实现展播这样的信息 那我们调制器的最终输出 其实是这样的波形 里面包含的信息 其实就是我们之前例子中的正旋信息 频率的图形波形就是这样的 在调制器这个环节 对调制器的选择 我们可以选择不同节数的 我们可以选择一节二节三节的 节数越高 浮频特性越好 在低频段 它的衰减就越厉害 在高频段 通过性就越好 但基数越高 我带来的延迟也越大 这是一个权衡 我要更好的 浮频特性 还是 更快的速率响应 这是一个权衡的问题 下面要介绍芯片内部的 数字滤波器加上 解调环节 那数字滤波器呢 其实我们可以用上面调制的浮值特性 我可以用上面调制之后 得到浮频特性 如果我设计一个 数字滤波器是这样的话 那么这个数字滤波器更高频段的信息 类似于低通的数字滤波器 输出掉 那剩下的 就是我有效的数字信息 那我的数字滤波器 它的带宽 浮频特性 我们是可以通过参数和节数来调解的 它的浮频特性是取决于 到底是一节二节还是三节 然后去选择它的截止频率 从而去选择我到底要 多少个频带的信息 通过 把剩下的信息如何滤掉 这是根据我们的应用选择的 但我们知道如果加 这种简单的低通的话 浮频特性上是可以保留有效的信号 但我们在角度特性上 会引入一个相交延迟 这是低通滤波器的一个特点 在这里 如果有相交延迟 相当于是我们的一个缺点 所以我们要想办法解决 如何相交延迟的问题 就是简单的低通滤波器的 相交延迟问题 那我们想 如何实现刚才的浮值特性的特点呢 同时不引入我们 不希望的这种相交延迟 这里有两种大的选择 对数字滤波器来说 第一个 就是我们的sinc filter 我们看这个波形图 把它叫待通滤波器 就是这部分的信号可以通过去 剩下的信号是被衰减掉的 或者就叫陷波滤波器 就是在这些陷下去的点 频点的信号我们把它滤掉 其他频段的信息会通过去 另外一种叫flat passband filter 其中从波形图看 非常类似一个标准的低通滤波器 但是这种呢 我们后面会对比这两种 滤波器 各自的优缺点 对于sync filter来说呢 在半导体里面是性价比更高的 需要的半导体的面积会更少 所消耗的能量更少 延迟会小 因为我们知道 它只对 陷下去的频点的信号进行抑制 其他地方基本上不抑制 更多的这种相交延迟 典型的就是我们的notch filter 典型的公平道滤波器 就是利用50赫兹 60赫兹 对频率非常敏感 比如我们设计一个50赫兹的sync filter或notch filter 如果我通过这个滤波器的信号是51赫兹 那这个滤波效果就会大打折扣 所以它对你设计的陷波的频点 和你的实际信号的频率 要非常一致 才能达到非常好的滤波效果 缺点就是我在这一点上 我把所有点的信号都滤除掉 那其中也可能包含我的有效信息 也是被同样滤除掉了 flat passband呢 我们理解就是一个 标准的低通滤波器 只是它的实现方式是使用非常多节数的FIR LIR滤波器形式来实现这个 波形图的形状 那我们知道 如果你的节数非常高的话 你的延迟也会非常厉害 比如我们这里举例的这个缺点 例子里面 比如我们用50节的FIR实现了 flat passband 那它的延迟就有50个cycle 但如果我用低的节数 比如用10节 5节 那它的波形图的浮频响应就 不会这么理想和完美 低频段就不会是一条直线 可能是一条斜线下来的 它的浮值特性就会受到影响 不是这么理想的低通 那这个图里面 我们就是 更加形象为大家介绍了 让大家看到 这个延迟是如何产生的 那这个最直接的解释就是你有几节 那你就有几个cycle的延迟 因为我们说的节数就是从 就是S的次数 或者就是存储的深度 数字就是它存储的深度 那很容易理解 有几节 就有几个cycle的延迟 那这个就是flat passband 内部的实现原理图 比如我们的这个ADS1672的芯片 它的实现方式就是FIR filter block 有很多节的FIR 实现了最终的波特图 这个芯片需要55个 cycle来settle 去稳定住 但每个cycle会非常短 频率非常快 但仍然需要55个cycle 相对来讲 是会有一定的延迟的 好的 对于delta sigma的 基本实现方式呢 我们先介绍到这里 欢迎大家继续关注后续的章节

大家好 欢迎大家参加TI工业研讨会

我是TI Century FAE Igor An

主要负责数字电源以及 相关算法的开发

今天我给大家介绍TI在电压电流采样中的相关采样技术

主要是利用不同类型的ADC

对电压电流进行采样

这一章节我们介绍Delta Sigma ADC 的采样基本原理

和具体的实现方式

首先 为什么要引入 delta sigma ADC 采样

之前我们了解到SAR ADC

其实在大部分的工业应用中已经

能够比较好的满足 我们对于ADC的要求

那我们为什么还要考虑引入新的技术

去进一步提升我们的ADC的性能指标

那下面我们要介绍的这个概念其实还是一个比较重要的原因

那就是我们的quantization noise

就是我们的量化噪声

那大家看这个图中的斜线

代表的是我们的模拟信号 我们连续的模拟信号

当我将SAR ADC或者其他ADC把它离散化的时候

我得到一个台阶性的信号

那如果我将原始的模拟信号和得到的台阶性的信号相减的话

我们永远会得到这样的一个锯齿波的形式

那这个Q的大小 +1/2Q -1/2Q

Q的大小其实就是我们的量化值

我如果采样的频率越快

那我两个Q之间的间距越小 那我两个Q之间的浮值就越小

我得到的这个锯齿波的正负的浮值就越低

相当于我量化噪声的浮值就会越低

当然我们看 整个包围的面积

不管高和低 浮值变低了

但密度变密了 那整个的乘积包围的面积是不变的

我们可以理解为不管量化的频率如何变化

那可以改变浮值 但不能改变造成的能量

或总量是不会变的

那这个量化噪声是无论如何都无法完全消除的

对于这个时间轴上看的话 我们得到的这个

采样信号 就是一个一个的锯齿信号 一个台阶

我们可以把这个锯齿变得很细很密

接近于连续但还是有量化噪声存在的

但这种和实际的连续的

模拟信号之间的差距 这个量化的

锯齿就是我们在数字化 或者采样过程中

丢失的信息 就是我们整个采样过程中

所损失的原始信号的信息

那我们来看看这个频谱 量化噪声

在我的量化频率的时候 它的量化浮值是最大的

会有一些底噪

那我们通过一些信噪比的计算 可以得到

一个固定的公式 就是量化信息的

信噪比系数 signal noise ration

信噪比就是 6.02N+1.76

N代表的是我们离散或者数字采样

到底有多少位

12位就等于12

我用16位 N就等于16

那如果我把N提高 就是我的 AD采样变数变大的话

信噪比是变大的 也就是

说我采样的质量是变好的

就是信噪比系数更高 噪声更低

所以我提高我的AD采样位数

是对我改善我的采样质量 起码在

消除量化噪声方面是有利的

那我们进一步去看

我在数字离散的时候 会有一个Nyquist

频率 或者我们之前比较熟悉的也叫做

香浓频率

就是我们著名的 Nyquist 香浓采样定理

就是说我的浮线 这个红色是我们关心的

这个信号的频率

那为了浮现这个信号

我的采样率至少是这个 信号频率的两倍以上

我才能完整浮现这个信号

那这就是Nyquist采样定理的核心内容

那我们再定义一个FS

就是我们的采样频率

二分之一FS就是一半

然后我们把这些量定义好

那在这个FS采样率采样的情况下

我会有一个噪声平台

这个噪声平台里面 我们这里

主要考虑量化噪声 其他的外界的噪声

我们在这个讨论里暂时不考虑

那我们刚才从上面的信噪比

知道我提高采样的位数 会对我提高

采样有帮助

那其他的 我单纯的

提高采样位数 意味着我用更高成本的ADC采样环节

和芯片 意味着成本的上升

有没有其他办法 在不增加ADC采样位数的情况下

去提高采样的信噪比 下面就是一个理论上的

分析 基于如果我把我的采样率提高

K倍 我的RFs就变成KFS

在这个情况下 可以从分析上看到

整个噪声平台的浮值 从这边这么高

降低了 但相当于是被拉长了拉扁了

所以它的包围面积是不变的 就是说

结合上面一张图看到的和分析到的

就是量化噪声包围的面积 和总量是不变的

无论采样频率的增加减少

所以这里也是一样的 我采样频率增加

整个的噪声总量是不变的 但是

我的噪声浮值降低了

那信噪比 就是我信号的浮值

和噪声的浮值去比

虽然总量没变 但浮值降低了

在我得到原生信号的频率点上它的信噪比就得到了提高和增加

所以这也是一个有效办法

就是进一步提高采样频率

好 下面介绍Delta Sigma的具体实现方式

来解释为何使用它的采样技术

它的采样技术和SAR采样技术相比

优缺点在哪里 帮助大家了解为什么

有这些优缺点 我们首先来看delta sigma的一个典型的采样

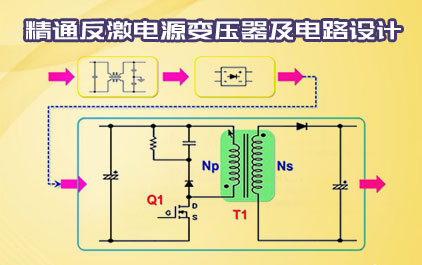

首先有个调制环节 delta sigma modulator

这个有点像我们在无线电里面了解到的调制技术

将一个连续的模拟信号经过调制后

变成一个类似PWM的方波信号 频率信号

这个调制很像我们在电源 电机控制里面

发生PWM的方式 这机制相当于我们的

载波和我们高频的调制波

去比较生成一个占空比固定 频率变化的

这么一个频率信号

然后这个信号经过一定的数字滤波

再解调 得到一个数字化的

这个模拟信号的放映

我们看到delta sigma的调制

一般是外挂的独立的调制芯片

这部分 虚线框里面的

数字滤波器加解调这个环节

一般在我们的C2000芯片里面集成

这个就是C2000里面讲的 delta sigma的模块

我们现在很清楚 我们在[听不清]的delta sigma

是数字滤波加解调 并不是完整的

delta sigma采样的整个环节

这里有一个调制环节 必须外挂一个芯片

好 这个有两个 有两个频率

第一个 FS 就是我们的

调制频率

相当于整个调制波的调制频率

FD是我最终解调之后得出的

数据的频率

首先 我们重点看看modulator

调制器是如何工作的

在对一个信号进行delta sigma调制的时候

我们是用下面这个环路

去实现数字化调制

那整个环路的传递函数

我们用下面的两个式子去推导

具体输出等于输入

两个差乘前面两项的积分环节

再加上量化噪声产生的这个点

把DOUT两边解出来

得到的这个式子 量化噪声乘以

这个表达式 相当于一个高滤波器

那输入的模拟的信号通过的相当于一个

低通的滤波器

那这样 我们在[听不清]段 就可以实现

实现的效果类似这样 我们的有效信号

通过一个低通滤波器

我们的量化噪声通过的是一个高通滤波器

我们的量化噪声刚才看到是一个平的平台

那我通过一个高通滤波器 就是在低频段

还是被削弱的 被滤掉的

高频段是会通过去的

所以在高频段会有量化噪声的信息

通过整个调制环节

在低频段 就是我们的有效信息所处段

它的量化噪声被进一步削减 所以通过这个环路后

我们的有效信息所处的频带 它的信噪比

进一步被优化 这就是我们整个的

delta sigma的基本实现原理

是通过比较 最终实现展播这样的信息

那我们调制器的最终输出

其实是这样的波形 里面包含的信息

其实就是我们之前例子中的正旋信息

频率的图形波形就是这样的

在调制器这个环节 对调制器的选择

我们可以选择不同节数的 我们可以选择一节二节三节的

节数越高 浮频特性越好

在低频段 它的衰减就越厉害

在高频段 通过性就越好

但基数越高 我带来的延迟也越大

这是一个权衡 我要更好的 浮频特性 还是

更快的速率响应

这是一个权衡的问题

下面要介绍芯片内部的 数字滤波器加上

解调环节

那数字滤波器呢

其实我们可以用上面调制的浮值特性

我可以用上面调制之后

得到浮频特性

如果我设计一个 数字滤波器是这样的话

那么这个数字滤波器更高频段的信息

类似于低通的数字滤波器

输出掉 那剩下的

就是我有效的数字信息 那我的数字滤波器

它的带宽 浮频特性

我们是可以通过参数和节数来调解的

它的浮频特性是取决于 到底是一节二节还是三节

然后去选择它的截止频率

从而去选择我到底要 多少个频带的信息

通过 把剩下的信息如何滤掉

这是根据我们的应用选择的

但我们知道如果加 这种简单的低通的话

浮频特性上是可以保留有效的信号

但我们在角度特性上

会引入一个相交延迟 这是低通滤波器的一个特点

在这里 如果有相交延迟 相当于是我们的一个缺点

所以我们要想办法解决 如何相交延迟的问题

就是简单的低通滤波器的 相交延迟问题

那我们想 如何实现刚才的浮值特性的特点呢

同时不引入我们 不希望的这种相交延迟

这里有两种大的选择

对数字滤波器来说 第一个

就是我们的sinc filter

我们看这个波形图 把它叫待通滤波器

就是这部分的信号可以通过去

剩下的信号是被衰减掉的

或者就叫陷波滤波器 就是在这些陷下去的点

频点的信号我们把它滤掉

其他频段的信息会通过去

另外一种叫flat passband filter

其中从波形图看

非常类似一个标准的低通滤波器

但是这种呢 我们后面会对比这两种

滤波器 各自的优缺点

对于sync filter来说呢

在半导体里面是性价比更高的

需要的半导体的面积会更少

所消耗的能量更少

延迟会小 因为我们知道 它只对

陷下去的频点的信号进行抑制

其他地方基本上不抑制

更多的这种相交延迟

典型的就是我们的notch filter

典型的公平道滤波器 就是利用50赫兹 60赫兹

对频率非常敏感

比如我们设计一个50赫兹的sync filter或notch filter

如果我通过这个滤波器的信号是51赫兹

那这个滤波效果就会大打折扣

所以它对你设计的陷波的频点

和你的实际信号的频率

要非常一致 才能达到非常好的滤波效果

缺点就是我在这一点上

我把所有点的信号都滤除掉

那其中也可能包含我的有效信息

也是被同样滤除掉了

flat passband呢 我们理解就是一个

标准的低通滤波器

只是它的实现方式是使用非常多节数的FIR

LIR滤波器形式来实现这个

波形图的形状

那我们知道 如果你的节数非常高的话

你的延迟也会非常厉害

比如我们这里举例的这个缺点

例子里面 比如我们用50节的FIR实现了

flat passband

那它的延迟就有50个cycle

但如果我用低的节数

比如用10节 5节

那它的波形图的浮频响应就

不会这么理想和完美

低频段就不会是一条直线

可能是一条斜线下来的

它的浮值特性就会受到影响

不是这么理想的低通

那这个图里面 我们就是

更加形象为大家介绍了 让大家看到

这个延迟是如何产生的

那这个最直接的解释就是你有几节

那你就有几个cycle的延迟

因为我们说的节数就是从

就是S的次数

或者就是存储的深度

数字就是它存储的深度

那很容易理解 有几节 就有几个cycle的延迟

那这个就是flat passband 内部的实现原理图

比如我们的这个ADS1672的芯片

它的实现方式就是FIR filter

block 有很多节的FIR

实现了最终的波特图

这个芯片需要55个 cycle来settle 去稳定住

但每个cycle会非常短 频率非常快

但仍然需要55个cycle

相对来讲 是会有一定的延迟的

好的 对于delta sigma的 基本实现方式呢

我们先介绍到这里

欢迎大家继续关注后续的章节

大家好 欢迎大家参加TI工业研讨会 我是TI Century FAE Igor An 主要负责数字电源以及 相关算法的开发 今天我给大家介绍TI在电压电流采样中的相关采样技术 主要是利用不同类型的ADC 对电压电流进行采样 这一章节我们介绍Delta Sigma ADC 的采样基本原理 和具体的实现方式 首先 为什么要引入 delta sigma ADC 采样 之前我们了解到SAR ADC 其实在大部分的工业应用中已经 能够比较好的满足 我们对于ADC的要求 那我们为什么还要考虑引入新的技术 去进一步提升我们的ADC的性能指标 那下面我们要介绍的这个概念其实还是一个比较重要的原因 那就是我们的quantization noise 就是我们的量化噪声 那大家看这个图中的斜线 代表的是我们的模拟信号 我们连续的模拟信号 当我将SAR ADC或者其他ADC把它离散化的时候 我得到一个台阶性的信号 那如果我将原始的模拟信号和得到的台阶性的信号相减的话 我们永远会得到这样的一个锯齿波的形式 那这个Q的大小 +1/2Q -1/2Q Q的大小其实就是我们的量化值 我如果采样的频率越快 那我两个Q之间的间距越小 那我两个Q之间的浮值就越小 我得到的这个锯齿波的正负的浮值就越低 相当于我量化噪声的浮值就会越低 当然我们看 整个包围的面积 不管高和低 浮值变低了 但密度变密了 那整个的乘积包围的面积是不变的 我们可以理解为不管量化的频率如何变化 那可以改变浮值 但不能改变造成的能量 或总量是不会变的 那这个量化噪声是无论如何都无法完全消除的 对于这个时间轴上看的话 我们得到的这个 采样信号 就是一个一个的锯齿信号 一个台阶 我们可以把这个锯齿变得很细很密 接近于连续但还是有量化噪声存在的 但这种和实际的连续的 模拟信号之间的差距 这个量化的 锯齿就是我们在数字化 或者采样过程中 丢失的信息 就是我们整个采样过程中 所损失的原始信号的信息 那我们来看看这个频谱 量化噪声 在我的量化频率的时候 它的量化浮值是最大的 会有一些底噪 那我们通过一些信噪比的计算 可以得到 一个固定的公式 就是量化信息的 信噪比系数 signal noise ration 信噪比就是 6.02N+1.76 N代表的是我们离散或者数字采样 到底有多少位 12位就等于12 我用16位 N就等于16 那如果我把N提高 就是我的 AD采样变数变大的话 信噪比是变大的 也就是 说我采样的质量是变好的 就是信噪比系数更高 噪声更低 所以我提高我的AD采样位数 是对我改善我的采样质量 起码在 消除量化噪声方面是有利的 那我们进一步去看 我在数字离散的时候 会有一个Nyquist 频率 或者我们之前比较熟悉的也叫做 香浓频率 就是我们著名的 Nyquist 香浓采样定理 就是说我的浮线 这个红色是我们关心的 这个信号的频率 那为了浮现这个信号 我的采样率至少是这个 信号频率的两倍以上 我才能完整浮现这个信号 那这就是Nyquist采样定理的核心内容 那我们再定义一个FS 就是我们的采样频率 二分之一FS就是一半 然后我们把这些量定义好 那在这个FS采样率采样的情况下 我会有一个噪声平台 这个噪声平台里面 我们这里 主要考虑量化噪声 其他的外界的噪声 我们在这个讨论里暂时不考虑 那我们刚才从上面的信噪比 知道我提高采样的位数 会对我提高 采样有帮助 那其他的 我单纯的 提高采样位数 意味着我用更高成本的ADC采样环节 和芯片 意味着成本的上升 有没有其他办法 在不增加ADC采样位数的情况下 去提高采样的信噪比 下面就是一个理论上的 分析 基于如果我把我的采样率提高 K倍 我的RFs就变成KFS 在这个情况下 可以从分析上看到 整个噪声平台的浮值 从这边这么高 降低了 但相当于是被拉长了拉扁了 所以它的包围面积是不变的 就是说 结合上面一张图看到的和分析到的 就是量化噪声包围的面积 和总量是不变的 无论采样频率的增加减少 所以这里也是一样的 我采样频率增加 整个的噪声总量是不变的 但是 我的噪声浮值降低了 那信噪比 就是我信号的浮值 和噪声的浮值去比 虽然总量没变 但浮值降低了 在我得到原生信号的频率点上它的信噪比就得到了提高和增加 所以这也是一个有效办法 就是进一步提高采样频率 好 下面介绍Delta Sigma的具体实现方式 来解释为何使用它的采样技术 它的采样技术和SAR采样技术相比 优缺点在哪里 帮助大家了解为什么 有这些优缺点 我们首先来看delta sigma的一个典型的采样 首先有个调制环节 delta sigma modulator 这个有点像我们在无线电里面了解到的调制技术 将一个连续的模拟信号经过调制后 变成一个类似PWM的方波信号 频率信号 这个调制很像我们在电源 电机控制里面 发生PWM的方式 这机制相当于我们的 载波和我们高频的调制波 去比较生成一个占空比固定 频率变化的 这么一个频率信号 然后这个信号经过一定的数字滤波 再解调 得到一个数字化的 这个模拟信号的放映 我们看到delta sigma的调制 一般是外挂的独立的调制芯片 这部分 虚线框里面的 数字滤波器加解调这个环节 一般在我们的C2000芯片里面集成 这个就是C2000里面讲的 delta sigma的模块 我们现在很清楚 我们在[听不清]的delta sigma 是数字滤波加解调 并不是完整的 delta sigma采样的整个环节 这里有一个调制环节 必须外挂一个芯片 好 这个有两个 有两个频率 第一个 FS 就是我们的 调制频率 相当于整个调制波的调制频率 FD是我最终解调之后得出的 数据的频率 首先 我们重点看看modulator 调制器是如何工作的 在对一个信号进行delta sigma调制的时候 我们是用下面这个环路 去实现数字化调制 那整个环路的传递函数 我们用下面的两个式子去推导 具体输出等于输入 两个差乘前面两项的积分环节 再加上量化噪声产生的这个点 把DOUT两边解出来 得到的这个式子 量化噪声乘以 这个表达式 相当于一个高滤波器 那输入的模拟的信号通过的相当于一个 低通的滤波器 那这样 我们在[听不清]段 就可以实现 实现的效果类似这样 我们的有效信号 通过一个低通滤波器 我们的量化噪声通过的是一个高通滤波器 我们的量化噪声刚才看到是一个平的平台 那我通过一个高通滤波器 就是在低频段 还是被削弱的 被滤掉的 高频段是会通过去的 所以在高频段会有量化噪声的信息 通过整个调制环节 在低频段 就是我们的有效信息所处段 它的量化噪声被进一步削减 所以通过这个环路后 我们的有效信息所处的频带 它的信噪比 进一步被优化 这就是我们整个的 delta sigma的基本实现原理 是通过比较 最终实现展播这样的信息 那我们调制器的最终输出 其实是这样的波形 里面包含的信息 其实就是我们之前例子中的正旋信息 频率的图形波形就是这样的 在调制器这个环节 对调制器的选择 我们可以选择不同节数的 我们可以选择一节二节三节的 节数越高 浮频特性越好 在低频段 它的衰减就越厉害 在高频段 通过性就越好 但基数越高 我带来的延迟也越大 这是一个权衡 我要更好的 浮频特性 还是 更快的速率响应 这是一个权衡的问题 下面要介绍芯片内部的 数字滤波器加上 解调环节 那数字滤波器呢 其实我们可以用上面调制的浮值特性 我可以用上面调制之后 得到浮频特性 如果我设计一个 数字滤波器是这样的话 那么这个数字滤波器更高频段的信息 类似于低通的数字滤波器 输出掉 那剩下的 就是我有效的数字信息 那我的数字滤波器 它的带宽 浮频特性 我们是可以通过参数和节数来调解的 它的浮频特性是取决于 到底是一节二节还是三节 然后去选择它的截止频率 从而去选择我到底要 多少个频带的信息 通过 把剩下的信息如何滤掉 这是根据我们的应用选择的 但我们知道如果加 这种简单的低通的话 浮频特性上是可以保留有效的信号 但我们在角度特性上 会引入一个相交延迟 这是低通滤波器的一个特点 在这里 如果有相交延迟 相当于是我们的一个缺点 所以我们要想办法解决 如何相交延迟的问题 就是简单的低通滤波器的 相交延迟问题 那我们想 如何实现刚才的浮值特性的特点呢 同时不引入我们 不希望的这种相交延迟 这里有两种大的选择 对数字滤波器来说 第一个 就是我们的sinc filter 我们看这个波形图 把它叫待通滤波器 就是这部分的信号可以通过去 剩下的信号是被衰减掉的 或者就叫陷波滤波器 就是在这些陷下去的点 频点的信号我们把它滤掉 其他频段的信息会通过去 另外一种叫flat passband filter 其中从波形图看 非常类似一个标准的低通滤波器 但是这种呢 我们后面会对比这两种 滤波器 各自的优缺点 对于sync filter来说呢 在半导体里面是性价比更高的 需要的半导体的面积会更少 所消耗的能量更少 延迟会小 因为我们知道 它只对 陷下去的频点的信号进行抑制 其他地方基本上不抑制 更多的这种相交延迟 典型的就是我们的notch filter 典型的公平道滤波器 就是利用50赫兹 60赫兹 对频率非常敏感 比如我们设计一个50赫兹的sync filter或notch filter 如果我通过这个滤波器的信号是51赫兹 那这个滤波效果就会大打折扣 所以它对你设计的陷波的频点 和你的实际信号的频率 要非常一致 才能达到非常好的滤波效果 缺点就是我在这一点上 我把所有点的信号都滤除掉 那其中也可能包含我的有效信息 也是被同样滤除掉了 flat passband呢 我们理解就是一个 标准的低通滤波器 只是它的实现方式是使用非常多节数的FIR LIR滤波器形式来实现这个 波形图的形状 那我们知道 如果你的节数非常高的话 你的延迟也会非常厉害 比如我们这里举例的这个缺点 例子里面 比如我们用50节的FIR实现了 flat passband 那它的延迟就有50个cycle 但如果我用低的节数 比如用10节 5节 那它的波形图的浮频响应就 不会这么理想和完美 低频段就不会是一条直线 可能是一条斜线下来的 它的浮值特性就会受到影响 不是这么理想的低通 那这个图里面 我们就是 更加形象为大家介绍了 让大家看到 这个延迟是如何产生的 那这个最直接的解释就是你有几节 那你就有几个cycle的延迟 因为我们说的节数就是从 就是S的次数 或者就是存储的深度 数字就是它存储的深度 那很容易理解 有几节 就有几个cycle的延迟 那这个就是flat passband 内部的实现原理图 比如我们的这个ADS1672的芯片 它的实现方式就是FIR filter block 有很多节的FIR 实现了最终的波特图 这个芯片需要55个 cycle来settle 去稳定住 但每个cycle会非常短 频率非常快 但仍然需要55个cycle 相对来讲 是会有一定的延迟的 好的 对于delta sigma的 基本实现方式呢 我们先介绍到这里 欢迎大家继续关注后续的章节

大家好 欢迎大家参加TI工业研讨会

我是TI Century FAE Igor An

主要负责数字电源以及 相关算法的开发

今天我给大家介绍TI在电压电流采样中的相关采样技术

主要是利用不同类型的ADC

对电压电流进行采样

这一章节我们介绍Delta Sigma ADC 的采样基本原理

和具体的实现方式

首先 为什么要引入 delta sigma ADC 采样

之前我们了解到SAR ADC

其实在大部分的工业应用中已经

能够比较好的满足 我们对于ADC的要求

那我们为什么还要考虑引入新的技术

去进一步提升我们的ADC的性能指标

那下面我们要介绍的这个概念其实还是一个比较重要的原因

那就是我们的quantization noise

就是我们的量化噪声

那大家看这个图中的斜线

代表的是我们的模拟信号 我们连续的模拟信号

当我将SAR ADC或者其他ADC把它离散化的时候

我得到一个台阶性的信号

那如果我将原始的模拟信号和得到的台阶性的信号相减的话

我们永远会得到这样的一个锯齿波的形式

那这个Q的大小 +1/2Q -1/2Q

Q的大小其实就是我们的量化值

我如果采样的频率越快

那我两个Q之间的间距越小 那我两个Q之间的浮值就越小

我得到的这个锯齿波的正负的浮值就越低

相当于我量化噪声的浮值就会越低

当然我们看 整个包围的面积

不管高和低 浮值变低了

但密度变密了 那整个的乘积包围的面积是不变的

我们可以理解为不管量化的频率如何变化

那可以改变浮值 但不能改变造成的能量

或总量是不会变的

那这个量化噪声是无论如何都无法完全消除的

对于这个时间轴上看的话 我们得到的这个

采样信号 就是一个一个的锯齿信号 一个台阶

我们可以把这个锯齿变得很细很密

接近于连续但还是有量化噪声存在的

但这种和实际的连续的

模拟信号之间的差距 这个量化的

锯齿就是我们在数字化 或者采样过程中

丢失的信息 就是我们整个采样过程中

所损失的原始信号的信息

那我们来看看这个频谱 量化噪声

在我的量化频率的时候 它的量化浮值是最大的

会有一些底噪

那我们通过一些信噪比的计算 可以得到

一个固定的公式 就是量化信息的

信噪比系数 signal noise ration

信噪比就是 6.02N+1.76

N代表的是我们离散或者数字采样

到底有多少位

12位就等于12

我用16位 N就等于16

那如果我把N提高 就是我的 AD采样变数变大的话

信噪比是变大的 也就是

说我采样的质量是变好的

就是信噪比系数更高 噪声更低

所以我提高我的AD采样位数

是对我改善我的采样质量 起码在

消除量化噪声方面是有利的

那我们进一步去看

我在数字离散的时候 会有一个Nyquist

频率 或者我们之前比较熟悉的也叫做

香浓频率

就是我们著名的 Nyquist 香浓采样定理

就是说我的浮线 这个红色是我们关心的

这个信号的频率

那为了浮现这个信号

我的采样率至少是这个 信号频率的两倍以上

我才能完整浮现这个信号

那这就是Nyquist采样定理的核心内容

那我们再定义一个FS

就是我们的采样频率

二分之一FS就是一半

然后我们把这些量定义好

那在这个FS采样率采样的情况下

我会有一个噪声平台

这个噪声平台里面 我们这里

主要考虑量化噪声 其他的外界的噪声

我们在这个讨论里暂时不考虑

那我们刚才从上面的信噪比

知道我提高采样的位数 会对我提高

采样有帮助

那其他的 我单纯的

提高采样位数 意味着我用更高成本的ADC采样环节

和芯片 意味着成本的上升

有没有其他办法 在不增加ADC采样位数的情况下

去提高采样的信噪比 下面就是一个理论上的

分析 基于如果我把我的采样率提高

K倍 我的RFs就变成KFS

在这个情况下 可以从分析上看到

整个噪声平台的浮值 从这边这么高

降低了 但相当于是被拉长了拉扁了

所以它的包围面积是不变的 就是说

结合上面一张图看到的和分析到的

就是量化噪声包围的面积 和总量是不变的

无论采样频率的增加减少

所以这里也是一样的 我采样频率增加

整个的噪声总量是不变的 但是

我的噪声浮值降低了

那信噪比 就是我信号的浮值

和噪声的浮值去比

虽然总量没变 但浮值降低了

在我得到原生信号的频率点上它的信噪比就得到了提高和增加

所以这也是一个有效办法

就是进一步提高采样频率

好 下面介绍Delta Sigma的具体实现方式

来解释为何使用它的采样技术

它的采样技术和SAR采样技术相比

优缺点在哪里 帮助大家了解为什么

有这些优缺点 我们首先来看delta sigma的一个典型的采样

首先有个调制环节 delta sigma modulator

这个有点像我们在无线电里面了解到的调制技术

将一个连续的模拟信号经过调制后

变成一个类似PWM的方波信号 频率信号

这个调制很像我们在电源 电机控制里面

发生PWM的方式 这机制相当于我们的

载波和我们高频的调制波

去比较生成一个占空比固定 频率变化的

这么一个频率信号

然后这个信号经过一定的数字滤波

再解调 得到一个数字化的

这个模拟信号的放映

我们看到delta sigma的调制

一般是外挂的独立的调制芯片

这部分 虚线框里面的

数字滤波器加解调这个环节

一般在我们的C2000芯片里面集成

这个就是C2000里面讲的 delta sigma的模块

我们现在很清楚 我们在[听不清]的delta sigma

是数字滤波加解调 并不是完整的

delta sigma采样的整个环节

这里有一个调制环节 必须外挂一个芯片

好 这个有两个 有两个频率

第一个 FS 就是我们的

调制频率

相当于整个调制波的调制频率

FD是我最终解调之后得出的

数据的频率

首先 我们重点看看modulator

调制器是如何工作的

在对一个信号进行delta sigma调制的时候

我们是用下面这个环路

去实现数字化调制

那整个环路的传递函数

我们用下面的两个式子去推导

具体输出等于输入

两个差乘前面两项的积分环节

再加上量化噪声产生的这个点

把DOUT两边解出来

得到的这个式子 量化噪声乘以

这个表达式 相当于一个高滤波器

那输入的模拟的信号通过的相当于一个

低通的滤波器

那这样 我们在[听不清]段 就可以实现

实现的效果类似这样 我们的有效信号

通过一个低通滤波器

我们的量化噪声通过的是一个高通滤波器

我们的量化噪声刚才看到是一个平的平台

那我通过一个高通滤波器 就是在低频段

还是被削弱的 被滤掉的

高频段是会通过去的

所以在高频段会有量化噪声的信息

通过整个调制环节

在低频段 就是我们的有效信息所处段

它的量化噪声被进一步削减 所以通过这个环路后

我们的有效信息所处的频带 它的信噪比

进一步被优化 这就是我们整个的

delta sigma的基本实现原理

是通过比较 最终实现展播这样的信息

那我们调制器的最终输出

其实是这样的波形 里面包含的信息

其实就是我们之前例子中的正旋信息

频率的图形波形就是这样的

在调制器这个环节 对调制器的选择

我们可以选择不同节数的 我们可以选择一节二节三节的

节数越高 浮频特性越好

在低频段 它的衰减就越厉害

在高频段 通过性就越好

但基数越高 我带来的延迟也越大

这是一个权衡 我要更好的 浮频特性 还是

更快的速率响应

这是一个权衡的问题

下面要介绍芯片内部的 数字滤波器加上

解调环节

那数字滤波器呢

其实我们可以用上面调制的浮值特性

我可以用上面调制之后

得到浮频特性

如果我设计一个 数字滤波器是这样的话

那么这个数字滤波器更高频段的信息

类似于低通的数字滤波器

输出掉 那剩下的

就是我有效的数字信息 那我的数字滤波器

它的带宽 浮频特性

我们是可以通过参数和节数来调解的

它的浮频特性是取决于 到底是一节二节还是三节

然后去选择它的截止频率

从而去选择我到底要 多少个频带的信息

通过 把剩下的信息如何滤掉

这是根据我们的应用选择的

但我们知道如果加 这种简单的低通的话

浮频特性上是可以保留有效的信号

但我们在角度特性上

会引入一个相交延迟 这是低通滤波器的一个特点

在这里 如果有相交延迟 相当于是我们的一个缺点

所以我们要想办法解决 如何相交延迟的问题

就是简单的低通滤波器的 相交延迟问题

那我们想 如何实现刚才的浮值特性的特点呢

同时不引入我们 不希望的这种相交延迟

这里有两种大的选择

对数字滤波器来说 第一个

就是我们的sinc filter

我们看这个波形图 把它叫待通滤波器

就是这部分的信号可以通过去

剩下的信号是被衰减掉的

或者就叫陷波滤波器 就是在这些陷下去的点

频点的信号我们把它滤掉

其他频段的信息会通过去

另外一种叫flat passband filter

其中从波形图看

非常类似一个标准的低通滤波器

但是这种呢 我们后面会对比这两种

滤波器 各自的优缺点

对于sync filter来说呢

在半导体里面是性价比更高的

需要的半导体的面积会更少

所消耗的能量更少

延迟会小 因为我们知道 它只对

陷下去的频点的信号进行抑制

其他地方基本上不抑制

更多的这种相交延迟

典型的就是我们的notch filter

典型的公平道滤波器 就是利用50赫兹 60赫兹

对频率非常敏感

比如我们设计一个50赫兹的sync filter或notch filter

如果我通过这个滤波器的信号是51赫兹

那这个滤波效果就会大打折扣

所以它对你设计的陷波的频点

和你的实际信号的频率

要非常一致 才能达到非常好的滤波效果

缺点就是我在这一点上

我把所有点的信号都滤除掉

那其中也可能包含我的有效信息

也是被同样滤除掉了

flat passband呢 我们理解就是一个

标准的低通滤波器

只是它的实现方式是使用非常多节数的FIR

LIR滤波器形式来实现这个

波形图的形状

那我们知道 如果你的节数非常高的话

你的延迟也会非常厉害

比如我们这里举例的这个缺点

例子里面 比如我们用50节的FIR实现了

flat passband

那它的延迟就有50个cycle

但如果我用低的节数

比如用10节 5节

那它的波形图的浮频响应就

不会这么理想和完美

低频段就不会是一条直线

可能是一条斜线下来的

它的浮值特性就会受到影响

不是这么理想的低通

那这个图里面 我们就是

更加形象为大家介绍了 让大家看到

这个延迟是如何产生的

那这个最直接的解释就是你有几节

那你就有几个cycle的延迟

因为我们说的节数就是从

就是S的次数

或者就是存储的深度

数字就是它存储的深度

那很容易理解 有几节 就有几个cycle的延迟

那这个就是flat passband 内部的实现原理图

比如我们的这个ADS1672的芯片

它的实现方式就是FIR filter

block 有很多节的FIR

实现了最终的波特图

这个芯片需要55个 cycle来settle 去稳定住

但每个cycle会非常短 频率非常快

但仍然需要55个cycle

相对来讲 是会有一定的延迟的

好的 对于delta sigma的 基本实现方式呢

我们先介绍到这里

欢迎大家继续关注后续的章节

手机看

扫码用手机观看

视频简介

视频简介

Sigma Delta ADC 工作原理介绍

所属课程:电机控制之电压与电流采样方案

发布时间:2017.05.04

视频集数:4

本节视频时长:00:19:41

TI在电机系统中的电压电流采样技术详解(SAR ADC/Sigma Delta ADC详述及比较)。

未学习 主要ADC采样技术简介SAR ADC原理介绍

未学习 主要ADC采样技术简介SAR ADC原理介绍

未学习 Sigma Delta ADC 工作原理介绍

未学习 Sigma Delta ADC 工作原理介绍

未学习 SAR ADC与Sigma Delta ADC比较

未学习 SAR ADC与Sigma Delta ADC比较

未学习 模拟前端设计指南

未学习 模拟前端设计指南