2. TI 高精度实验室-隔离:什么是数字隔离器?

Loading the player...

将在30s后自动为您播放下一课程

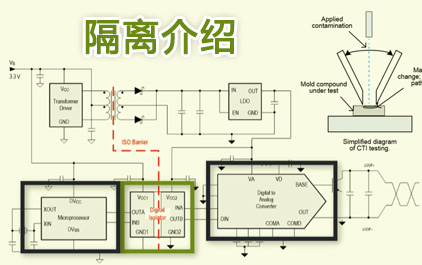

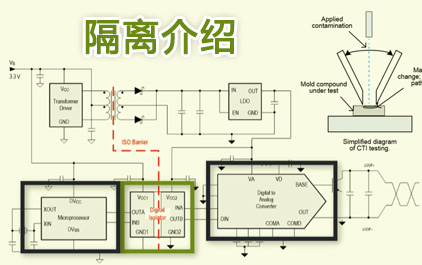

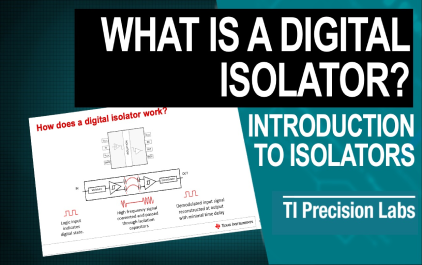

[音乐播放] 大家好,欢迎观看 TI 高精度实验室视频。 TI 的高精度 实验室视频节目 是面向工程师的 综合在线课程。 这段视频 将介绍有关 数字隔离器的 基本问题。 如需查看更多 视频和主题, 请访问 ti.com/precisionlabs。 什么是数字隔离器? 电隔离是在 存在高压事件时 与人或其他 电路相连的 所有电子器件的 必要保护形式。 在确保人身安全 甚至电子保护的情况下, 高压事件的电压范围 可能从几十伏 到几千伏。 在过去的几十年中, 用于隔离电路的 技术已经 从基于光学的 光耦合器发展到了 基于硅的技术, 其中,数字隔离器 是越来越多 设计人员的首选。 本视频将 主要讨论 基于电容的 数字隔离器。 有关隔离技术的 一般介绍 可以在名为 “什么是电隔离”的 高精度实验室主题中找到。 本高精度实验室主题 将回答以下问题。 什么是数字隔离器? 电容数字隔离器 是如何构建的? 基于边沿的数字隔离器 如何工作? 开关键控 (OOK) 数字隔离器 如何工作? 哪种数字 隔离器架构 最适合我的设计? 让我们开始吧。 什么是数字隔离器? 数字隔离器 是用于隔离 数字信号并 跨隔离栅 传输数字通信的 集成器件。 由于数字隔离器 使用经过 预先数字化处理的 数据流,因此它们 通常跟随在 一个系统中的 ADC 之后, 这个系统在 不同电源电平的 微处理器 和 FPGA 之间, 或者在具有 共享背板的 接口通信板之间。 在此示例中, 数字隔离器 在 4 至 20 毫安的 环路中保护 MCU 数据线路免受 输出数模转换器的影响。 在查看此处 所示的用例时, 很明显可以 看出,在使用 数字隔离器时, 也需要隔离式电源。 如需了解关于隔离器 电源设计的更多 详细信息,请参阅 高精度实验室视频, 标题为“如何为 数字隔离器设计隔离式 电源”。 现在,我们深入 了解一下数字隔离器。 数字隔离器 如何工作? 这里显示了一个典型 数字隔离器的引脚图。 它包含两个 隔离式电源 VCC1 和 VCC2,两个接地端 GND1 和 GND2, 还有两侧 以各自接地端为基准的 输入和输出引脚。 输入信号 通过发送 IC 进行调制, 然后通过高压电容隔离层 并跨越接合线 到达接收侧 IC。 理想情况下, 施加输入信号时, 数字输入和输出 是相同的。 正如前面提到的, 数字隔离器 最常与采用独立 接地端的隔离式电源 一起使用, 这对于 防止电源的 接地干扰和噪声电流 也很有用。 数字隔离器使用 CMOS 或 TTL 逻辑开关技术, 并具有指定的高电平 或低电平默认输出状态, 可以在数据表的 器件功能模式部分 找到这些状态, 如此处所示。 如表中所示, 如果输入断开 或 BCC1 断开, 则输出 将转换为 逻辑状态高电平。 这一行为称为 失效防护高电平。 另一方面,某些器件 在断开状态下会变成低电平, 称为失效防护低电平。 定义此行为 是为了防止 在电源中断或 电压不足的情况下出现 错误代码。 两个电源 VCC1 和 VCC2 的 数字隔离器的 逻辑电平范围都可以 在 1.8 至 5.5 伏之间, 但有些器件可能支持更大的 电源范围。 由于隔离器基于 两个独立的内部 IC, 因此可以在 数字隔离器的每一侧 使用两个不同的 电源电压。 现在我们已经 大致了解了 数字隔离器在 功能级的工作方式, 我们接下来将讨论 数字隔离器的内部结构 和架构。 电容数字隔离器 是如何构建的? 电容数字隔离器 使用基于 CMOS 技术的 硅基电介质, 包含两个独立的 集成电路 (IC) 芯片: 一个输入电路和 一个输出电路, 通过接合线和 高质量、 耐高压的 模塑化合物相连。 这里显示了数字隔离器的 横截面和 X 射线。 数字隔离器 电路的绝缘体 可以是单个或两个 二氧化硅电容隔离层, 根据设计 可以承受极高的 电压。 基于电容的 隔离器 由半导体行业中 最高电介质强度的 材料制成, 并在受严格控制的 清洁室晶圆厂中 进行制造, 从而使零部件之间的 差异最小。 由于严格控制的 制造环境 和二氧化硅 电介质的质量, 影响隔离性能的 关键因素 主要是技术本身 和设计架构。 电容隔离器通常 采用两种主要的 调制架构: 开关键控 (OOK) 或基于边沿的架构。 这两个名称都描述了 用于触发输出更改的 时序方案。 基于边沿的隔离器 如何工作? 对于基于边沿的 数字隔离器, 如此处所示的 隔离器,数据传输 由指定持续时间的 输入脉冲进行启动。 I/O 通道包含两个 内部数据通道: 一个高频通道, 带宽从 100 千比特/秒 到 25 兆比特/秒, 以及一个低频通道, 涵盖 100 千比特/秒 到直流的 范围。 进入高频通道的 单端输入信号 通过输入端的 反相器门 分解为 差分信号。 然后,电容器电阻网络 将信号分化为 瞬态脉冲, 而高频通道 比较器输出端的 判定逻辑 将测量信号瞬态之间的 持续时间。 如果两个 连续瞬态之间的 持续时间超过特定的 时间限制, 例如在低频信号的 情况下,则判定逻辑 会强制输出多路复用器 从高频通道切换到低频通道。 低频信号通过 内部振荡器的 载波频率进行 脉宽调制, 从而产生能够通过 电容隔离层的 高频信号。 振荡器用于设置 直流 PWM 通道的 时标,使用的 时基通常为 数十纳秒。 然后会以高于 振荡器频率的 可能最小的数据包 对 PWM 通信进行 数据包处理。 根据设计, 基于边沿的隔离器 可以使该振荡器频率 不会反映在 输出频谱中。 在对输入进行调制时, 需要使用一个低通滤波器 消除实际数据中的 高频载波, 然后再将其 传递到输出多路复用器 和输出引脚上, 从而重建 数字输入信号的 电隔离版本。 开关键控数字隔离器 如何工作? 在开关键控 OOK 架构中, 将使用内部 扩频振荡器时钟 对输入的数字比特流 进行调制, 这个时钟的 工作频率 超出器件可用的 数据速率范围。 该时钟频率用于 生成 OOK 信令, 以使输入状态之一通过 传输载波频率来表示, 而另一状态 不通过传输表示。 经过调制的此信号 将耦合到隔离栅, 并以衰减的形式 出现在接收侧, 该接收侧包含用于 放大输入信号的前置放大器 以及包络检波器。 该器件可用作 解调器以重新生成 原始数字模式。 发送和接收 信号调节电路 用于改善 通道的共模抑制, 从而产生更好的 共模瞬态抗扰度, 即 CMTI。 哪种架构最适合 我的设计? 基于边沿的调制方案的 主要优点之一 是比 OOK 架构的 功耗更低。 这是因为基于边沿的 调制隔离器 仅在数据转换 或边沿期间 跨隔离栅传递信号。 因此,这种架构的 功耗大大低于 OOK 架构, OOK 架构会持续采样, 并跨屏蔽层传输 经过调制的输入。 由于这种 连续性的传输, 与基于 PWM 边沿的 架构相比, OOK 架构所需的 功率要大得多。 这些架构 是否有特定的 挑战和优势? 的确,有一些权衡因素。 对于基于边沿的 架构,一旦启动 数据信号,就不会 再对输入和输出状态 进行采样。 这确实会在 电压不足或 数据信号故障的情况下 产生出错风险, 因此需要集成的 刷新电路 来减轻这些条件下的 出错风险, 以便在输出端 强化输入状态。 对于 OOK 方案, 在电源或输入信号 意外变化的情况下 对输入进行连续采样 将不会在输出端 显示任何错误。 尽管基于 边沿的架构 由于其采样方案 而具有特定的功耗优势, 但在前面提到过, 信号调节电路 和开关键控 调制方案 具有固有的噪声 和瞬态响应优势, 同时 CMTI 会高得多, 数据速率也更高。 那么,哪种电容 数字隔离器拓扑 真正适合 您的设计? 在考虑每种架构时, 除了关键的 隔离规格外, 请记住要考虑 功耗与数据速率、 最高可能的 共模抗扰度 以及错误条件管理 等其他重要的 设计注意事项, 以便帮助您确定 最适合自己的方案。 数字隔离器的介绍 到此结束。 我们讨论了 数字隔离器 用于跨隔离栅 传递数字信号, 并且需要隔离式 电源和接地。 电容隔离是使用 硅电介质实现的, 这种材料是业界 电介质强度最高的 绝缘材料。 电容数字隔离器 有两种主要架构: 基于边沿的架构 或 OOK 架构。 基于边沿和基于 OOK 的 电容数字隔离器设计 之间的主要区别 包括输出状态: 基于边沿和基于 OOK 的 数字隔离解决方案 均具有器件数据表中 预定义的 默认输出高电平和 低电平状态。 还包括数据传输: 基于边沿的解决方案 在指定长度的 输入脉冲之后 跨隔离栅 传输数据流, 使用输入流的边沿 构建输出流。 而基于 OOK 的 解决方案,也就是 开关键控解决方案, 通过高频载波 跨隔离栅 传输数据流, 因此改善了 噪声和 CMTI 性能。 最后一个区别是功耗。 基于边沿的架构具有 更低的功耗和更低的数据速率, 而 OOK 架构具有 更高的功耗和更高的数据速率。 高精度实验室主题 “什么是数字隔离器” 到此结束。 谢谢观看。 请尝试完成在线测验 以测试所学到的知识。 问题 1. 哪种绝缘材料 具有最高的 电介质强度? 模塑化合物、聚酰亚胺、 空气还是二氧化硅? 二氧化硅具有 最高的电介质强度, 约为每微米 500 伏。 最常用的 数字隔离器技术 是光学和电感、 电容和光学 或电容和电感。 电容和 电感拓扑 是最常用于 数字隔离的拓扑。 对或错-- 数字隔离器可以 在两个不同的 VCC1 和 VCC2 电源电压下工作。 对。 VCC1 和 VCC2 可以采用 不同的电压值运行, 并且仍然保持 数据表中的性能。 在基于边沿的 数字架构和开关键控 数字架构之间 需要考虑的三个 关键权衡因素是什么? 基于边沿的架构 和电容架构之间 最常见的 权衡因素是 数据速率、功耗 和噪声抑制。 TI 高精度实验室主题 “什么是数字隔离器?” 到此结束。 谢谢观看。 请访问 www.ti.com/precisionlabs, 浏览更多主题。

[音乐播放] 大家好,欢迎观看 TI 高精度实验室视频。 TI 的高精度 实验室视频节目 是面向工程师的 综合在线课程。 这段视频 将介绍有关 数字隔离器的 基本问题。 如需查看更多 视频和主题, 请访问 ti.com/precisionlabs。 什么是数字隔离器? 电隔离是在 存在高压事件时 与人或其他 电路相连的 所有电子器件的 必要保护形式。 在确保人身安全 甚至电子保护的情况下, 高压事件的电压范围 可能从几十伏 到几千伏。 在过去的几十年中, 用于隔离电路的 技术已经 从基于光学的 光耦合器发展到了 基于硅的技术, 其中,数字隔离器 是越来越多 设计人员的首选。 本视频将 主要讨论 基于电容的 数字隔离器。 有关隔离技术的 一般介绍 可以在名为 “什么是电隔离”的 高精度实验室主题中找到。 本高精度实验室主题 将回答以下问题。 什么是数字隔离器? 电容数字隔离器 是如何构建的? 基于边沿的数字隔离器 如何工作? 开关键控 (OOK) 数字隔离器 如何工作? 哪种数字 隔离器架构 最适合我的设计? 让我们开始吧。 什么是数字隔离器? 数字隔离器 是用于隔离 数字信号并 跨隔离栅 传输数字通信的 集成器件。 由于数字隔离器 使用经过 预先数字化处理的 数据流,因此它们 通常跟随在 一个系统中的 ADC 之后, 这个系统在 不同电源电平的 微处理器 和 FPGA 之间, 或者在具有 共享背板的 接口通信板之间。 在此示例中, 数字隔离器 在 4 至 20 毫安的 环路中保护 MCU 数据线路免受 输出数模转换器的影响。 在查看此处 所示的用例时, 很明显可以 看出,在使用 数字隔离器时, 也需要隔离式电源。 如需了解关于隔离器 电源设计的更多 详细信息,请参阅 高精度实验室视频, 标题为“如何为 数字隔离器设计隔离式 电源”。 现在,我们深入 了解一下数字隔离器。 数字隔离器 如何工作? 这里显示了一个典型 数字隔离器的引脚图。 它包含两个 隔离式电源 VCC1 和 VCC2,两个接地端 GND1 和 GND2, 还有两侧 以各自接地端为基准的 输入和输出引脚。 输入信号 通过发送 IC 进行调制, 然后通过高压电容隔离层 并跨越接合线 到达接收侧 IC。 理想情况下, 施加输入信号时, 数字输入和输出 是相同的。 正如前面提到的, 数字隔离器 最常与采用独立 接地端的隔离式电源 一起使用, 这对于 防止电源的 接地干扰和噪声电流 也很有用。 数字隔离器使用 CMOS 或 TTL 逻辑开关技术, 并具有指定的高电平 或低电平默认输出状态, 可以在数据表的 器件功能模式部分 找到这些状态, 如此处所示。 如表中所示, 如果输入断开 或 BCC1 断开, 则输出 将转换为 逻辑状态高电平。 这一行为称为 失效防护高电平。 另一方面,某些器件 在断开状态下会变成低电平, 称为失效防护低电平。 定义此行为 是为了防止 在电源中断或 电压不足的情况下出现 错误代码。 两个电源 VCC1 和 VCC2 的 数字隔离器的 逻辑电平范围都可以 在 1.8 至 5.5 伏之间, 但有些器件可能支持更大的 电源范围。 由于隔离器基于 两个独立的内部 IC, 因此可以在 数字隔离器的每一侧 使用两个不同的 电源电压。 现在我们已经 大致了解了 数字隔离器在 功能级的工作方式, 我们接下来将讨论 数字隔离器的内部结构 和架构。 电容数字隔离器 是如何构建的? 电容数字隔离器 使用基于 CMOS 技术的 硅基电介质, 包含两个独立的 集成电路 (IC) 芯片: 一个输入电路和 一个输出电路, 通过接合线和 高质量、 耐高压的 模塑化合物相连。 这里显示了数字隔离器的 横截面和 X 射线。 数字隔离器 电路的绝缘体 可以是单个或两个 二氧化硅电容隔离层, 根据设计 可以承受极高的 电压。 基于电容的 隔离器 由半导体行业中 最高电介质强度的 材料制成, 并在受严格控制的 清洁室晶圆厂中 进行制造, 从而使零部件之间的 差异最小。 由于严格控制的 制造环境 和二氧化硅 电介质的质量, 影响隔离性能的 关键因素 主要是技术本身 和设计架构。 电容隔离器通常 采用两种主要的 调制架构: 开关键控 (OOK) 或基于边沿的架构。 这两个名称都描述了 用于触发输出更改的 时序方案。 基于边沿的隔离器 如何工作? 对于基于边沿的 数字隔离器, 如此处所示的 隔离器,数据传输 由指定持续时间的 输入脉冲进行启动。 I/O 通道包含两个 内部数据通道: 一个高频通道, 带宽从 100 千比特/秒 到 25 兆比特/秒, 以及一个低频通道, 涵盖 100 千比特/秒 到直流的 范围。 进入高频通道的 单端输入信号 通过输入端的 反相器门 分解为 差分信号。 然后,电容器电阻网络 将信号分化为 瞬态脉冲, 而高频通道 比较器输出端的 判定逻辑 将测量信号瞬态之间的 持续时间。 如果两个 连续瞬态之间的 持续时间超过特定的 时间限制, 例如在低频信号的 情况下,则判定逻辑 会强制输出多路复用器 从高频通道切换到低频通道。 低频信号通过 内部振荡器的 载波频率进行 脉宽调制, 从而产生能够通过 电容隔离层的 高频信号。 振荡器用于设置 直流 PWM 通道的 时标,使用的 时基通常为 数十纳秒。 然后会以高于 振荡器频率的 可能最小的数据包 对 PWM 通信进行 数据包处理。 根据设计, 基于边沿的隔离器 可以使该振荡器频率 不会反映在 输出频谱中。 在对输入进行调制时, 需要使用一个低通滤波器 消除实际数据中的 高频载波, 然后再将其 传递到输出多路复用器 和输出引脚上, 从而重建 数字输入信号的 电隔离版本。 开关键控数字隔离器 如何工作? 在开关键控 OOK 架构中, 将使用内部 扩频振荡器时钟 对输入的数字比特流 进行调制, 这个时钟的 工作频率 超出器件可用的 数据速率范围。 该时钟频率用于 生成 OOK 信令, 以使输入状态之一通过 传输载波频率来表示, 而另一状态 不通过传输表示。 经过调制的此信号 将耦合到隔离栅, 并以衰减的形式 出现在接收侧, 该接收侧包含用于 放大输入信号的前置放大器 以及包络检波器。 该器件可用作 解调器以重新生成 原始数字模式。 发送和接收 信号调节电路 用于改善 通道的共模抑制, 从而产生更好的 共模瞬态抗扰度, 即 CMTI。 哪种架构最适合 我的设计? 基于边沿的调制方案的 主要优点之一 是比 OOK 架构的 功耗更低。 这是因为基于边沿的 调制隔离器 仅在数据转换 或边沿期间 跨隔离栅传递信号。 因此,这种架构的 功耗大大低于 OOK 架构, OOK 架构会持续采样, 并跨屏蔽层传输 经过调制的输入。 由于这种 连续性的传输, 与基于 PWM 边沿的 架构相比, OOK 架构所需的 功率要大得多。 这些架构 是否有特定的 挑战和优势? 的确,有一些权衡因素。 对于基于边沿的 架构,一旦启动 数据信号,就不会 再对输入和输出状态 进行采样。 这确实会在 电压不足或 数据信号故障的情况下 产生出错风险, 因此需要集成的 刷新电路 来减轻这些条件下的 出错风险, 以便在输出端 强化输入状态。 对于 OOK 方案, 在电源或输入信号 意外变化的情况下 对输入进行连续采样 将不会在输出端 显示任何错误。 尽管基于 边沿的架构 由于其采样方案 而具有特定的功耗优势, 但在前面提到过, 信号调节电路 和开关键控 调制方案 具有固有的噪声 和瞬态响应优势, 同时 CMTI 会高得多, 数据速率也更高。 那么,哪种电容 数字隔离器拓扑 真正适合 您的设计? 在考虑每种架构时, 除了关键的 隔离规格外, 请记住要考虑 功耗与数据速率、 最高可能的 共模抗扰度 以及错误条件管理 等其他重要的 设计注意事项, 以便帮助您确定 最适合自己的方案。 数字隔离器的介绍 到此结束。 我们讨论了 数字隔离器 用于跨隔离栅 传递数字信号, 并且需要隔离式 电源和接地。 电容隔离是使用 硅电介质实现的, 这种材料是业界 电介质强度最高的 绝缘材料。 电容数字隔离器 有两种主要架构: 基于边沿的架构 或 OOK 架构。 基于边沿和基于 OOK 的 电容数字隔离器设计 之间的主要区别 包括输出状态: 基于边沿和基于 OOK 的 数字隔离解决方案 均具有器件数据表中 预定义的 默认输出高电平和 低电平状态。 还包括数据传输: 基于边沿的解决方案 在指定长度的 输入脉冲之后 跨隔离栅 传输数据流, 使用输入流的边沿 构建输出流。 而基于 OOK 的 解决方案,也就是 开关键控解决方案, 通过高频载波 跨隔离栅 传输数据流, 因此改善了 噪声和 CMTI 性能。 最后一个区别是功耗。 基于边沿的架构具有 更低的功耗和更低的数据速率, 而 OOK 架构具有 更高的功耗和更高的数据速率。 高精度实验室主题 “什么是数字隔离器” 到此结束。 谢谢观看。 请尝试完成在线测验 以测试所学到的知识。 问题 1. 哪种绝缘材料 具有最高的 电介质强度? 模塑化合物、聚酰亚胺、 空气还是二氧化硅? 二氧化硅具有 最高的电介质强度, 约为每微米 500 伏。 最常用的 数字隔离器技术 是光学和电感、 电容和光学 或电容和电感。 电容和 电感拓扑 是最常用于 数字隔离的拓扑。 对或错-- 数字隔离器可以 在两个不同的 VCC1 和 VCC2 电源电压下工作。 对。 VCC1 和 VCC2 可以采用 不同的电压值运行, 并且仍然保持 数据表中的性能。 在基于边沿的 数字架构和开关键控 数字架构之间 需要考虑的三个 关键权衡因素是什么? 基于边沿的架构 和电容架构之间 最常见的 权衡因素是 数据速率、功耗 和噪声抑制。 TI 高精度实验室主题 “什么是数字隔离器?” 到此结束。 谢谢观看。 请访问 www.ti.com/precisionlabs, 浏览更多主题。

[音乐播放]

大家好,欢迎观看 TI 高精度实验室视频。

TI 的高精度 实验室视频节目

是面向工程师的 综合在线课程。

这段视频 将介绍有关

数字隔离器的 基本问题。

如需查看更多 视频和主题,

请访问 ti.com/precisionlabs。

什么是数字隔离器?

电隔离是在 存在高压事件时

与人或其他 电路相连的

所有电子器件的

必要保护形式。

在确保人身安全 甚至电子保护的情况下,

高压事件的电压范围 可能从几十伏

到几千伏。

在过去的几十年中, 用于隔离电路的

技术已经 从基于光学的

光耦合器发展到了 基于硅的技术,

其中,数字隔离器 是越来越多

设计人员的首选。

本视频将 主要讨论

基于电容的 数字隔离器。

有关隔离技术的 一般介绍

可以在名为 “什么是电隔离”的

高精度实验室主题中找到。

本高精度实验室主题 将回答以下问题。

什么是数字隔离器?

电容数字隔离器 是如何构建的?

基于边沿的数字隔离器 如何工作?

开关键控 (OOK) 数字隔离器 如何工作?

哪种数字 隔离器架构

最适合我的设计?

让我们开始吧。

什么是数字隔离器?

数字隔离器 是用于隔离

数字信号并 跨隔离栅

传输数字通信的 集成器件。

由于数字隔离器 使用经过

预先数字化处理的 数据流,因此它们

通常跟随在 一个系统中的 ADC 之后,

这个系统在 不同电源电平的

微处理器 和 FPGA 之间,

或者在具有 共享背板的

接口通信板之间。

在此示例中, 数字隔离器

在 4 至 20 毫安的 环路中保护

MCU 数据线路免受 输出数模转换器的影响。

在查看此处 所示的用例时,

很明显可以 看出,在使用

数字隔离器时, 也需要隔离式电源。

如需了解关于隔离器 电源设计的更多

详细信息,请参阅 高精度实验室视频,

标题为“如何为 数字隔离器设计隔离式

电源”。

现在,我们深入 了解一下数字隔离器。

数字隔离器 如何工作?

这里显示了一个典型 数字隔离器的引脚图。

它包含两个 隔离式电源

VCC1 和 VCC2,两个接地端

GND1 和 GND2, 还有两侧

以各自接地端为基准的 输入和输出引脚。

输入信号 通过发送 IC

进行调制, 然后通过高压电容隔离层

并跨越接合线 到达接收侧 IC。

理想情况下, 施加输入信号时,

数字输入和输出 是相同的。

正如前面提到的, 数字隔离器

最常与采用独立 接地端的隔离式电源

一起使用, 这对于

防止电源的 接地干扰和噪声电流

也很有用。

数字隔离器使用 CMOS 或 TTL 逻辑开关技术,

并具有指定的高电平 或低电平默认输出状态,

可以在数据表的 器件功能模式部分

找到这些状态, 如此处所示。

如表中所示, 如果输入断开

或 BCC1 断开, 则输出

将转换为 逻辑状态高电平。

这一行为称为 失效防护高电平。

另一方面,某些器件 在断开状态下会变成低电平,

称为失效防护低电平。

定义此行为 是为了防止

在电源中断或 电压不足的情况下出现

错误代码。

两个电源 VCC1 和 VCC2 的

数字隔离器的 逻辑电平范围都可以

在 1.8 至 5.5 伏之间, 但有些器件可能支持更大的

电源范围。

由于隔离器基于 两个独立的内部 IC,

因此可以在 数字隔离器的每一侧

使用两个不同的 电源电压。

现在我们已经 大致了解了

数字隔离器在 功能级的工作方式,

我们接下来将讨论 数字隔离器的内部结构

和架构。

电容数字隔离器 是如何构建的?

电容数字隔离器 使用基于 CMOS 技术的

硅基电介质, 包含两个独立的

集成电路 (IC) 芯片:

一个输入电路和 一个输出电路,

通过接合线和 高质量、

耐高压的 模塑化合物相连。

这里显示了数字隔离器的 横截面和 X 射线。

数字隔离器 电路的绝缘体

可以是单个或两个 二氧化硅电容隔离层,

根据设计 可以承受极高的

电压。

基于电容的 隔离器

由半导体行业中 最高电介质强度的

材料制成, 并在受严格控制的

清洁室晶圆厂中 进行制造,

从而使零部件之间的 差异最小。

由于严格控制的 制造环境

和二氧化硅 电介质的质量,

影响隔离性能的 关键因素

主要是技术本身 和设计架构。

电容隔离器通常 采用两种主要的

调制架构:

开关键控 (OOK) 或基于边沿的架构。

这两个名称都描述了 用于触发输出更改的

时序方案。

基于边沿的隔离器 如何工作?

对于基于边沿的 数字隔离器,

如此处所示的 隔离器,数据传输

由指定持续时间的 输入脉冲进行启动。

I/O 通道包含两个 内部数据通道:

一个高频通道, 带宽从 100 千比特/秒

到 25 兆比特/秒, 以及一个低频通道,

涵盖 100 千比特/秒 到直流的

范围。

进入高频通道的 单端输入信号

通过输入端的 反相器门

分解为 差分信号。

然后,电容器电阻网络 将信号分化为

瞬态脉冲, 而高频通道

比较器输出端的 判定逻辑

将测量信号瞬态之间的 持续时间。

如果两个 连续瞬态之间的

持续时间超过特定的 时间限制,

例如在低频信号的 情况下,则判定逻辑

会强制输出多路复用器 从高频通道切换到低频通道。

低频信号通过 内部振荡器的

载波频率进行 脉宽调制,

从而产生能够通过 电容隔离层的

高频信号。

振荡器用于设置 直流 PWM 通道的

时标,使用的 时基通常为

数十纳秒。

然后会以高于 振荡器频率的

可能最小的数据包 对 PWM 通信进行

数据包处理。

根据设计, 基于边沿的隔离器

可以使该振荡器频率 不会反映在

输出频谱中。

在对输入进行调制时, 需要使用一个低通滤波器

消除实际数据中的 高频载波,

然后再将其 传递到输出多路复用器

和输出引脚上,

从而重建 数字输入信号的

电隔离版本。

开关键控数字隔离器 如何工作?

在开关键控 OOK 架构中,

将使用内部 扩频振荡器时钟

对输入的数字比特流 进行调制,

这个时钟的 工作频率

超出器件可用的 数据速率范围。

该时钟频率用于 生成 OOK 信令,

以使输入状态之一通过

传输载波频率来表示,

而另一状态 不通过传输表示。

经过调制的此信号 将耦合到隔离栅,

并以衰减的形式 出现在接收侧,

该接收侧包含用于 放大输入信号的前置放大器

以及包络检波器。

该器件可用作 解调器以重新生成

原始数字模式。

发送和接收 信号调节电路

用于改善 通道的共模抑制,

从而产生更好的 共模瞬态抗扰度,

即 CMTI。

哪种架构最适合 我的设计?

基于边沿的调制方案的 主要优点之一

是比 OOK 架构的 功耗更低。

这是因为基于边沿的 调制隔离器

仅在数据转换 或边沿期间

跨隔离栅传递信号。

因此,这种架构的 功耗大大低于

OOK 架构, OOK 架构会持续采样,

并跨屏蔽层传输 经过调制的输入。

由于这种 连续性的传输,

与基于 PWM 边沿的 架构相比,

OOK 架构所需的 功率要大得多。

这些架构 是否有特定的

挑战和优势?

的确,有一些权衡因素。

对于基于边沿的 架构,一旦启动

数据信号,就不会 再对输入和输出状态

进行采样。

这确实会在 电压不足或

数据信号故障的情况下 产生出错风险,

因此需要集成的 刷新电路

来减轻这些条件下的 出错风险,

以便在输出端 强化输入状态。

对于 OOK 方案, 在电源或输入信号

意外变化的情况下 对输入进行连续采样

将不会在输出端 显示任何错误。

尽管基于 边沿的架构

由于其采样方案 而具有特定的功耗优势,

但在前面提到过, 信号调节电路

和开关键控 调制方案

具有固有的噪声 和瞬态响应优势,

同时 CMTI 会高得多,

数据速率也更高。

那么,哪种电容 数字隔离器拓扑

真正适合 您的设计?

在考虑每种架构时, 除了关键的

隔离规格外, 请记住要考虑

功耗与数据速率、 最高可能的

共模抗扰度 以及错误条件管理

等其他重要的 设计注意事项,

以便帮助您确定 最适合自己的方案。

数字隔离器的介绍 到此结束。

我们讨论了 数字隔离器

用于跨隔离栅 传递数字信号,

并且需要隔离式 电源和接地。

电容隔离是使用 硅电介质实现的,

这种材料是业界 电介质强度最高的

绝缘材料。

电容数字隔离器 有两种主要架构:

基于边沿的架构 或 OOK 架构。

基于边沿和基于 OOK 的 电容数字隔离器设计

之间的主要区别 包括输出状态:

基于边沿和基于 OOK 的 数字隔离解决方案

均具有器件数据表中 预定义的

默认输出高电平和 低电平状态。

还包括数据传输: 基于边沿的解决方案

在指定长度的 输入脉冲之后

跨隔离栅 传输数据流,

使用输入流的边沿 构建输出流。

而基于 OOK 的 解决方案,也就是

开关键控解决方案, 通过高频载波

跨隔离栅 传输数据流,

因此改善了 噪声和 CMTI 性能。

最后一个区别是功耗。

基于边沿的架构具有 更低的功耗和更低的数据速率,

而 OOK 架构具有 更高的功耗和更高的数据速率。

高精度实验室主题 “什么是数字隔离器”

到此结束。

谢谢观看。

请尝试完成在线测验 以测试所学到的知识。

问题 1.

哪种绝缘材料 具有最高的

电介质强度?

模塑化合物、聚酰亚胺、 空气还是二氧化硅?

二氧化硅具有 最高的电介质强度,

约为每微米 500 伏。

最常用的 数字隔离器技术

是光学和电感、 电容和光学

或电容和电感。

电容和 电感拓扑

是最常用于 数字隔离的拓扑。

对或错--

数字隔离器可以 在两个不同的

VCC1 和 VCC2 电源电压下工作。

对。

VCC1 和 VCC2 可以采用 不同的电压值运行,

并且仍然保持 数据表中的性能。

在基于边沿的 数字架构和开关键控

数字架构之间 需要考虑的三个

关键权衡因素是什么?

基于边沿的架构 和电容架构之间

最常见的 权衡因素是

数据速率、功耗 和噪声抑制。

TI 高精度实验室主题 “什么是数字隔离器?”

到此结束。

谢谢观看。

请访问 www.ti.com/precisionlabs, 浏览更多主题。

[音乐播放] 大家好,欢迎观看 TI 高精度实验室视频。 TI 的高精度 实验室视频节目 是面向工程师的 综合在线课程。 这段视频 将介绍有关 数字隔离器的 基本问题。 如需查看更多 视频和主题, 请访问 ti.com/precisionlabs。 什么是数字隔离器? 电隔离是在 存在高压事件时 与人或其他 电路相连的 所有电子器件的 必要保护形式。 在确保人身安全 甚至电子保护的情况下, 高压事件的电压范围 可能从几十伏 到几千伏。 在过去的几十年中, 用于隔离电路的 技术已经 从基于光学的 光耦合器发展到了 基于硅的技术, 其中,数字隔离器 是越来越多 设计人员的首选。 本视频将 主要讨论 基于电容的 数字隔离器。 有关隔离技术的 一般介绍 可以在名为 “什么是电隔离”的 高精度实验室主题中找到。 本高精度实验室主题 将回答以下问题。 什么是数字隔离器? 电容数字隔离器 是如何构建的? 基于边沿的数字隔离器 如何工作? 开关键控 (OOK) 数字隔离器 如何工作? 哪种数字 隔离器架构 最适合我的设计? 让我们开始吧。 什么是数字隔离器? 数字隔离器 是用于隔离 数字信号并 跨隔离栅 传输数字通信的 集成器件。 由于数字隔离器 使用经过 预先数字化处理的 数据流,因此它们 通常跟随在 一个系统中的 ADC 之后, 这个系统在 不同电源电平的 微处理器 和 FPGA 之间, 或者在具有 共享背板的 接口通信板之间。 在此示例中, 数字隔离器 在 4 至 20 毫安的 环路中保护 MCU 数据线路免受 输出数模转换器的影响。 在查看此处 所示的用例时, 很明显可以 看出,在使用 数字隔离器时, 也需要隔离式电源。 如需了解关于隔离器 电源设计的更多 详细信息,请参阅 高精度实验室视频, 标题为“如何为 数字隔离器设计隔离式 电源”。 现在,我们深入 了解一下数字隔离器。 数字隔离器 如何工作? 这里显示了一个典型 数字隔离器的引脚图。 它包含两个 隔离式电源 VCC1 和 VCC2,两个接地端 GND1 和 GND2, 还有两侧 以各自接地端为基准的 输入和输出引脚。 输入信号 通过发送 IC 进行调制, 然后通过高压电容隔离层 并跨越接合线 到达接收侧 IC。 理想情况下, 施加输入信号时, 数字输入和输出 是相同的。 正如前面提到的, 数字隔离器 最常与采用独立 接地端的隔离式电源 一起使用, 这对于 防止电源的 接地干扰和噪声电流 也很有用。 数字隔离器使用 CMOS 或 TTL 逻辑开关技术, 并具有指定的高电平 或低电平默认输出状态, 可以在数据表的 器件功能模式部分 找到这些状态, 如此处所示。 如表中所示, 如果输入断开 或 BCC1 断开, 则输出 将转换为 逻辑状态高电平。 这一行为称为 失效防护高电平。 另一方面,某些器件 在断开状态下会变成低电平, 称为失效防护低电平。 定义此行为 是为了防止 在电源中断或 电压不足的情况下出现 错误代码。 两个电源 VCC1 和 VCC2 的 数字隔离器的 逻辑电平范围都可以 在 1.8 至 5.5 伏之间, 但有些器件可能支持更大的 电源范围。 由于隔离器基于 两个独立的内部 IC, 因此可以在 数字隔离器的每一侧 使用两个不同的 电源电压。 现在我们已经 大致了解了 数字隔离器在 功能级的工作方式, 我们接下来将讨论 数字隔离器的内部结构 和架构。 电容数字隔离器 是如何构建的? 电容数字隔离器 使用基于 CMOS 技术的 硅基电介质, 包含两个独立的 集成电路 (IC) 芯片: 一个输入电路和 一个输出电路, 通过接合线和 高质量、 耐高压的 模塑化合物相连。 这里显示了数字隔离器的 横截面和 X 射线。 数字隔离器 电路的绝缘体 可以是单个或两个 二氧化硅电容隔离层, 根据设计 可以承受极高的 电压。 基于电容的 隔离器 由半导体行业中 最高电介质强度的 材料制成, 并在受严格控制的 清洁室晶圆厂中 进行制造, 从而使零部件之间的 差异最小。 由于严格控制的 制造环境 和二氧化硅 电介质的质量, 影响隔离性能的 关键因素 主要是技术本身 和设计架构。 电容隔离器通常 采用两种主要的 调制架构: 开关键控 (OOK) 或基于边沿的架构。 这两个名称都描述了 用于触发输出更改的 时序方案。 基于边沿的隔离器 如何工作? 对于基于边沿的 数字隔离器, 如此处所示的 隔离器,数据传输 由指定持续时间的 输入脉冲进行启动。 I/O 通道包含两个 内部数据通道: 一个高频通道, 带宽从 100 千比特/秒 到 25 兆比特/秒, 以及一个低频通道, 涵盖 100 千比特/秒 到直流的 范围。 进入高频通道的 单端输入信号 通过输入端的 反相器门 分解为 差分信号。 然后,电容器电阻网络 将信号分化为 瞬态脉冲, 而高频通道 比较器输出端的 判定逻辑 将测量信号瞬态之间的 持续时间。 如果两个 连续瞬态之间的 持续时间超过特定的 时间限制, 例如在低频信号的 情况下,则判定逻辑 会强制输出多路复用器 从高频通道切换到低频通道。 低频信号通过 内部振荡器的 载波频率进行 脉宽调制, 从而产生能够通过 电容隔离层的 高频信号。 振荡器用于设置 直流 PWM 通道的 时标,使用的 时基通常为 数十纳秒。 然后会以高于 振荡器频率的 可能最小的数据包 对 PWM 通信进行 数据包处理。 根据设计, 基于边沿的隔离器 可以使该振荡器频率 不会反映在 输出频谱中。 在对输入进行调制时, 需要使用一个低通滤波器 消除实际数据中的 高频载波, 然后再将其 传递到输出多路复用器 和输出引脚上, 从而重建 数字输入信号的 电隔离版本。 开关键控数字隔离器 如何工作? 在开关键控 OOK 架构中, 将使用内部 扩频振荡器时钟 对输入的数字比特流 进行调制, 这个时钟的 工作频率 超出器件可用的 数据速率范围。 该时钟频率用于 生成 OOK 信令, 以使输入状态之一通过 传输载波频率来表示, 而另一状态 不通过传输表示。 经过调制的此信号 将耦合到隔离栅, 并以衰减的形式 出现在接收侧, 该接收侧包含用于 放大输入信号的前置放大器 以及包络检波器。 该器件可用作 解调器以重新生成 原始数字模式。 发送和接收 信号调节电路 用于改善 通道的共模抑制, 从而产生更好的 共模瞬态抗扰度, 即 CMTI。 哪种架构最适合 我的设计? 基于边沿的调制方案的 主要优点之一 是比 OOK 架构的 功耗更低。 这是因为基于边沿的 调制隔离器 仅在数据转换 或边沿期间 跨隔离栅传递信号。 因此,这种架构的 功耗大大低于 OOK 架构, OOK 架构会持续采样, 并跨屏蔽层传输 经过调制的输入。 由于这种 连续性的传输, 与基于 PWM 边沿的 架构相比, OOK 架构所需的 功率要大得多。 这些架构 是否有特定的 挑战和优势? 的确,有一些权衡因素。 对于基于边沿的 架构,一旦启动 数据信号,就不会 再对输入和输出状态 进行采样。 这确实会在 电压不足或 数据信号故障的情况下 产生出错风险, 因此需要集成的 刷新电路 来减轻这些条件下的 出错风险, 以便在输出端 强化输入状态。 对于 OOK 方案, 在电源或输入信号 意外变化的情况下 对输入进行连续采样 将不会在输出端 显示任何错误。 尽管基于 边沿的架构 由于其采样方案 而具有特定的功耗优势, 但在前面提到过, 信号调节电路 和开关键控 调制方案 具有固有的噪声 和瞬态响应优势, 同时 CMTI 会高得多, 数据速率也更高。 那么,哪种电容 数字隔离器拓扑 真正适合 您的设计? 在考虑每种架构时, 除了关键的 隔离规格外, 请记住要考虑 功耗与数据速率、 最高可能的 共模抗扰度 以及错误条件管理 等其他重要的 设计注意事项, 以便帮助您确定 最适合自己的方案。 数字隔离器的介绍 到此结束。 我们讨论了 数字隔离器 用于跨隔离栅 传递数字信号, 并且需要隔离式 电源和接地。 电容隔离是使用 硅电介质实现的, 这种材料是业界 电介质强度最高的 绝缘材料。 电容数字隔离器 有两种主要架构: 基于边沿的架构 或 OOK 架构。 基于边沿和基于 OOK 的 电容数字隔离器设计 之间的主要区别 包括输出状态: 基于边沿和基于 OOK 的 数字隔离解决方案 均具有器件数据表中 预定义的 默认输出高电平和 低电平状态。 还包括数据传输: 基于边沿的解决方案 在指定长度的 输入脉冲之后 跨隔离栅 传输数据流, 使用输入流的边沿 构建输出流。 而基于 OOK 的 解决方案,也就是 开关键控解决方案, 通过高频载波 跨隔离栅 传输数据流, 因此改善了 噪声和 CMTI 性能。 最后一个区别是功耗。 基于边沿的架构具有 更低的功耗和更低的数据速率, 而 OOK 架构具有 更高的功耗和更高的数据速率。 高精度实验室主题 “什么是数字隔离器” 到此结束。 谢谢观看。 请尝试完成在线测验 以测试所学到的知识。 问题 1. 哪种绝缘材料 具有最高的 电介质强度? 模塑化合物、聚酰亚胺、 空气还是二氧化硅? 二氧化硅具有 最高的电介质强度, 约为每微米 500 伏。 最常用的 数字隔离器技术 是光学和电感、 电容和光学 或电容和电感。 电容和 电感拓扑 是最常用于 数字隔离的拓扑。 对或错-- 数字隔离器可以 在两个不同的 VCC1 和 VCC2 电源电压下工作。 对。 VCC1 和 VCC2 可以采用 不同的电压值运行, 并且仍然保持 数据表中的性能。 在基于边沿的 数字架构和开关键控 数字架构之间 需要考虑的三个 关键权衡因素是什么? 基于边沿的架构 和电容架构之间 最常见的 权衡因素是 数据速率、功耗 和噪声抑制。 TI 高精度实验室主题 “什么是数字隔离器?” 到此结束。 谢谢观看。 请访问 www.ti.com/precisionlabs, 浏览更多主题。

[音乐播放]

大家好,欢迎观看 TI 高精度实验室视频。

TI 的高精度 实验室视频节目

是面向工程师的 综合在线课程。

这段视频 将介绍有关

数字隔离器的 基本问题。

如需查看更多 视频和主题,

请访问 ti.com/precisionlabs。

什么是数字隔离器?

电隔离是在 存在高压事件时

与人或其他 电路相连的

所有电子器件的

必要保护形式。

在确保人身安全 甚至电子保护的情况下,

高压事件的电压范围 可能从几十伏

到几千伏。

在过去的几十年中, 用于隔离电路的

技术已经 从基于光学的

光耦合器发展到了 基于硅的技术,

其中,数字隔离器 是越来越多

设计人员的首选。

本视频将 主要讨论

基于电容的 数字隔离器。

有关隔离技术的 一般介绍

可以在名为 “什么是电隔离”的

高精度实验室主题中找到。

本高精度实验室主题 将回答以下问题。

什么是数字隔离器?

电容数字隔离器 是如何构建的?

基于边沿的数字隔离器 如何工作?

开关键控 (OOK) 数字隔离器 如何工作?

哪种数字 隔离器架构

最适合我的设计?

让我们开始吧。

什么是数字隔离器?

数字隔离器 是用于隔离

数字信号并 跨隔离栅

传输数字通信的 集成器件。

由于数字隔离器 使用经过

预先数字化处理的 数据流,因此它们

通常跟随在 一个系统中的 ADC 之后,

这个系统在 不同电源电平的

微处理器 和 FPGA 之间,

或者在具有 共享背板的

接口通信板之间。

在此示例中, 数字隔离器

在 4 至 20 毫安的 环路中保护

MCU 数据线路免受 输出数模转换器的影响。

在查看此处 所示的用例时,

很明显可以 看出,在使用

数字隔离器时, 也需要隔离式电源。

如需了解关于隔离器 电源设计的更多

详细信息,请参阅 高精度实验室视频,

标题为“如何为 数字隔离器设计隔离式

电源”。

现在,我们深入 了解一下数字隔离器。

数字隔离器 如何工作?

这里显示了一个典型 数字隔离器的引脚图。

它包含两个 隔离式电源

VCC1 和 VCC2,两个接地端

GND1 和 GND2, 还有两侧

以各自接地端为基准的 输入和输出引脚。

输入信号 通过发送 IC

进行调制, 然后通过高压电容隔离层

并跨越接合线 到达接收侧 IC。

理想情况下, 施加输入信号时,

数字输入和输出 是相同的。

正如前面提到的, 数字隔离器

最常与采用独立 接地端的隔离式电源

一起使用, 这对于

防止电源的 接地干扰和噪声电流

也很有用。

数字隔离器使用 CMOS 或 TTL 逻辑开关技术,

并具有指定的高电平 或低电平默认输出状态,

可以在数据表的 器件功能模式部分

找到这些状态, 如此处所示。

如表中所示, 如果输入断开

或 BCC1 断开, 则输出

将转换为 逻辑状态高电平。

这一行为称为 失效防护高电平。

另一方面,某些器件 在断开状态下会变成低电平,

称为失效防护低电平。

定义此行为 是为了防止

在电源中断或 电压不足的情况下出现

错误代码。

两个电源 VCC1 和 VCC2 的

数字隔离器的 逻辑电平范围都可以

在 1.8 至 5.5 伏之间, 但有些器件可能支持更大的

电源范围。

由于隔离器基于 两个独立的内部 IC,

因此可以在 数字隔离器的每一侧

使用两个不同的 电源电压。

现在我们已经 大致了解了

数字隔离器在 功能级的工作方式,

我们接下来将讨论 数字隔离器的内部结构

和架构。

电容数字隔离器 是如何构建的?

电容数字隔离器 使用基于 CMOS 技术的

硅基电介质, 包含两个独立的

集成电路 (IC) 芯片:

一个输入电路和 一个输出电路,

通过接合线和 高质量、

耐高压的 模塑化合物相连。

这里显示了数字隔离器的 横截面和 X 射线。

数字隔离器 电路的绝缘体

可以是单个或两个 二氧化硅电容隔离层,

根据设计 可以承受极高的

电压。

基于电容的 隔离器

由半导体行业中 最高电介质强度的

材料制成, 并在受严格控制的

清洁室晶圆厂中 进行制造,

从而使零部件之间的 差异最小。

由于严格控制的 制造环境

和二氧化硅 电介质的质量,

影响隔离性能的 关键因素

主要是技术本身 和设计架构。

电容隔离器通常 采用两种主要的

调制架构:

开关键控 (OOK) 或基于边沿的架构。

这两个名称都描述了 用于触发输出更改的

时序方案。

基于边沿的隔离器 如何工作?

对于基于边沿的 数字隔离器,

如此处所示的 隔离器,数据传输

由指定持续时间的 输入脉冲进行启动。

I/O 通道包含两个 内部数据通道:

一个高频通道, 带宽从 100 千比特/秒

到 25 兆比特/秒, 以及一个低频通道,

涵盖 100 千比特/秒 到直流的

范围。

进入高频通道的 单端输入信号

通过输入端的 反相器门

分解为 差分信号。

然后,电容器电阻网络 将信号分化为

瞬态脉冲, 而高频通道

比较器输出端的 判定逻辑

将测量信号瞬态之间的 持续时间。

如果两个 连续瞬态之间的

持续时间超过特定的 时间限制,

例如在低频信号的 情况下,则判定逻辑

会强制输出多路复用器 从高频通道切换到低频通道。

低频信号通过 内部振荡器的

载波频率进行 脉宽调制,

从而产生能够通过 电容隔离层的

高频信号。

振荡器用于设置 直流 PWM 通道的

时标,使用的 时基通常为

数十纳秒。

然后会以高于 振荡器频率的

可能最小的数据包 对 PWM 通信进行

数据包处理。

根据设计, 基于边沿的隔离器

可以使该振荡器频率 不会反映在

输出频谱中。

在对输入进行调制时, 需要使用一个低通滤波器

消除实际数据中的 高频载波,

然后再将其 传递到输出多路复用器

和输出引脚上,

从而重建 数字输入信号的

电隔离版本。

开关键控数字隔离器 如何工作?

在开关键控 OOK 架构中,

将使用内部 扩频振荡器时钟

对输入的数字比特流 进行调制,

这个时钟的 工作频率

超出器件可用的 数据速率范围。

该时钟频率用于 生成 OOK 信令,

以使输入状态之一通过

传输载波频率来表示,

而另一状态 不通过传输表示。

经过调制的此信号 将耦合到隔离栅,

并以衰减的形式 出现在接收侧,

该接收侧包含用于 放大输入信号的前置放大器

以及包络检波器。

该器件可用作 解调器以重新生成

原始数字模式。

发送和接收 信号调节电路

用于改善 通道的共模抑制,

从而产生更好的 共模瞬态抗扰度,

即 CMTI。

哪种架构最适合 我的设计?

基于边沿的调制方案的 主要优点之一

是比 OOK 架构的 功耗更低。

这是因为基于边沿的 调制隔离器

仅在数据转换 或边沿期间

跨隔离栅传递信号。

因此,这种架构的 功耗大大低于

OOK 架构, OOK 架构会持续采样,

并跨屏蔽层传输 经过调制的输入。

由于这种 连续性的传输,

与基于 PWM 边沿的 架构相比,

OOK 架构所需的 功率要大得多。

这些架构 是否有特定的

挑战和优势?

的确,有一些权衡因素。

对于基于边沿的 架构,一旦启动

数据信号,就不会 再对输入和输出状态

进行采样。

这确实会在 电压不足或

数据信号故障的情况下 产生出错风险,

因此需要集成的 刷新电路

来减轻这些条件下的 出错风险,

以便在输出端 强化输入状态。

对于 OOK 方案, 在电源或输入信号

意外变化的情况下 对输入进行连续采样

将不会在输出端 显示任何错误。

尽管基于 边沿的架构

由于其采样方案 而具有特定的功耗优势,

但在前面提到过, 信号调节电路

和开关键控 调制方案

具有固有的噪声 和瞬态响应优势,

同时 CMTI 会高得多,

数据速率也更高。

那么,哪种电容 数字隔离器拓扑

真正适合 您的设计?

在考虑每种架构时, 除了关键的

隔离规格外, 请记住要考虑

功耗与数据速率、 最高可能的

共模抗扰度 以及错误条件管理

等其他重要的 设计注意事项,

以便帮助您确定 最适合自己的方案。

数字隔离器的介绍 到此结束。

我们讨论了 数字隔离器

用于跨隔离栅 传递数字信号,

并且需要隔离式 电源和接地。

电容隔离是使用 硅电介质实现的,

这种材料是业界 电介质强度最高的

绝缘材料。

电容数字隔离器 有两种主要架构:

基于边沿的架构 或 OOK 架构。

基于边沿和基于 OOK 的 电容数字隔离器设计

之间的主要区别 包括输出状态:

基于边沿和基于 OOK 的 数字隔离解决方案

均具有器件数据表中 预定义的

默认输出高电平和 低电平状态。

还包括数据传输: 基于边沿的解决方案

在指定长度的 输入脉冲之后

跨隔离栅 传输数据流,

使用输入流的边沿 构建输出流。

而基于 OOK 的 解决方案,也就是

开关键控解决方案, 通过高频载波

跨隔离栅 传输数据流,

因此改善了 噪声和 CMTI 性能。

最后一个区别是功耗。

基于边沿的架构具有 更低的功耗和更低的数据速率,

而 OOK 架构具有 更高的功耗和更高的数据速率。

高精度实验室主题 “什么是数字隔离器”

到此结束。

谢谢观看。

请尝试完成在线测验 以测试所学到的知识。

问题 1.

哪种绝缘材料 具有最高的

电介质强度?

模塑化合物、聚酰亚胺、 空气还是二氧化硅?

二氧化硅具有 最高的电介质强度,

约为每微米 500 伏。

最常用的 数字隔离器技术

是光学和电感、 电容和光学

或电容和电感。

电容和 电感拓扑

是最常用于 数字隔离的拓扑。

对或错--

数字隔离器可以 在两个不同的

VCC1 和 VCC2 电源电压下工作。

对。

VCC1 和 VCC2 可以采用 不同的电压值运行,

并且仍然保持 数据表中的性能。

在基于边沿的 数字架构和开关键控

数字架构之间 需要考虑的三个

关键权衡因素是什么?

基于边沿的架构 和电容架构之间

最常见的 权衡因素是

数据速率、功耗 和噪声抑制。

TI 高精度实验室主题 “什么是数字隔离器?”

到此结束。

谢谢观看。

请访问 www.ti.com/precisionlabs, 浏览更多主题。

手机看

扫码用手机观看

视频简介

视频简介

2. TI 高精度实验室-隔离:什么是数字隔离器?

所属课程:TI 高精度实验室 - 隔离介绍

发布时间:2020.08.11

视频集数:15

本节视频时长:00:12:11

培训视频的这一部分将讨论什么是隔离,隔离器的三种类型以及它们如何实现隔离。本课程讲解隔离的基础知识,包括许多不同的TI隔离产品使用的技术的基础。然后,通过学习最常见的隔离参数(对系统设计非常重要)并选择正确的隔离器产品,在上一课的基础上进行构建。这些参数描述了隔离器要处理的最大电压应力,甚至是基本隔离器和增强型隔离器之间的差异。

未学习 1. TI 高精度实验室-隔离:什么是电流隔离?

未学习 1. TI 高精度实验室-隔离:什么是电流隔离?

未学习 2. TI 高精度实验室-隔离:什么是数字隔离器?

未学习 2. TI 高精度实验室-隔离:什么是数字隔离器?

未学习 3. TI 高精度实验室-隔离:什么是隔离数字输入?

未学习 3. TI 高精度实验室-隔离:什么是隔离数字输入?

未学习 4. TI 高精度实验室-隔离:数字隔离器的隔离电源

未学习 4. TI 高精度实验室-隔离:数字隔离器的隔离电源

未学习 5. TI 高精度实验室-隔离:隔离标准和认证简介

未学习 5. TI 高精度实验室-隔离:隔离标准和认证简介

未学习 6. TI 高精度实验室-隔离:什么是爬电距离和电气间隙?

未学习 6. TI 高精度实验室-隔离:什么是爬电距离和电气间隙?

未学习 7. TI 高精度实验室-隔离:什么是数字隔离器的CMTI?

未学习 7. TI 高精度实验室-隔离:什么是数字隔离器的CMTI?

未学习 8. TI 高精度实验室-隔离:隔离测试简介

未学习 8. TI 高精度实验室-隔离:隔离测试简介

未学习 (中文)什么是电流隔离?

未学习 (中文)什么是电流隔离?

未学习 (中文)什么是数字隔离器?

未学习 (中文)什么是数字隔离器?

未学习 (中文)什么是隔离数字输入?

未学习 (中文)什么是隔离数字输入?

未学习 (中文)隔离标准和认证简介

未学习 (中文)隔离标准和认证简介

未学习 (中文)数字隔离器的 CMTI 是什么?

未学习 (中文)数字隔离器的 CMTI 是什么?

未学习 (中文)隔离的 EMC 简介

未学习 (中文)隔离的 EMC 简介

未学习 (中文)什么是功能隔离?

未学习 (中文)什么是功能隔离?

视频简介

视频简介