高速Transimpedence放大器设计流程

Loading the player...

将在30s后自动为您播放下一课程

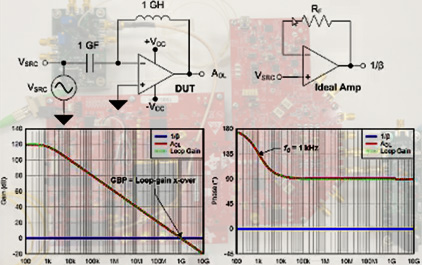

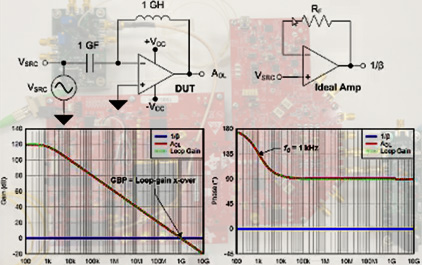

大家好! 我叫 Samir Cherian, 是德州仪器 (TI) 高速放大器团队的 应用工程师。 今天,我将展示 有关如何 优化互阻抗放大器 以用于高速应用的 定性分析。 互阻抗 放大器 用于转换来自 光学传感器的 输出电流,例如, 将光电二极管变为电压。 TIA 的概念简单。 它们依据欧姆定律在运算放大器中 使用反馈电阻器 将电流 转为电压。 但是,当尝试 最大程度提高 高速系统的 性能时, 分析会变得相当复杂。 在本演示中, 我将介绍理论设计 概念, 然后在 Spice 环境中 应用这些概念。 我们将在本演示中 着重介绍三个领域 - 介绍影响其 频率响应和形状的 TIA 和 因素。 我将深入介绍 可能影响放大器稳定性的 每个因素。 然后,我将最终 检查影响 TIA 中 总体噪声的 单独元素。 您还将在下面 找到两个链接。 第一个链接是对 基础放大器稳定性的回顾。 第二个链接是 应用手册, 它提供了 对互阻抗放大器 稳定性的 详细量化分析。 检测和放大 来自光电二极管的 高速小电流 可具有较高的设计难度。 光电二极管、 放大器以及印刷电路板的 寄生电容 相互之间 以及与反馈电阻之间 相互作用, 以修改 TIA 的 频率响应形状。 该图显示了 影响放大器 稳定性的 主要元素。 光电二极管具有 可从 1 皮法拉至 数百皮法拉不等的 寄生电容, 具体取决于其敏感度。 此外,运算放大器具有 共模和差分输入电容, 同样也需要 加以考虑。 此外,PCB 也具有一些 寄生电容。 在本演示中, 我将三个电容 合为一个单输入电容, 记为总计 C。 除在放大器的 输入节点上的 电容器存在寄生效应外, 在 PCB 以及 反馈电阻器封装中 也有反馈寄生效应, 稍后, 我将讨论 与射频 同时增加的 物理电容器。 TIA 的带宽由 三个关键元素 确定。 首选是总输入 电容 - 这包括光电二极管电容、 运算放大器输入电容, 以及任何 寄生 PCB 电容。 其次是符合期望的互阻抗增益。 最后,同样还有运算 放大器的带宽积。 运算放大器的 带宽增益越高, 产生的闭环带宽 互阻抗带宽就越高。 以上三个因素 相互关联。 对于选定的 特定运算放大器, 以互阻抗 增益为目标 就会设定 最大带宽, 或反之,以该带宽为目标 就会将设定最大增益。 我将使用 TINA-Spice 仿真软件展示 TIA 的 基础构建块以及 不同的组件如何影响 TIA 的稳定性和噪声。 在本演示中, 我将着重 介绍针对目标 互阻抗增益 实现 65° 相补角的 巴特沃斯型响应形状, 然后,我将推导 闭环响应 和噪声。 当尝试选择互阻抗 设计的运算放大器时, 务必了解三件事, 光电二极管 电容、所需的 互阻抗 增益,以及所需的 闭环带宽。 放大器的稳定性 取决于其环路增益, 其定义为 开环增益 AOL 与 反馈因子 β 的乘积。 运算放大器的 反馈因子是 其噪声增益的倒数。 为仿真 环路增益, 我将使用 图中所示的 两个电路配置。 DUT 配置用于 提取运算放大器的 开路增益幅度和相位。 图中显示的 大电容器和电感器 将配置开路中的 运算放大器 以提取其 AOL。 理想的 放大器配置 使用理想的运算放大器 提取噪声增益, 这是围绕运算 放大器无源元件的 功能。 在第一种情况下, 我将假定 DUT 没有任何输入电容 和理想的光电二极管, 没有寄生电容。 在此案例中, 没有任何输入和反馈 电容器, 放大器采用单元增益缓冲器 配置。 噪声增益的 幅度在整个频率中 并没有扁平为零 dB, 其相位也是如此。 以 dB 表示的 环路增益是 AOL 与 β 之和。 由于 β 是 0dB, 环路增益将跟踪开环增益。 如要确定 相补角, 查找 AOL 曲线 与 β 曲线相交处的 频率。 该点可称为 回路增益交叉点。 在此案例中, 环路增益交叉点 出现在 运算放大器的 增益带宽积,即 1GHz。 现在,找到交叉频率处 环路增益的 相位。 在本例中,它为 90°, 因为系统是 单极性放大器。 相补角为 180° 减去 90° 相移, 由于其为单极性, 这可产生 90° 的 相补角。 放大器 因此稳定。 现在让我们考虑 光电二极管和运算放大器的 输入电容。 我将假定总输入 电容为 10 皮法, 并且目标互阻抗 增益为 159 千欧姆。 开环增益 曲线将保持为 上一例中的 曲线不变, 如红色曲线所示。 出于噪音增益 考虑, 10 皮法拉 输入电容器 已添加至理想放大器的 反向终端处。 现在,让我们看看跨频率 噪声增益行为。 在低频时, 10 皮法拉电容 阻抗 将极高, 并因此将被 视为开路。 在低频时, 放大器 将如前用作 空增益缓冲器, 此增益幅度为零 dB。 随着频率上升, 输出电容器的阻抗 将开始降低。 在 1/2π RFC(总计)的 频率下, 即 100KHz 频率下, 阻抗电容器 等于反馈 电阻器的值。 这是噪声增益 曲线上的零。 在零频率以上, 噪声增益 将开始以 20 dB/十倍频程的速率增加。 总相位 会发生变化, 因为它将是 0° 至 90°。 现在,让我们考虑 环路增益交叉。 我们使开环增益 降低 20dB/十倍频程。 它将在 1GHz 处 经过 0db 线。 与此类似, 噪声增益曲线 将开始在 100KHz 处 以 20dB/十倍频程的速率增加。 交点 即环路增益交叉点, 它是 100KHz 处 零频率与 1GHz 处放大器 增益带宽积的 几何平均数。 此环路增益因此 将在 10MHz 交叉。 请记住,噪声增益中的零 是 β 中的极。 产生的环路增益 确实有双极响应。 现在我们需要了解一下幅度。 噪声增益 始于 100KHz, 并以 20 dB/十倍频程的 速率增加, 而 AOL 以 -20 dB/十倍 频程的速度降低。 环路增益在 环路增益交叉频率处 具有 -40 dB 的 接近率。 这通常指示存在 潜在的不稳定性。 现在,让我们来看看 环路增益的相位。 正如此前的情况, 1KHz 的主极点 将影响 90° 的总相移, 该相移在 10KHz 处结束。 但是,现在由于 在 100KHz 处为零, 相位将 持续减少。 在 1MHz 时, 总相移 接近 180°。 请记住,在此之前, 环路增益交叉处 为 10MHz。 在该频率处, 围绕反馈环路的 总相移 是 180°, 这表示产生的 相补角是 0°, 并且 TIA 现在 将变得不稳定。 现在,让我们考虑 TIA 的环路增益响应 对反馈电容的影响。 我将首先 假定反馈电容 为 141 飞法拉。 我将稍后 展示, 我是如何针对反馈电容 提出此类值。 检查整个频率的 噪声增益形状。 如前所述, 噪声增益 将在 低频时扁平。 由于反馈电容 远小于 输入电容, 它将不会影响 零频率的位置。 但是, 在 1/2π RFCF 的频率下, 即 10 MHz 频率下, 反馈电阻 与反馈电容的阻抗 将变为相等。 在较高频率处, 由于 Rf 与 Cf 并联, RF 不再会 影响噪声增益。 因此,产生的 噪声增益 将由总计为 C 的 输入电容以及 反馈电容 CF 确定。 由于这两个电容器的 阻抗幅度 将以相同 频率变化, 噪声增益将变平, 如图中所示。 反馈电容 因此具有 在噪声增益中插入池的效果, 这将继而纠正 环路增益曲线上 回收相位。 如图中所示, 环路增益交叉点 将在接近极点频率的 位置处出现, 大约 10MHz。 现在,让我们来看看 相位响应。 比极点频率 低十倍频程, 由于存在反馈电容, 环路增益相 将开始以 45 度/十倍频程的速率增加。 在 10MHz 处出现 环路增益交叉时, 覆盖足够 相位的环路增益 可提供大约 65° 的相比角, 因此为我们带来 巴特沃斯型响应。 将反馈电容 设为远低于 该 141 飞法拉的值 将进一步 推动 极点频率。 这将导致 相补角不够理想。 与此类似, 将反馈电容 提高到远高于 141 飞法拉的值, 这将使极点频率 更接近零频率。 这将导致 过阻尼响应。 但是,闭环 带宽 将比过去 低得多。 结果变为, 对于巴特沃斯型响应, 相补角 为 65°, 您必须 根据此方程式 将反馈电容 设为相等, 其中 f -3 dB 是 由运算放大器增益带宽与 噪声增益中 零频率的几何平均数 得出。 我就是这样 得出 141 飞法拉的 反馈电容值。 在此幻灯片中, 我仿真 互阻抗放大器 在我更改反馈电容值后的 环路增益和 闭环带宽。 将反馈 电容值 提高到 280 飞法拉 会将极点频率拉至低值, 导致 相补角和 过阻尼响应增加。 当反馈电容器的 值降低时, 反之亦然。 极点在频率方面 会进一步外推, 从而缩减相补角 和频率响应 将显示超额峰值。 用于仿真闭环 互阻抗增益的电路 如此处所示。 最后, 我总结了 变更反馈 电容值的结果。 如您所见, 对于某个反馈电容值, 巴特沃斯型 响应的一半, 相补角将下降至大约 39°。 但是,闭环 带宽 已从 10 MHz 增至 14 MHz。 另一方面, 反馈电容值翻倍 导致相补角 接近 90°。 不过,带宽的 减幅过半, 降至 4MHz。 这样,通过更改 反馈电容值, 设计人员可通过 控制相补角 来控制 想要在电路中 实现的脉冲响应, 或者可控制所需的 闭环带宽。 解补偿运算放大器 是单位增益不稳定的 放大器。 单位增益稳定放大器 具有第二个 AOL 极点, 该极点通常在 零 dB 交叉处出现。 另一方面, 解补偿运算放大器 将在其单位 增益带宽前, 出现其第二个极点。 解补偿运算 放大器使 IC 设计人员 能够在相同静态电流下是选择 相对更高带宽、更低噪声的放大器 还是选择单位增益稳定的 对应放大器之间做出 折衷。 我们现在比较 两个 TI 放大器, OPS 656 为单位增益稳定, OPS 657 则在增益为 7 时 稳定。 如您可见,在两个案例中, 消耗的静态电流均为 14 毫安。 然而, 在 OPS 657 案例中, 对于 656, 增益带宽积 约为 1.6GHz 对比 230MHz。 与此类似,657 的噪声 比 OPS 656 的噪声 要低得多。 看一看开环 增益幅度曲线, 您将注意到 在 OPS 656 中, 即此处上方的 蓝色曲线, 斜率从大约 20 dB/十倍频程 降低到每十倍频 40 dB, 接近零 db 交叉处。 但是, 在 OPS 657 中, 其出现要早得多。 现在,让我们看看 补偿放大器 更适合 TIA 应用。 如先前 所讨论, TIA 的噪声增益 将受到输入和 反馈电容的影响。 由于对噪声增益 曲线存在此影响, 在幅度大于零 dB 处 将出现相补角。 对于适当补偿的 放大器, 在增益为 1 加上总计 C 除以反馈 C 得出的增益处 通常将出现交叉。 在 OPS 657 的案例中, 噪声增益曲线 将在 37 dB 处与 开环增益曲线相交, 而第二个开环增益 极点在 19 dB 处出现。 这表示存在 -20 dB/十倍频程接近率, 而这意味着稳定的 运算放大器配置。 请记住, 对于巴特沃斯型响应, 相补角 为 65°, 闭环带宽 由该方程式得出。 要实现 该闭环带宽的 相应 反馈电容 由此处的方程式得出。 现在,我已扫描从 1 千欧姆 至 10 兆欧姆的 反馈电阻, 并抽取了 所需的闭环带宽 和反馈电容值。 我已检查了 四个不同的 具有增益带宽的放大器产品, 频率范围涵盖 500MHz 至 2GHz,应有尽有。 正如预期,更高的 增益带宽放大器 能够产生 更高的闭环带宽。 在各自情况下, 我假定输入电容为 10 皮法拉。 随着输入 电容值增加, 可实现的带宽 将减少。 现在,让我们 来看看反馈电容。 闭环带宽 越高, 获得巴特沃斯响应 所需的反馈电容值 就变得 极小, 并可以是数十飞法拉。 在此类情况下, 此类反馈电容值 可能就很难 在硬件中实现。 实现极低的 反馈电容值 可能不切实际, 因为没有足够的 0.2 皮法拉以下的 芯片电容器, 并且因为 存在 PCB 寄生, 这使外部 电容器显得逊色。 此外, 反馈电阻器包 自身具有自己的 寄生电容, 应将该电容值加上, 从而防止 设计人员得出 极低的反馈 电容值。 通过移除 低于放大器、 反向输入、其输出以及 反馈路径下的接地平面和电源平面, 可以减小 寄生电流。 有可能通过 使用电容 T 形网络, 实现极小的 电容器值, 如此电路中所示, 其有效电容 由此方程式给出。 例如,C1 等于 C2 等于 1 皮法拉, C3 等于 47 皮法拉, 该 T 形网络的 等效电容 结果是 20 飞法拉。 同样,要获得 极大的反馈电阻, 可使用电阻器 树形网络, 其中冷却剂电阻 由此方程式给出。 同样,如果 R1 等于 R2, 等于 100 千欧姆, 且 R3 等于 10 千欧姆, 则可获得等效电阻 或 1.2 兆欧姆。 现在,让我们看看 影响互阻抗放大器 总输出噪声的 各种元件。 存在 4 个 影响因素。 还有放大器的 电压噪声 影响的噪声, 运算放大器的 电流噪声 影响的噪声, 反馈电阻器元件 影响的噪声, 并且存在 因放大器的 电压噪声和 噪声增益形状产生的 总输出电压噪声。 我们现在将分别检查 四个影响因子中的 一个。 在极低频率时, 输入电容 与反馈电容 为开路, 从而在放大器的 输出端 将出现增益为 1 的 放大器电压噪声。 在反馈电阻 作用下, 放大器的 电流噪声将提高, 并以其输出的形式出现。 同样, 反馈电阻器的噪声 将直接出现在 放大器的输出端, 且增益为零 dB。 请注意,此处所有 噪声项 均指噪声密度, 其单位为每根赫兹。 在下张幻灯片上 将详细讨论 最终噪声项。 TIA 的噪声增益 将使高频下的 电压噪声 成形。 我已仿真 TIA 的 输出噪声, 假定放大器噪声 为 4 纳伏/根赫兹, 以及输入和输出元件 如先前所述。 TIA 在 低频率下的噪声为 4 纳伏/根赫兹, 与预期相符。 在 100KHz 零频率后, 噪声开始以 20dB/十倍频程的速率增加。 噪声在极点频率处 乘以 37 dB 最大值, 并自此 保持不变。 但是,TIA 的 输出噪声 将以 20dB/十倍频程的速度递减, 因为它存在闭环增益 滚降。 TIA 在高频处的 输出噪声 可按此方程式逼近, 其中 F 通常是 任何 TIA 后滤波的带宽, 或者是 TIA 本身的 闭环带宽。 称作 TIA 噪声的 总输入是 所有单个 影响因素 除以互阻抗增益 RF 结果平方和的 平方根。 重要的是,在 JFET 或 CMOS 输入放大器案例中, 可以忽略 电流噪声项, 因为它极小。 这可导致 TIA 设计人员相信 JFET 或 CMOS 输入放大器 将始终提供 最低噪声解决方案。 但是,这可能不是真的, 因为传统上 BJT 输入放大器 与其 FET 对应产品相比 具有低电压 噪声。 本示例中, 我将双极输入放大器 OPA846 与 JFET 输入放大器 OPA657 进行了对比。 如您在 JFET 的 例子中所见, 电流噪声比 BJT 输入放大器低得多。 然而,其电压 噪声 也比双极输入 放大器高得多。 在本图中, 我将在扫描反馈电阻期间 将 OPA846 和 OPA657 的 输入参考噪声进行了 比较。 在电阻较低处, OPA846 影响的噪声 低于 657, 这是因为此处的 主要因素是电压噪声。 不过,随着反馈 电容值增加, 您可以看到 JFET 输入放大器趋于 变成更佳的解决方案。 这是因为双极输入 放大器 OPA846 的 电流噪声 在反馈电阻的作用下 放大。 它将开始主导 总输出噪声。 总而言之, BJT 输入放大器 在高频的中到高 互阻抗增益应用中 将展示卓越的 SNR 性能, 而 FET 和 CMOS 输入放大器 将在中到低频率 但互阻抗增益极高的应用中 展示卓越的 SNR 性能。 总之, 互阻抗放大器 具有二阶 闭环响应。 封闭型方程式 表明它将使设计人员 能够根据期望的 互阻抗增益 和输入电容 推导带宽和 反馈电容。 由于噪声增益 始终是高值处 穿过开环增益曲线, 因此如得到正确补偿, 运算放大器就 无需稳定的单位增益。 事实上,解补偿放大器 可能会变成更佳。 互阻抗放大器的 输出噪声 在较高频率下将 很大程度上受到 峰值上升电压噪声的影响。 一般而言, 双极输入放大器 更适于在较宽带宽处 提供低至中的 互阻抗增益, 而 JEFT 与 CMOS 输入放大器 更适于在较低 带宽处提供高 高互阻抗增益。 当使用 BJT 输入放大器时, 必须将等于 反馈电阻的电阻器 放在介于从运算 放大器非反向终端至 接地之间的位置。 这用于抵消 BJT 放大器 偏移电流的 效应。 除此之外, 将旁路电容器 并联非反向 终端上的电阻器 以降低较高 频率处电阻器的 噪声影响量。 我在此列出了 一些其他资源 以帮助您 设计 TIA。 此博客文章包含 指向 Excel 计算器的链接, 其中包含在此演示中 讨论的方程式。 我希望您觉得这对于 简化您的设计有用。 此外,在 TI 网站上 还提供了完整的 端到端参考设计 以使您能够评估 光学前端的 系统性能。 该设计包含激光 及其激光驱动器、 带偏置电源的 光电二极管、 放大器信号链以及 包含时钟电路、 FGA 以及 内存的 ADC 板。 我希望您觉得这 有助于评估您的系统 性能。 谢谢。

大家好! 我叫 Samir Cherian, 是德州仪器 (TI) 高速放大器团队的 应用工程师。 今天,我将展示 有关如何 优化互阻抗放大器 以用于高速应用的 定性分析。 互阻抗 放大器 用于转换来自 光学传感器的 输出电流,例如, 将光电二极管变为电压。 TIA 的概念简单。 它们依据欧姆定律在运算放大器中 使用反馈电阻器 将电流 转为电压。 但是,当尝试 最大程度提高 高速系统的 性能时, 分析会变得相当复杂。 在本演示中, 我将介绍理论设计 概念, 然后在 Spice 环境中 应用这些概念。 我们将在本演示中 着重介绍三个领域 - 介绍影响其 频率响应和形状的 TIA 和 因素。 我将深入介绍 可能影响放大器稳定性的 每个因素。 然后,我将最终 检查影响 TIA 中 总体噪声的 单独元素。 您还将在下面 找到两个链接。 第一个链接是对 基础放大器稳定性的回顾。 第二个链接是 应用手册, 它提供了 对互阻抗放大器 稳定性的 详细量化分析。 检测和放大 来自光电二极管的 高速小电流 可具有较高的设计难度。 光电二极管、 放大器以及印刷电路板的 寄生电容 相互之间 以及与反馈电阻之间 相互作用, 以修改 TIA 的 频率响应形状。 该图显示了 影响放大器 稳定性的 主要元素。 光电二极管具有 可从 1 皮法拉至 数百皮法拉不等的 寄生电容, 具体取决于其敏感度。 此外,运算放大器具有 共模和差分输入电容, 同样也需要 加以考虑。 此外,PCB 也具有一些 寄生电容。 在本演示中, 我将三个电容 合为一个单输入电容, 记为总计 C。 除在放大器的 输入节点上的 电容器存在寄生效应外, 在 PCB 以及 反馈电阻器封装中 也有反馈寄生效应, 稍后, 我将讨论 与射频 同时增加的 物理电容器。 TIA 的带宽由 三个关键元素 确定。 首选是总输入 电容 - 这包括光电二极管电容、 运算放大器输入电容, 以及任何 寄生 PCB 电容。 其次是符合期望的互阻抗增益。 最后,同样还有运算 放大器的带宽积。 运算放大器的 带宽增益越高, 产生的闭环带宽 互阻抗带宽就越高。 以上三个因素 相互关联。 对于选定的 特定运算放大器, 以互阻抗 增益为目标 就会设定 最大带宽, 或反之,以该带宽为目标 就会将设定最大增益。 我将使用 TINA-Spice 仿真软件展示 TIA 的 基础构建块以及 不同的组件如何影响 TIA 的稳定性和噪声。 在本演示中, 我将着重 介绍针对目标 互阻抗增益 实现 65° 相补角的 巴特沃斯型响应形状, 然后,我将推导 闭环响应 和噪声。 当尝试选择互阻抗 设计的运算放大器时, 务必了解三件事, 光电二极管 电容、所需的 互阻抗 增益,以及所需的 闭环带宽。 放大器的稳定性 取决于其环路增益, 其定义为 开环增益 AOL 与 反馈因子 β 的乘积。 运算放大器的 反馈因子是 其噪声增益的倒数。 为仿真 环路增益, 我将使用 图中所示的 两个电路配置。 DUT 配置用于 提取运算放大器的 开路增益幅度和相位。 图中显示的 大电容器和电感器 将配置开路中的 运算放大器 以提取其 AOL。 理想的 放大器配置 使用理想的运算放大器 提取噪声增益, 这是围绕运算 放大器无源元件的 功能。 在第一种情况下, 我将假定 DUT 没有任何输入电容 和理想的光电二极管, 没有寄生电容。 在此案例中, 没有任何输入和反馈 电容器, 放大器采用单元增益缓冲器 配置。 噪声增益的 幅度在整个频率中 并没有扁平为零 dB, 其相位也是如此。 以 dB 表示的 环路增益是 AOL 与 β 之和。 由于 β 是 0dB, 环路增益将跟踪开环增益。 如要确定 相补角, 查找 AOL 曲线 与 β 曲线相交处的 频率。 该点可称为 回路增益交叉点。 在此案例中, 环路增益交叉点 出现在 运算放大器的 增益带宽积,即 1GHz。 现在,找到交叉频率处 环路增益的 相位。 在本例中,它为 90°, 因为系统是 单极性放大器。 相补角为 180° 减去 90° 相移, 由于其为单极性, 这可产生 90° 的 相补角。 放大器 因此稳定。 现在让我们考虑 光电二极管和运算放大器的 输入电容。 我将假定总输入 电容为 10 皮法, 并且目标互阻抗 增益为 159 千欧姆。 开环增益 曲线将保持为 上一例中的 曲线不变, 如红色曲线所示。 出于噪音增益 考虑, 10 皮法拉 输入电容器 已添加至理想放大器的 反向终端处。 现在,让我们看看跨频率 噪声增益行为。 在低频时, 10 皮法拉电容 阻抗 将极高, 并因此将被 视为开路。 在低频时, 放大器 将如前用作 空增益缓冲器, 此增益幅度为零 dB。 随着频率上升, 输出电容器的阻抗 将开始降低。 在 1/2π RFC(总计)的 频率下, 即 100KHz 频率下, 阻抗电容器 等于反馈 电阻器的值。 这是噪声增益 曲线上的零。 在零频率以上, 噪声增益 将开始以 20 dB/十倍频程的速率增加。 总相位 会发生变化, 因为它将是 0° 至 90°。 现在,让我们考虑 环路增益交叉。 我们使开环增益 降低 20dB/十倍频程。 它将在 1GHz 处 经过 0db 线。 与此类似, 噪声增益曲线 将开始在 100KHz 处 以 20dB/十倍频程的速率增加。 交点 即环路增益交叉点, 它是 100KHz 处 零频率与 1GHz 处放大器 增益带宽积的 几何平均数。 此环路增益因此 将在 10MHz 交叉。 请记住,噪声增益中的零 是 β 中的极。 产生的环路增益 确实有双极响应。 现在我们需要了解一下幅度。 噪声增益 始于 100KHz, 并以 20 dB/十倍频程的 速率增加, 而 AOL 以 -20 dB/十倍 频程的速度降低。 环路增益在 环路增益交叉频率处 具有 -40 dB 的 接近率。 这通常指示存在 潜在的不稳定性。 现在,让我们来看看 环路增益的相位。 正如此前的情况, 1KHz 的主极点 将影响 90° 的总相移, 该相移在 10KHz 处结束。 但是,现在由于 在 100KHz 处为零, 相位将 持续减少。 在 1MHz 时, 总相移 接近 180°。 请记住,在此之前, 环路增益交叉处 为 10MHz。 在该频率处, 围绕反馈环路的 总相移 是 180°, 这表示产生的 相补角是 0°, 并且 TIA 现在 将变得不稳定。 现在,让我们考虑 TIA 的环路增益响应 对反馈电容的影响。 我将首先 假定反馈电容 为 141 飞法拉。 我将稍后 展示, 我是如何针对反馈电容 提出此类值。 检查整个频率的 噪声增益形状。 如前所述, 噪声增益 将在 低频时扁平。 由于反馈电容 远小于 输入电容, 它将不会影响 零频率的位置。 但是, 在 1/2π RFCF 的频率下, 即 10 MHz 频率下, 反馈电阻 与反馈电容的阻抗 将变为相等。 在较高频率处, 由于 Rf 与 Cf 并联, RF 不再会 影响噪声增益。 因此,产生的 噪声增益 将由总计为 C 的 输入电容以及 反馈电容 CF 确定。 由于这两个电容器的 阻抗幅度 将以相同 频率变化, 噪声增益将变平, 如图中所示。 反馈电容 因此具有 在噪声增益中插入池的效果, 这将继而纠正 环路增益曲线上 回收相位。 如图中所示, 环路增益交叉点 将在接近极点频率的 位置处出现, 大约 10MHz。 现在,让我们来看看 相位响应。 比极点频率 低十倍频程, 由于存在反馈电容, 环路增益相 将开始以 45 度/十倍频程的速率增加。 在 10MHz 处出现 环路增益交叉时, 覆盖足够 相位的环路增益 可提供大约 65° 的相比角, 因此为我们带来 巴特沃斯型响应。 将反馈电容 设为远低于 该 141 飞法拉的值 将进一步 推动 极点频率。 这将导致 相补角不够理想。 与此类似, 将反馈电容 提高到远高于 141 飞法拉的值, 这将使极点频率 更接近零频率。 这将导致 过阻尼响应。 但是,闭环 带宽 将比过去 低得多。 结果变为, 对于巴特沃斯型响应, 相补角 为 65°, 您必须 根据此方程式 将反馈电容 设为相等, 其中 f -3 dB 是 由运算放大器增益带宽与 噪声增益中 零频率的几何平均数 得出。 我就是这样 得出 141 飞法拉的 反馈电容值。 在此幻灯片中, 我仿真 互阻抗放大器 在我更改反馈电容值后的 环路增益和 闭环带宽。 将反馈 电容值 提高到 280 飞法拉 会将极点频率拉至低值, 导致 相补角和 过阻尼响应增加。 当反馈电容器的 值降低时, 反之亦然。 极点在频率方面 会进一步外推, 从而缩减相补角 和频率响应 将显示超额峰值。 用于仿真闭环 互阻抗增益的电路 如此处所示。 最后, 我总结了 变更反馈 电容值的结果。 如您所见, 对于某个反馈电容值, 巴特沃斯型 响应的一半, 相补角将下降至大约 39°。 但是,闭环 带宽 已从 10 MHz 增至 14 MHz。 另一方面, 反馈电容值翻倍 导致相补角 接近 90°。 不过,带宽的 减幅过半, 降至 4MHz。 这样,通过更改 反馈电容值, 设计人员可通过 控制相补角 来控制 想要在电路中 实现的脉冲响应, 或者可控制所需的 闭环带宽。 解补偿运算放大器 是单位增益不稳定的 放大器。 单位增益稳定放大器 具有第二个 AOL 极点, 该极点通常在 零 dB 交叉处出现。 另一方面, 解补偿运算放大器 将在其单位 增益带宽前, 出现其第二个极点。 解补偿运算 放大器使 IC 设计人员 能够在相同静态电流下是选择 相对更高带宽、更低噪声的放大器 还是选择单位增益稳定的 对应放大器之间做出 折衷。 我们现在比较 两个 TI 放大器, OPS 656 为单位增益稳定, OPS 657 则在增益为 7 时 稳定。 如您可见,在两个案例中, 消耗的静态电流均为 14 毫安。 然而, 在 OPS 657 案例中, 对于 656, 增益带宽积 约为 1.6GHz 对比 230MHz。 与此类似,657 的噪声 比 OPS 656 的噪声 要低得多。 看一看开环 增益幅度曲线, 您将注意到 在 OPS 656 中, 即此处上方的 蓝色曲线, 斜率从大约 20 dB/十倍频程 降低到每十倍频 40 dB, 接近零 db 交叉处。 但是, 在 OPS 657 中, 其出现要早得多。 现在,让我们看看 补偿放大器 更适合 TIA 应用。 如先前 所讨论, TIA 的噪声增益 将受到输入和 反馈电容的影响。 由于对噪声增益 曲线存在此影响, 在幅度大于零 dB 处 将出现相补角。 对于适当补偿的 放大器, 在增益为 1 加上总计 C 除以反馈 C 得出的增益处 通常将出现交叉。 在 OPS 657 的案例中, 噪声增益曲线 将在 37 dB 处与 开环增益曲线相交, 而第二个开环增益 极点在 19 dB 处出现。 这表示存在 -20 dB/十倍频程接近率, 而这意味着稳定的 运算放大器配置。 请记住, 对于巴特沃斯型响应, 相补角 为 65°, 闭环带宽 由该方程式得出。 要实现 该闭环带宽的 相应 反馈电容 由此处的方程式得出。 现在,我已扫描从 1 千欧姆 至 10 兆欧姆的 反馈电阻, 并抽取了 所需的闭环带宽 和反馈电容值。 我已检查了 四个不同的 具有增益带宽的放大器产品, 频率范围涵盖 500MHz 至 2GHz,应有尽有。 正如预期,更高的 增益带宽放大器 能够产生 更高的闭环带宽。 在各自情况下, 我假定输入电容为 10 皮法拉。 随着输入 电容值增加, 可实现的带宽 将减少。 现在,让我们 来看看反馈电容。 闭环带宽 越高, 获得巴特沃斯响应 所需的反馈电容值 就变得 极小, 并可以是数十飞法拉。 在此类情况下, 此类反馈电容值 可能就很难 在硬件中实现。 实现极低的 反馈电容值 可能不切实际, 因为没有足够的 0.2 皮法拉以下的 芯片电容器, 并且因为 存在 PCB 寄生, 这使外部 电容器显得逊色。 此外, 反馈电阻器包 自身具有自己的 寄生电容, 应将该电容值加上, 从而防止 设计人员得出 极低的反馈 电容值。 通过移除 低于放大器、 反向输入、其输出以及 反馈路径下的接地平面和电源平面, 可以减小 寄生电流。 有可能通过 使用电容 T 形网络, 实现极小的 电容器值, 如此电路中所示, 其有效电容 由此方程式给出。 例如,C1 等于 C2 等于 1 皮法拉, C3 等于 47 皮法拉, 该 T 形网络的 等效电容 结果是 20 飞法拉。 同样,要获得 极大的反馈电阻, 可使用电阻器 树形网络, 其中冷却剂电阻 由此方程式给出。 同样,如果 R1 等于 R2, 等于 100 千欧姆, 且 R3 等于 10 千欧姆, 则可获得等效电阻 或 1.2 兆欧姆。 现在,让我们看看 影响互阻抗放大器 总输出噪声的 各种元件。 存在 4 个 影响因素。 还有放大器的 电压噪声 影响的噪声, 运算放大器的 电流噪声 影响的噪声, 反馈电阻器元件 影响的噪声, 并且存在 因放大器的 电压噪声和 噪声增益形状产生的 总输出电压噪声。 我们现在将分别检查 四个影响因子中的 一个。 在极低频率时, 输入电容 与反馈电容 为开路, 从而在放大器的 输出端 将出现增益为 1 的 放大器电压噪声。 在反馈电阻 作用下, 放大器的 电流噪声将提高, 并以其输出的形式出现。 同样, 反馈电阻器的噪声 将直接出现在 放大器的输出端, 且增益为零 dB。 请注意,此处所有 噪声项 均指噪声密度, 其单位为每根赫兹。 在下张幻灯片上 将详细讨论 最终噪声项。 TIA 的噪声增益 将使高频下的 电压噪声 成形。 我已仿真 TIA 的 输出噪声, 假定放大器噪声 为 4 纳伏/根赫兹, 以及输入和输出元件 如先前所述。 TIA 在 低频率下的噪声为 4 纳伏/根赫兹, 与预期相符。 在 100KHz 零频率后, 噪声开始以 20dB/十倍频程的速率增加。 噪声在极点频率处 乘以 37 dB 最大值, 并自此 保持不变。 但是,TIA 的 输出噪声 将以 20dB/十倍频程的速度递减, 因为它存在闭环增益 滚降。 TIA 在高频处的 输出噪声 可按此方程式逼近, 其中 F 通常是 任何 TIA 后滤波的带宽, 或者是 TIA 本身的 闭环带宽。 称作 TIA 噪声的 总输入是 所有单个 影响因素 除以互阻抗增益 RF 结果平方和的 平方根。 重要的是,在 JFET 或 CMOS 输入放大器案例中, 可以忽略 电流噪声项, 因为它极小。 这可导致 TIA 设计人员相信 JFET 或 CMOS 输入放大器 将始终提供 最低噪声解决方案。 但是,这可能不是真的, 因为传统上 BJT 输入放大器 与其 FET 对应产品相比 具有低电压 噪声。 本示例中, 我将双极输入放大器 OPA846 与 JFET 输入放大器 OPA657 进行了对比。 如您在 JFET 的 例子中所见, 电流噪声比 BJT 输入放大器低得多。 然而,其电压 噪声 也比双极输入 放大器高得多。 在本图中, 我将在扫描反馈电阻期间 将 OPA846 和 OPA657 的 输入参考噪声进行了 比较。 在电阻较低处, OPA846 影响的噪声 低于 657, 这是因为此处的 主要因素是电压噪声。 不过,随着反馈 电容值增加, 您可以看到 JFET 输入放大器趋于 变成更佳的解决方案。 这是因为双极输入 放大器 OPA846 的 电流噪声 在反馈电阻的作用下 放大。 它将开始主导 总输出噪声。 总而言之, BJT 输入放大器 在高频的中到高 互阻抗增益应用中 将展示卓越的 SNR 性能, 而 FET 和 CMOS 输入放大器 将在中到低频率 但互阻抗增益极高的应用中 展示卓越的 SNR 性能。 总之, 互阻抗放大器 具有二阶 闭环响应。 封闭型方程式 表明它将使设计人员 能够根据期望的 互阻抗增益 和输入电容 推导带宽和 反馈电容。 由于噪声增益 始终是高值处 穿过开环增益曲线, 因此如得到正确补偿, 运算放大器就 无需稳定的单位增益。 事实上,解补偿放大器 可能会变成更佳。 互阻抗放大器的 输出噪声 在较高频率下将 很大程度上受到 峰值上升电压噪声的影响。 一般而言, 双极输入放大器 更适于在较宽带宽处 提供低至中的 互阻抗增益, 而 JEFT 与 CMOS 输入放大器 更适于在较低 带宽处提供高 高互阻抗增益。 当使用 BJT 输入放大器时, 必须将等于 反馈电阻的电阻器 放在介于从运算 放大器非反向终端至 接地之间的位置。 这用于抵消 BJT 放大器 偏移电流的 效应。 除此之外, 将旁路电容器 并联非反向 终端上的电阻器 以降低较高 频率处电阻器的 噪声影响量。 我在此列出了 一些其他资源 以帮助您 设计 TIA。 此博客文章包含 指向 Excel 计算器的链接, 其中包含在此演示中 讨论的方程式。 我希望您觉得这对于 简化您的设计有用。 此外,在 TI 网站上 还提供了完整的 端到端参考设计 以使您能够评估 光学前端的 系统性能。 该设计包含激光 及其激光驱动器、 带偏置电源的 光电二极管、 放大器信号链以及 包含时钟电路、 FGA 以及 内存的 ADC 板。 我希望您觉得这 有助于评估您的系统 性能。 谢谢。

大家好!

我叫 Samir Cherian,

是德州仪器 (TI) 高速放大器团队的

应用工程师。

今天,我将展示 有关如何

优化互阻抗放大器 以用于高速应用的

定性分析。

互阻抗 放大器

用于转换来自 光学传感器的

输出电流,例如, 将光电二极管变为电压。

TIA 的概念简单。

它们依据欧姆定律在运算放大器中 使用反馈电阻器

将电流 转为电压。

但是,当尝试 最大程度提高

高速系统的 性能时,

分析会变得相当复杂。

在本演示中, 我将介绍理论设计

概念, 然后在 Spice 环境中

应用这些概念。

我们将在本演示中 着重介绍三个领域 -

介绍影响其 频率响应和形状的

TIA 和 因素。

我将深入介绍 可能影响放大器稳定性的

每个因素。

然后,我将最终 检查影响 TIA 中

总体噪声的 单独元素。

您还将在下面 找到两个链接。

第一个链接是对 基础放大器稳定性的回顾。

第二个链接是 应用手册,

它提供了 对互阻抗放大器

稳定性的 详细量化分析。

检测和放大 来自光电二极管的

高速小电流 可具有较高的设计难度。

光电二极管、 放大器以及印刷电路板的

寄生电容 相互之间

以及与反馈电阻之间 相互作用,

以修改 TIA 的 频率响应形状。

该图显示了 影响放大器

稳定性的 主要元素。

光电二极管具有 可从 1 皮法拉至

数百皮法拉不等的 寄生电容,

具体取决于其敏感度。

此外,运算放大器具有 共模和差分输入电容,

同样也需要 加以考虑。

此外,PCB 也具有一些

寄生电容。

在本演示中, 我将三个电容

合为一个单输入电容, 记为总计 C。

除在放大器的 输入节点上的

电容器存在寄生效应外, 在 PCB 以及

反馈电阻器封装中 也有反馈寄生效应,

稍后, 我将讨论

与射频 同时增加的

物理电容器。

TIA 的带宽由 三个关键元素

确定。

首选是总输入 电容 -

这包括光电二极管电容、 运算放大器输入电容,

以及任何 寄生 PCB 电容。

其次是符合期望的互阻抗增益。

最后,同样还有运算 放大器的带宽积。

运算放大器的 带宽增益越高,

产生的闭环带宽 互阻抗带宽就越高。

以上三个因素 相互关联。

对于选定的 特定运算放大器,

以互阻抗 增益为目标

就会设定 最大带宽,

或反之,以该带宽为目标 就会将设定最大增益。

我将使用 TINA-Spice 仿真软件展示 TIA 的

基础构建块以及 不同的组件如何影响

TIA 的稳定性和噪声。

在本演示中, 我将着重

介绍针对目标 互阻抗增益

实现 65° 相补角的 巴特沃斯型响应形状,

然后,我将推导 闭环响应

和噪声。

当尝试选择互阻抗 设计的运算放大器时,

务必了解三件事, 光电二极管

电容、所需的 互阻抗

增益,以及所需的 闭环带宽。

放大器的稳定性 取决于其环路增益,

其定义为 开环增益

AOL 与 反馈因子 β 的乘积。

运算放大器的 反馈因子是

其噪声增益的倒数。

为仿真 环路增益,

我将使用 图中所示的

两个电路配置。

DUT 配置用于 提取运算放大器的

开路增益幅度和相位。

图中显示的 大电容器和电感器

将配置开路中的 运算放大器

以提取其 AOL。

理想的 放大器配置

使用理想的运算放大器 提取噪声增益,

这是围绕运算 放大器无源元件的

功能。

在第一种情况下, 我将假定 DUT

没有任何输入电容 和理想的光电二极管,

没有寄生电容。

在此案例中, 没有任何输入和反馈

电容器, 放大器采用单元增益缓冲器

配置。

噪声增益的 幅度在整个频率中

并没有扁平为零 dB, 其相位也是如此。

以 dB 表示的 环路增益是

AOL 与 β 之和。

由于 β 是 0dB, 环路增益将跟踪开环增益。

如要确定 相补角,

查找 AOL 曲线 与 β 曲线相交处的

频率。

该点可称为 回路增益交叉点。

在此案例中, 环路增益交叉点

出现在 运算放大器的

增益带宽积,即 1GHz。

现在,找到交叉频率处 环路增益的

相位。

在本例中,它为 90°, 因为系统是

单极性放大器。

相补角为 180°

减去 90° 相移, 由于其为单极性,

这可产生 90° 的 相补角。

放大器 因此稳定。

现在让我们考虑 光电二极管和运算放大器的

输入电容。

我将假定总输入 电容为 10 皮法,

并且目标互阻抗 增益为 159 千欧姆。

开环增益 曲线将保持为

上一例中的 曲线不变,

如红色曲线所示。

出于噪音增益 考虑,

10 皮法拉 输入电容器

已添加至理想放大器的 反向终端处。

现在,让我们看看跨频率 噪声增益行为。

在低频时, 10 皮法拉电容

阻抗 将极高,

并因此将被 视为开路。

在低频时, 放大器

将如前用作 空增益缓冲器,

此增益幅度为零 dB。

随着频率上升, 输出电容器的阻抗

将开始降低。

在 1/2π RFC(总计)的 频率下,

即 100KHz 频率下, 阻抗电容器

等于反馈 电阻器的值。

这是噪声增益 曲线上的零。

在零频率以上, 噪声增益

将开始以 20 dB/十倍频程的速率增加。

总相位 会发生变化,

因为它将是 0° 至 90°。

现在,让我们考虑 环路增益交叉。

我们使开环增益 降低 20dB/十倍频程。

它将在 1GHz 处 经过 0db 线。

与此类似, 噪声增益曲线

将开始在 100KHz 处 以 20dB/十倍频程的速率增加。

交点 即环路增益交叉点,

它是 100KHz 处 零频率与

1GHz 处放大器 增益带宽积的

几何平均数。

此环路增益因此 将在 10MHz 交叉。

请记住,噪声增益中的零 是 β 中的极。

产生的环路增益 确实有双极响应。

现在我们需要了解一下幅度。

噪声增益 始于 100KHz,

并以 20 dB/十倍频程的 速率增加,

而 AOL 以 -20 dB/十倍 频程的速度降低。

环路增益在 环路增益交叉频率处

具有 -40 dB 的 接近率。

这通常指示存在 潜在的不稳定性。

现在,让我们来看看 环路增益的相位。

正如此前的情况, 1KHz 的主极点

将影响 90° 的总相移,

该相移在 10KHz 处结束。

但是,现在由于 在 100KHz 处为零,

相位将 持续减少。

在 1MHz 时, 总相移

接近 180°。

请记住,在此之前, 环路增益交叉处

为 10MHz。

在该频率处, 围绕反馈环路的

总相移 是 180°,

这表示产生的 相补角是 0°,

并且 TIA 现在 将变得不稳定。

现在,让我们考虑 TIA 的环路增益响应

对反馈电容的影响。

我将首先 假定反馈电容

为 141 飞法拉。

我将稍后 展示,

我是如何针对反馈电容 提出此类值。

检查整个频率的 噪声增益形状。

如前所述, 噪声增益

将在 低频时扁平。

由于反馈电容 远小于

输入电容, 它将不会影响

零频率的位置。

但是, 在 1/2π RFCF 的频率下,

即 10 MHz 频率下,

反馈电阻 与反馈电容的阻抗

将变为相等。

在较高频率处, 由于 Rf 与 Cf 并联,

RF 不再会 影响噪声增益。

因此,产生的 噪声增益

将由总计为 C 的 输入电容以及

反馈电容 CF 确定。

由于这两个电容器的 阻抗幅度

将以相同 频率变化,

噪声增益将变平, 如图中所示。

反馈电容 因此具有

在噪声增益中插入池的效果, 这将继而纠正

环路增益曲线上 回收相位。

如图中所示, 环路增益交叉点

将在接近极点频率的 位置处出现,

大约 10MHz。

现在,让我们来看看 相位响应。

比极点频率 低十倍频程,

由于存在反馈电容, 环路增益相

将开始以 45 度/十倍频程的速率增加。

在 10MHz 处出现 环路增益交叉时,

覆盖足够 相位的环路增益

可提供大约 65° 的相比角,

因此为我们带来 巴特沃斯型响应。

将反馈电容 设为远低于

该 141 飞法拉的值 将进一步

推动 极点频率。

这将导致 相补角不够理想。

与此类似, 将反馈电容

提高到远高于 141 飞法拉的值,

这将使极点频率 更接近零频率。

这将导致 过阻尼响应。

但是,闭环 带宽

将比过去 低得多。

结果变为, 对于巴特沃斯型响应,

相补角 为 65°,

您必须 根据此方程式

将反馈电容 设为相等,

其中 f -3 dB 是 由运算放大器增益带宽与

噪声增益中 零频率的几何平均数

得出。

我就是这样 得出 141 飞法拉的

反馈电容值。

在此幻灯片中, 我仿真

互阻抗放大器 在我更改反馈电容值后的

环路增益和 闭环带宽。

将反馈 电容值

提高到 280 飞法拉 会将极点频率拉至低值,

导致 相补角和

过阻尼响应增加。

当反馈电容器的 值降低时,

反之亦然。

极点在频率方面 会进一步外推,

从而缩减相补角 和频率响应

将显示超额峰值。

用于仿真闭环 互阻抗增益的电路

如此处所示。

最后, 我总结了

变更反馈 电容值的结果。

如您所见, 对于某个反馈电容值,

巴特沃斯型 响应的一半,

相补角将下降至大约 39°。

但是,闭环 带宽

已从 10 MHz 增至 14 MHz。

另一方面, 反馈电容值翻倍

导致相补角 接近 90°。

不过,带宽的 减幅过半,

降至 4MHz。

这样,通过更改 反馈电容值,

设计人员可通过 控制相补角

来控制 想要在电路中

实现的脉冲响应, 或者可控制所需的

闭环带宽。

解补偿运算放大器 是单位增益不稳定的

放大器。

单位增益稳定放大器 具有第二个 AOL 极点,

该极点通常在 零 dB 交叉处出现。

另一方面, 解补偿运算放大器

将在其单位 增益带宽前,

出现其第二个极点。

解补偿运算 放大器使 IC 设计人员

能够在相同静态电流下是选择 相对更高带宽、更低噪声的放大器

还是选择单位增益稳定的 对应放大器之间做出

折衷。

我们现在比较 两个 TI 放大器,

OPS 656 为单位增益稳定, OPS 657 则在增益为 7 时

稳定。

如您可见,在两个案例中, 消耗的静态电流均为

14 毫安。

然而, 在 OPS 657 案例中,

对于 656, 增益带宽积

约为 1.6GHz 对比 230MHz。

与此类似,657 的噪声 比 OPS 656 的噪声

要低得多。

看一看开环 增益幅度曲线,

您将注意到 在 OPS 656 中,

即此处上方的 蓝色曲线,

斜率从大约 20 dB/十倍频程 降低到每十倍频 40 dB,

接近零 db 交叉处。

但是, 在 OPS 657 中,

其出现要早得多。

现在,让我们看看 补偿放大器

更适合 TIA 应用。

如先前 所讨论,

TIA 的噪声增益 将受到输入和

反馈电容的影响。

由于对噪声增益 曲线存在此影响,

在幅度大于零 dB 处 将出现相补角。

对于适当补偿的 放大器,

在增益为 1 加上总计 C 除以反馈 C 得出的增益处

通常将出现交叉。

在 OPS 657 的案例中, 噪声增益曲线

将在 37 dB 处与 开环增益曲线相交,

而第二个开环增益 极点在 19 dB 处出现。

这表示存在 -20 dB/十倍频程接近率,

而这意味着稳定的 运算放大器配置。

请记住, 对于巴特沃斯型响应,

相补角 为 65°,

闭环带宽 由该方程式得出。

要实现 该闭环带宽的

相应 反馈电容

由此处的方程式得出。

现在,我已扫描从 1 千欧姆 至 10 兆欧姆的

反馈电阻, 并抽取了

所需的闭环带宽 和反馈电容值。

我已检查了 四个不同的

具有增益带宽的放大器产品, 频率范围涵盖 500MHz

至 2GHz,应有尽有。

正如预期,更高的 增益带宽放大器

能够产生 更高的闭环带宽。

在各自情况下, 我假定输入电容为

10 皮法拉。

随着输入 电容值增加,

可实现的带宽 将减少。

现在,让我们 来看看反馈电容。

闭环带宽 越高,

获得巴特沃斯响应 所需的反馈电容值

就变得 极小,

并可以是数十飞法拉。

在此类情况下, 此类反馈电容值

可能就很难 在硬件中实现。

实现极低的 反馈电容值

可能不切实际, 因为没有足够的

0.2 皮法拉以下的 芯片电容器,

并且因为 存在 PCB 寄生,

这使外部 电容器显得逊色。

此外, 反馈电阻器包

自身具有自己的 寄生电容,

应将该电容值加上, 从而防止

设计人员得出 极低的反馈

电容值。

通过移除 低于放大器、

反向输入、其输出以及 反馈路径下的接地平面和电源平面,

可以减小 寄生电流。

有可能通过 使用电容 T 形网络,

实现极小的 电容器值,

如此电路中所示, 其有效电容

由此方程式给出。

例如,C1 等于 C2 等于 1 皮法拉,

C3 等于 47 皮法拉,

该 T 形网络的 等效电容

结果是 20 飞法拉。

同样,要获得 极大的反馈电阻,

可使用电阻器 树形网络,

其中冷却剂电阻 由此方程式给出。

同样,如果 R1 等于 R2,

等于 100 千欧姆, 且 R3 等于 10 千欧姆,

则可获得等效电阻 或 1.2 兆欧姆。

现在,让我们看看 影响互阻抗放大器

总输出噪声的 各种元件。

存在 4 个 影响因素。

还有放大器的 电压噪声

影响的噪声, 运算放大器的

电流噪声 影响的噪声,

反馈电阻器元件 影响的噪声,

并且存在 因放大器的

电压噪声和 噪声增益形状产生的

总输出电压噪声。

我们现在将分别检查 四个影响因子中的

一个。

在极低频率时, 输入电容

与反馈电容 为开路,

从而在放大器的 输出端

将出现增益为 1 的 放大器电压噪声。

在反馈电阻 作用下,

放大器的 电流噪声将提高,

并以其输出的形式出现。

同样, 反馈电阻器的噪声

将直接出现在 放大器的输出端,

且增益为零 dB。

请注意,此处所有 噪声项

均指噪声密度, 其单位为每根赫兹。

在下张幻灯片上 将详细讨论

最终噪声项。

TIA 的噪声增益 将使高频下的

电压噪声 成形。

我已仿真 TIA 的 输出噪声,

假定放大器噪声 为 4 纳伏/根赫兹,

以及输入和输出元件 如先前所述。

TIA 在 低频率下的噪声为

4 纳伏/根赫兹, 与预期相符。

在 100KHz 零频率后,

噪声开始以 20dB/十倍频程的速率增加。

噪声在极点频率处 乘以 37 dB 最大值,

并自此 保持不变。

但是,TIA 的 输出噪声

将以 20dB/十倍频程的速度递减, 因为它存在闭环增益

滚降。

TIA 在高频处的 输出噪声

可按此方程式逼近, 其中 F 通常是

任何 TIA 后滤波的带宽,

或者是 TIA 本身的 闭环带宽。

称作 TIA 噪声的 总输入是

所有单个 影响因素

除以互阻抗增益 RF 结果平方和的

平方根。

重要的是,在 JFET 或 CMOS 输入放大器案例中,

可以忽略 电流噪声项,

因为它极小。

这可导致 TIA 设计人员相信

JFET 或 CMOS 输入放大器

将始终提供 最低噪声解决方案。

但是,这可能不是真的, 因为传统上 BJT 输入放大器

与其 FET 对应产品相比 具有低电压

噪声。

本示例中, 我将双极输入放大器

OPA846 与 JFET 输入放大器 OPA657

进行了对比。

如您在 JFET 的 例子中所见,

电流噪声比 BJT 输入放大器低得多。

然而,其电压 噪声

也比双极输入 放大器高得多。

在本图中, 我将在扫描反馈电阻期间

将 OPA846 和 OPA657 的 输入参考噪声进行了

比较。

在电阻较低处, OPA846 影响的噪声

低于 657,

这是因为此处的 主要因素是电压噪声。

不过,随着反馈 电容值增加,

您可以看到 JFET 输入放大器趋于

变成更佳的解决方案。

这是因为双极输入 放大器 OPA846 的

电流噪声 在反馈电阻的作用下

放大。

它将开始主导 总输出噪声。

总而言之, BJT 输入放大器

在高频的中到高 互阻抗增益应用中

将展示卓越的 SNR 性能,

而 FET 和 CMOS 输入放大器

将在中到低频率 但互阻抗增益极高的应用中

展示卓越的 SNR 性能。

总之, 互阻抗放大器

具有二阶 闭环响应。

封闭型方程式 表明它将使设计人员

能够根据期望的 互阻抗增益

和输入电容 推导带宽和

反馈电容。

由于噪声增益 始终是高值处

穿过开环增益曲线, 因此如得到正确补偿,

运算放大器就 无需稳定的单位增益。

事实上,解补偿放大器 可能会变成更佳。

互阻抗放大器的 输出噪声

在较高频率下将 很大程度上受到

峰值上升电压噪声的影响。

一般而言, 双极输入放大器

更适于在较宽带宽处 提供低至中的

互阻抗增益, 而 JEFT 与 CMOS 输入放大器

更适于在较低 带宽处提供高

高互阻抗增益。

当使用 BJT 输入放大器时,

必须将等于 反馈电阻的电阻器

放在介于从运算 放大器非反向终端至

接地之间的位置。

这用于抵消 BJT 放大器 偏移电流的

效应。

除此之外, 将旁路电容器

并联非反向 终端上的电阻器

以降低较高 频率处电阻器的

噪声影响量。

我在此列出了 一些其他资源

以帮助您 设计 TIA。

此博客文章包含 指向 Excel 计算器的链接,

其中包含在此演示中 讨论的方程式。

我希望您觉得这对于 简化您的设计有用。

此外,在 TI 网站上

还提供了完整的 端到端参考设计

以使您能够评估 光学前端的

系统性能。

该设计包含激光 及其激光驱动器、

带偏置电源的 光电二极管、

放大器信号链以及 包含时钟电路、

FGA 以及 内存的 ADC 板。

我希望您觉得这 有助于评估您的系统

性能。

谢谢。

大家好! 我叫 Samir Cherian, 是德州仪器 (TI) 高速放大器团队的 应用工程师。 今天,我将展示 有关如何 优化互阻抗放大器 以用于高速应用的 定性分析。 互阻抗 放大器 用于转换来自 光学传感器的 输出电流,例如, 将光电二极管变为电压。 TIA 的概念简单。 它们依据欧姆定律在运算放大器中 使用反馈电阻器 将电流 转为电压。 但是,当尝试 最大程度提高 高速系统的 性能时, 分析会变得相当复杂。 在本演示中, 我将介绍理论设计 概念, 然后在 Spice 环境中 应用这些概念。 我们将在本演示中 着重介绍三个领域 - 介绍影响其 频率响应和形状的 TIA 和 因素。 我将深入介绍 可能影响放大器稳定性的 每个因素。 然后,我将最终 检查影响 TIA 中 总体噪声的 单独元素。 您还将在下面 找到两个链接。 第一个链接是对 基础放大器稳定性的回顾。 第二个链接是 应用手册, 它提供了 对互阻抗放大器 稳定性的 详细量化分析。 检测和放大 来自光电二极管的 高速小电流 可具有较高的设计难度。 光电二极管、 放大器以及印刷电路板的 寄生电容 相互之间 以及与反馈电阻之间 相互作用, 以修改 TIA 的 频率响应形状。 该图显示了 影响放大器 稳定性的 主要元素。 光电二极管具有 可从 1 皮法拉至 数百皮法拉不等的 寄生电容, 具体取决于其敏感度。 此外,运算放大器具有 共模和差分输入电容, 同样也需要 加以考虑。 此外,PCB 也具有一些 寄生电容。 在本演示中, 我将三个电容 合为一个单输入电容, 记为总计 C。 除在放大器的 输入节点上的 电容器存在寄生效应外, 在 PCB 以及 反馈电阻器封装中 也有反馈寄生效应, 稍后, 我将讨论 与射频 同时增加的 物理电容器。 TIA 的带宽由 三个关键元素 确定。 首选是总输入 电容 - 这包括光电二极管电容、 运算放大器输入电容, 以及任何 寄生 PCB 电容。 其次是符合期望的互阻抗增益。 最后,同样还有运算 放大器的带宽积。 运算放大器的 带宽增益越高, 产生的闭环带宽 互阻抗带宽就越高。 以上三个因素 相互关联。 对于选定的 特定运算放大器, 以互阻抗 增益为目标 就会设定 最大带宽, 或反之,以该带宽为目标 就会将设定最大增益。 我将使用 TINA-Spice 仿真软件展示 TIA 的 基础构建块以及 不同的组件如何影响 TIA 的稳定性和噪声。 在本演示中, 我将着重 介绍针对目标 互阻抗增益 实现 65° 相补角的 巴特沃斯型响应形状, 然后,我将推导 闭环响应 和噪声。 当尝试选择互阻抗 设计的运算放大器时, 务必了解三件事, 光电二极管 电容、所需的 互阻抗 增益,以及所需的 闭环带宽。 放大器的稳定性 取决于其环路增益, 其定义为 开环增益 AOL 与 反馈因子 β 的乘积。 运算放大器的 反馈因子是 其噪声增益的倒数。 为仿真 环路增益, 我将使用 图中所示的 两个电路配置。 DUT 配置用于 提取运算放大器的 开路增益幅度和相位。 图中显示的 大电容器和电感器 将配置开路中的 运算放大器 以提取其 AOL。 理想的 放大器配置 使用理想的运算放大器 提取噪声增益, 这是围绕运算 放大器无源元件的 功能。 在第一种情况下, 我将假定 DUT 没有任何输入电容 和理想的光电二极管, 没有寄生电容。 在此案例中, 没有任何输入和反馈 电容器, 放大器采用单元增益缓冲器 配置。 噪声增益的 幅度在整个频率中 并没有扁平为零 dB, 其相位也是如此。 以 dB 表示的 环路增益是 AOL 与 β 之和。 由于 β 是 0dB, 环路增益将跟踪开环增益。 如要确定 相补角, 查找 AOL 曲线 与 β 曲线相交处的 频率。 该点可称为 回路增益交叉点。 在此案例中, 环路增益交叉点 出现在 运算放大器的 增益带宽积,即 1GHz。 现在,找到交叉频率处 环路增益的 相位。 在本例中,它为 90°, 因为系统是 单极性放大器。 相补角为 180° 减去 90° 相移, 由于其为单极性, 这可产生 90° 的 相补角。 放大器 因此稳定。 现在让我们考虑 光电二极管和运算放大器的 输入电容。 我将假定总输入 电容为 10 皮法, 并且目标互阻抗 增益为 159 千欧姆。 开环增益 曲线将保持为 上一例中的 曲线不变, 如红色曲线所示。 出于噪音增益 考虑, 10 皮法拉 输入电容器 已添加至理想放大器的 反向终端处。 现在,让我们看看跨频率 噪声增益行为。 在低频时, 10 皮法拉电容 阻抗 将极高, 并因此将被 视为开路。 在低频时, 放大器 将如前用作 空增益缓冲器, 此增益幅度为零 dB。 随着频率上升, 输出电容器的阻抗 将开始降低。 在 1/2π RFC(总计)的 频率下, 即 100KHz 频率下, 阻抗电容器 等于反馈 电阻器的值。 这是噪声增益 曲线上的零。 在零频率以上, 噪声增益 将开始以 20 dB/十倍频程的速率增加。 总相位 会发生变化, 因为它将是 0° 至 90°。 现在,让我们考虑 环路增益交叉。 我们使开环增益 降低 20dB/十倍频程。 它将在 1GHz 处 经过 0db 线。 与此类似, 噪声增益曲线 将开始在 100KHz 处 以 20dB/十倍频程的速率增加。 交点 即环路增益交叉点, 它是 100KHz 处 零频率与 1GHz 处放大器 增益带宽积的 几何平均数。 此环路增益因此 将在 10MHz 交叉。 请记住,噪声增益中的零 是 β 中的极。 产生的环路增益 确实有双极响应。 现在我们需要了解一下幅度。 噪声增益 始于 100KHz, 并以 20 dB/十倍频程的 速率增加, 而 AOL 以 -20 dB/十倍 频程的速度降低。 环路增益在 环路增益交叉频率处 具有 -40 dB 的 接近率。 这通常指示存在 潜在的不稳定性。 现在,让我们来看看 环路增益的相位。 正如此前的情况, 1KHz 的主极点 将影响 90° 的总相移, 该相移在 10KHz 处结束。 但是,现在由于 在 100KHz 处为零, 相位将 持续减少。 在 1MHz 时, 总相移 接近 180°。 请记住,在此之前, 环路增益交叉处 为 10MHz。 在该频率处, 围绕反馈环路的 总相移 是 180°, 这表示产生的 相补角是 0°, 并且 TIA 现在 将变得不稳定。 现在,让我们考虑 TIA 的环路增益响应 对反馈电容的影响。 我将首先 假定反馈电容 为 141 飞法拉。 我将稍后 展示, 我是如何针对反馈电容 提出此类值。 检查整个频率的 噪声增益形状。 如前所述, 噪声增益 将在 低频时扁平。 由于反馈电容 远小于 输入电容, 它将不会影响 零频率的位置。 但是, 在 1/2π RFCF 的频率下, 即 10 MHz 频率下, 反馈电阻 与反馈电容的阻抗 将变为相等。 在较高频率处, 由于 Rf 与 Cf 并联, RF 不再会 影响噪声增益。 因此,产生的 噪声增益 将由总计为 C 的 输入电容以及 反馈电容 CF 确定。 由于这两个电容器的 阻抗幅度 将以相同 频率变化, 噪声增益将变平, 如图中所示。 反馈电容 因此具有 在噪声增益中插入池的效果, 这将继而纠正 环路增益曲线上 回收相位。 如图中所示, 环路增益交叉点 将在接近极点频率的 位置处出现, 大约 10MHz。 现在,让我们来看看 相位响应。 比极点频率 低十倍频程, 由于存在反馈电容, 环路增益相 将开始以 45 度/十倍频程的速率增加。 在 10MHz 处出现 环路增益交叉时, 覆盖足够 相位的环路增益 可提供大约 65° 的相比角, 因此为我们带来 巴特沃斯型响应。 将反馈电容 设为远低于 该 141 飞法拉的值 将进一步 推动 极点频率。 这将导致 相补角不够理想。 与此类似, 将反馈电容 提高到远高于 141 飞法拉的值, 这将使极点频率 更接近零频率。 这将导致 过阻尼响应。 但是,闭环 带宽 将比过去 低得多。 结果变为, 对于巴特沃斯型响应, 相补角 为 65°, 您必须 根据此方程式 将反馈电容 设为相等, 其中 f -3 dB 是 由运算放大器增益带宽与 噪声增益中 零频率的几何平均数 得出。 我就是这样 得出 141 飞法拉的 反馈电容值。 在此幻灯片中, 我仿真 互阻抗放大器 在我更改反馈电容值后的 环路增益和 闭环带宽。 将反馈 电容值 提高到 280 飞法拉 会将极点频率拉至低值, 导致 相补角和 过阻尼响应增加。 当反馈电容器的 值降低时, 反之亦然。 极点在频率方面 会进一步外推, 从而缩减相补角 和频率响应 将显示超额峰值。 用于仿真闭环 互阻抗增益的电路 如此处所示。 最后, 我总结了 变更反馈 电容值的结果。 如您所见, 对于某个反馈电容值, 巴特沃斯型 响应的一半, 相补角将下降至大约 39°。 但是,闭环 带宽 已从 10 MHz 增至 14 MHz。 另一方面, 反馈电容值翻倍 导致相补角 接近 90°。 不过,带宽的 减幅过半, 降至 4MHz。 这样,通过更改 反馈电容值, 设计人员可通过 控制相补角 来控制 想要在电路中 实现的脉冲响应, 或者可控制所需的 闭环带宽。 解补偿运算放大器 是单位增益不稳定的 放大器。 单位增益稳定放大器 具有第二个 AOL 极点, 该极点通常在 零 dB 交叉处出现。 另一方面, 解补偿运算放大器 将在其单位 增益带宽前, 出现其第二个极点。 解补偿运算 放大器使 IC 设计人员 能够在相同静态电流下是选择 相对更高带宽、更低噪声的放大器 还是选择单位增益稳定的 对应放大器之间做出 折衷。 我们现在比较 两个 TI 放大器, OPS 656 为单位增益稳定, OPS 657 则在增益为 7 时 稳定。 如您可见,在两个案例中, 消耗的静态电流均为 14 毫安。 然而, 在 OPS 657 案例中, 对于 656, 增益带宽积 约为 1.6GHz 对比 230MHz。 与此类似,657 的噪声 比 OPS 656 的噪声 要低得多。 看一看开环 增益幅度曲线, 您将注意到 在 OPS 656 中, 即此处上方的 蓝色曲线, 斜率从大约 20 dB/十倍频程 降低到每十倍频 40 dB, 接近零 db 交叉处。 但是, 在 OPS 657 中, 其出现要早得多。 现在,让我们看看 补偿放大器 更适合 TIA 应用。 如先前 所讨论, TIA 的噪声增益 将受到输入和 反馈电容的影响。 由于对噪声增益 曲线存在此影响, 在幅度大于零 dB 处 将出现相补角。 对于适当补偿的 放大器, 在增益为 1 加上总计 C 除以反馈 C 得出的增益处 通常将出现交叉。 在 OPS 657 的案例中, 噪声增益曲线 将在 37 dB 处与 开环增益曲线相交, 而第二个开环增益 极点在 19 dB 处出现。 这表示存在 -20 dB/十倍频程接近率, 而这意味着稳定的 运算放大器配置。 请记住, 对于巴特沃斯型响应, 相补角 为 65°, 闭环带宽 由该方程式得出。 要实现 该闭环带宽的 相应 反馈电容 由此处的方程式得出。 现在,我已扫描从 1 千欧姆 至 10 兆欧姆的 反馈电阻, 并抽取了 所需的闭环带宽 和反馈电容值。 我已检查了 四个不同的 具有增益带宽的放大器产品, 频率范围涵盖 500MHz 至 2GHz,应有尽有。 正如预期,更高的 增益带宽放大器 能够产生 更高的闭环带宽。 在各自情况下, 我假定输入电容为 10 皮法拉。 随着输入 电容值增加, 可实现的带宽 将减少。 现在,让我们 来看看反馈电容。 闭环带宽 越高, 获得巴特沃斯响应 所需的反馈电容值 就变得 极小, 并可以是数十飞法拉。 在此类情况下, 此类反馈电容值 可能就很难 在硬件中实现。 实现极低的 反馈电容值 可能不切实际, 因为没有足够的 0.2 皮法拉以下的 芯片电容器, 并且因为 存在 PCB 寄生, 这使外部 电容器显得逊色。 此外, 反馈电阻器包 自身具有自己的 寄生电容, 应将该电容值加上, 从而防止 设计人员得出 极低的反馈 电容值。 通过移除 低于放大器、 反向输入、其输出以及 反馈路径下的接地平面和电源平面, 可以减小 寄生电流。 有可能通过 使用电容 T 形网络, 实现极小的 电容器值, 如此电路中所示, 其有效电容 由此方程式给出。 例如,C1 等于 C2 等于 1 皮法拉, C3 等于 47 皮法拉, 该 T 形网络的 等效电容 结果是 20 飞法拉。 同样,要获得 极大的反馈电阻, 可使用电阻器 树形网络, 其中冷却剂电阻 由此方程式给出。 同样,如果 R1 等于 R2, 等于 100 千欧姆, 且 R3 等于 10 千欧姆, 则可获得等效电阻 或 1.2 兆欧姆。 现在,让我们看看 影响互阻抗放大器 总输出噪声的 各种元件。 存在 4 个 影响因素。 还有放大器的 电压噪声 影响的噪声, 运算放大器的 电流噪声 影响的噪声, 反馈电阻器元件 影响的噪声, 并且存在 因放大器的 电压噪声和 噪声增益形状产生的 总输出电压噪声。 我们现在将分别检查 四个影响因子中的 一个。 在极低频率时, 输入电容 与反馈电容 为开路, 从而在放大器的 输出端 将出现增益为 1 的 放大器电压噪声。 在反馈电阻 作用下, 放大器的 电流噪声将提高, 并以其输出的形式出现。 同样, 反馈电阻器的噪声 将直接出现在 放大器的输出端, 且增益为零 dB。 请注意,此处所有 噪声项 均指噪声密度, 其单位为每根赫兹。 在下张幻灯片上 将详细讨论 最终噪声项。 TIA 的噪声增益 将使高频下的 电压噪声 成形。 我已仿真 TIA 的 输出噪声, 假定放大器噪声 为 4 纳伏/根赫兹, 以及输入和输出元件 如先前所述。 TIA 在 低频率下的噪声为 4 纳伏/根赫兹, 与预期相符。 在 100KHz 零频率后, 噪声开始以 20dB/十倍频程的速率增加。 噪声在极点频率处 乘以 37 dB 最大值, 并自此 保持不变。 但是,TIA 的 输出噪声 将以 20dB/十倍频程的速度递减, 因为它存在闭环增益 滚降。 TIA 在高频处的 输出噪声 可按此方程式逼近, 其中 F 通常是 任何 TIA 后滤波的带宽, 或者是 TIA 本身的 闭环带宽。 称作 TIA 噪声的 总输入是 所有单个 影响因素 除以互阻抗增益 RF 结果平方和的 平方根。 重要的是,在 JFET 或 CMOS 输入放大器案例中, 可以忽略 电流噪声项, 因为它极小。 这可导致 TIA 设计人员相信 JFET 或 CMOS 输入放大器 将始终提供 最低噪声解决方案。 但是,这可能不是真的, 因为传统上 BJT 输入放大器 与其 FET 对应产品相比 具有低电压 噪声。 本示例中, 我将双极输入放大器 OPA846 与 JFET 输入放大器 OPA657 进行了对比。 如您在 JFET 的 例子中所见, 电流噪声比 BJT 输入放大器低得多。 然而,其电压 噪声 也比双极输入 放大器高得多。 在本图中, 我将在扫描反馈电阻期间 将 OPA846 和 OPA657 的 输入参考噪声进行了 比较。 在电阻较低处, OPA846 影响的噪声 低于 657, 这是因为此处的 主要因素是电压噪声。 不过,随着反馈 电容值增加, 您可以看到 JFET 输入放大器趋于 变成更佳的解决方案。 这是因为双极输入 放大器 OPA846 的 电流噪声 在反馈电阻的作用下 放大。 它将开始主导 总输出噪声。 总而言之, BJT 输入放大器 在高频的中到高 互阻抗增益应用中 将展示卓越的 SNR 性能, 而 FET 和 CMOS 输入放大器 将在中到低频率 但互阻抗增益极高的应用中 展示卓越的 SNR 性能。 总之, 互阻抗放大器 具有二阶 闭环响应。 封闭型方程式 表明它将使设计人员 能够根据期望的 互阻抗增益 和输入电容 推导带宽和 反馈电容。 由于噪声增益 始终是高值处 穿过开环增益曲线, 因此如得到正确补偿, 运算放大器就 无需稳定的单位增益。 事实上,解补偿放大器 可能会变成更佳。 互阻抗放大器的 输出噪声 在较高频率下将 很大程度上受到 峰值上升电压噪声的影响。 一般而言, 双极输入放大器 更适于在较宽带宽处 提供低至中的 互阻抗增益, 而 JEFT 与 CMOS 输入放大器 更适于在较低 带宽处提供高 高互阻抗增益。 当使用 BJT 输入放大器时, 必须将等于 反馈电阻的电阻器 放在介于从运算 放大器非反向终端至 接地之间的位置。 这用于抵消 BJT 放大器 偏移电流的 效应。 除此之外, 将旁路电容器 并联非反向 终端上的电阻器 以降低较高 频率处电阻器的 噪声影响量。 我在此列出了 一些其他资源 以帮助您 设计 TIA。 此博客文章包含 指向 Excel 计算器的链接, 其中包含在此演示中 讨论的方程式。 我希望您觉得这对于 简化您的设计有用。 此外,在 TI 网站上 还提供了完整的 端到端参考设计 以使您能够评估 光学前端的 系统性能。 该设计包含激光 及其激光驱动器、 带偏置电源的 光电二极管、 放大器信号链以及 包含时钟电路、 FGA 以及 内存的 ADC 板。 我希望您觉得这 有助于评估您的系统 性能。 谢谢。

大家好!

我叫 Samir Cherian,

是德州仪器 (TI) 高速放大器团队的

应用工程师。

今天,我将展示 有关如何

优化互阻抗放大器 以用于高速应用的

定性分析。

互阻抗 放大器

用于转换来自 光学传感器的

输出电流,例如, 将光电二极管变为电压。

TIA 的概念简单。

它们依据欧姆定律在运算放大器中 使用反馈电阻器

将电流 转为电压。

但是,当尝试 最大程度提高

高速系统的 性能时,

分析会变得相当复杂。

在本演示中, 我将介绍理论设计

概念, 然后在 Spice 环境中

应用这些概念。

我们将在本演示中 着重介绍三个领域 -

介绍影响其 频率响应和形状的

TIA 和 因素。

我将深入介绍 可能影响放大器稳定性的

每个因素。

然后,我将最终 检查影响 TIA 中

总体噪声的 单独元素。

您还将在下面 找到两个链接。

第一个链接是对 基础放大器稳定性的回顾。

第二个链接是 应用手册,

它提供了 对互阻抗放大器

稳定性的 详细量化分析。

检测和放大 来自光电二极管的

高速小电流 可具有较高的设计难度。

光电二极管、 放大器以及印刷电路板的

寄生电容 相互之间

以及与反馈电阻之间 相互作用,

以修改 TIA 的 频率响应形状。

该图显示了 影响放大器

稳定性的 主要元素。

光电二极管具有 可从 1 皮法拉至

数百皮法拉不等的 寄生电容,

具体取决于其敏感度。

此外,运算放大器具有 共模和差分输入电容,

同样也需要 加以考虑。

此外,PCB 也具有一些

寄生电容。

在本演示中, 我将三个电容

合为一个单输入电容, 记为总计 C。

除在放大器的 输入节点上的

电容器存在寄生效应外, 在 PCB 以及

反馈电阻器封装中 也有反馈寄生效应,

稍后, 我将讨论

与射频 同时增加的

物理电容器。

TIA 的带宽由 三个关键元素

确定。

首选是总输入 电容 -

这包括光电二极管电容、 运算放大器输入电容,

以及任何 寄生 PCB 电容。

其次是符合期望的互阻抗增益。

最后,同样还有运算 放大器的带宽积。

运算放大器的 带宽增益越高,

产生的闭环带宽 互阻抗带宽就越高。

以上三个因素 相互关联。

对于选定的 特定运算放大器,

以互阻抗 增益为目标

就会设定 最大带宽,

或反之,以该带宽为目标 就会将设定最大增益。

我将使用 TINA-Spice 仿真软件展示 TIA 的

基础构建块以及 不同的组件如何影响

TIA 的稳定性和噪声。

在本演示中, 我将着重

介绍针对目标 互阻抗增益

实现 65° 相补角的 巴特沃斯型响应形状,

然后,我将推导 闭环响应

和噪声。

当尝试选择互阻抗 设计的运算放大器时,

务必了解三件事, 光电二极管

电容、所需的 互阻抗

增益,以及所需的 闭环带宽。

放大器的稳定性 取决于其环路增益,

其定义为 开环增益

AOL 与 反馈因子 β 的乘积。

运算放大器的 反馈因子是

其噪声增益的倒数。

为仿真 环路增益,

我将使用 图中所示的

两个电路配置。

DUT 配置用于 提取运算放大器的

开路增益幅度和相位。

图中显示的 大电容器和电感器

将配置开路中的 运算放大器

以提取其 AOL。

理想的 放大器配置

使用理想的运算放大器 提取噪声增益,

这是围绕运算 放大器无源元件的

功能。

在第一种情况下, 我将假定 DUT

没有任何输入电容 和理想的光电二极管,

没有寄生电容。

在此案例中, 没有任何输入和反馈

电容器, 放大器采用单元增益缓冲器

配置。

噪声增益的 幅度在整个频率中

并没有扁平为零 dB, 其相位也是如此。

以 dB 表示的 环路增益是

AOL 与 β 之和。

由于 β 是 0dB, 环路增益将跟踪开环增益。

如要确定 相补角,

查找 AOL 曲线 与 β 曲线相交处的

频率。

该点可称为 回路增益交叉点。

在此案例中, 环路增益交叉点

出现在 运算放大器的

增益带宽积,即 1GHz。

现在,找到交叉频率处 环路增益的

相位。

在本例中,它为 90°, 因为系统是

单极性放大器。

相补角为 180°

减去 90° 相移, 由于其为单极性,

这可产生 90° 的 相补角。

放大器 因此稳定。

现在让我们考虑 光电二极管和运算放大器的

输入电容。

我将假定总输入 电容为 10 皮法,

并且目标互阻抗 增益为 159 千欧姆。

开环增益 曲线将保持为

上一例中的 曲线不变,

如红色曲线所示。

出于噪音增益 考虑,

10 皮法拉 输入电容器

已添加至理想放大器的 反向终端处。

现在,让我们看看跨频率 噪声增益行为。

在低频时, 10 皮法拉电容

阻抗 将极高,

并因此将被 视为开路。

在低频时, 放大器

将如前用作 空增益缓冲器,

此增益幅度为零 dB。

随着频率上升, 输出电容器的阻抗

将开始降低。

在 1/2π RFC(总计)的 频率下,

即 100KHz 频率下, 阻抗电容器

等于反馈 电阻器的值。

这是噪声增益 曲线上的零。

在零频率以上, 噪声增益

将开始以 20 dB/十倍频程的速率增加。

总相位 会发生变化,

因为它将是 0° 至 90°。

现在,让我们考虑 环路增益交叉。

我们使开环增益 降低 20dB/十倍频程。

它将在 1GHz 处 经过 0db 线。

与此类似, 噪声增益曲线

将开始在 100KHz 处 以 20dB/十倍频程的速率增加。

交点 即环路增益交叉点,

它是 100KHz 处 零频率与

1GHz 处放大器 增益带宽积的

几何平均数。

此环路增益因此 将在 10MHz 交叉。

请记住,噪声增益中的零 是 β 中的极。

产生的环路增益 确实有双极响应。

现在我们需要了解一下幅度。

噪声增益 始于 100KHz,

并以 20 dB/十倍频程的 速率增加,

而 AOL 以 -20 dB/十倍 频程的速度降低。

环路增益在 环路增益交叉频率处

具有 -40 dB 的 接近率。

这通常指示存在 潜在的不稳定性。

现在,让我们来看看 环路增益的相位。

正如此前的情况, 1KHz 的主极点

将影响 90° 的总相移,

该相移在 10KHz 处结束。

但是,现在由于 在 100KHz 处为零,

相位将 持续减少。

在 1MHz 时, 总相移

接近 180°。

请记住,在此之前, 环路增益交叉处

为 10MHz。

在该频率处, 围绕反馈环路的

总相移 是 180°,

这表示产生的 相补角是 0°,

并且 TIA 现在 将变得不稳定。

现在,让我们考虑 TIA 的环路增益响应

对反馈电容的影响。

我将首先 假定反馈电容

为 141 飞法拉。

我将稍后 展示,

我是如何针对反馈电容 提出此类值。

检查整个频率的 噪声增益形状。

如前所述, 噪声增益

将在 低频时扁平。

由于反馈电容 远小于

输入电容, 它将不会影响

零频率的位置。

但是, 在 1/2π RFCF 的频率下,

即 10 MHz 频率下,

反馈电阻 与反馈电容的阻抗

将变为相等。

在较高频率处, 由于 Rf 与 Cf 并联,

RF 不再会 影响噪声增益。

因此,产生的 噪声增益

将由总计为 C 的 输入电容以及

反馈电容 CF 确定。

由于这两个电容器的 阻抗幅度

将以相同 频率变化,

噪声增益将变平, 如图中所示。

反馈电容 因此具有

在噪声增益中插入池的效果, 这将继而纠正

环路增益曲线上 回收相位。

如图中所示, 环路增益交叉点

将在接近极点频率的 位置处出现,

大约 10MHz。

现在,让我们来看看 相位响应。

比极点频率 低十倍频程,

由于存在反馈电容, 环路增益相

将开始以 45 度/十倍频程的速率增加。

在 10MHz 处出现 环路增益交叉时,

覆盖足够 相位的环路增益

可提供大约 65° 的相比角,

因此为我们带来 巴特沃斯型响应。

将反馈电容 设为远低于

该 141 飞法拉的值 将进一步

推动 极点频率。

这将导致 相补角不够理想。

与此类似, 将反馈电容

提高到远高于 141 飞法拉的值,

这将使极点频率 更接近零频率。

这将导致 过阻尼响应。

但是,闭环 带宽

将比过去 低得多。

结果变为, 对于巴特沃斯型响应,

相补角 为 65°,

您必须 根据此方程式

将反馈电容 设为相等,

其中 f -3 dB 是 由运算放大器增益带宽与

噪声增益中 零频率的几何平均数

得出。

我就是这样 得出 141 飞法拉的

反馈电容值。

在此幻灯片中, 我仿真

互阻抗放大器 在我更改反馈电容值后的

环路增益和 闭环带宽。

将反馈 电容值

提高到 280 飞法拉 会将极点频率拉至低值,

导致 相补角和

过阻尼响应增加。

当反馈电容器的 值降低时,

反之亦然。

极点在频率方面 会进一步外推,

从而缩减相补角 和频率响应

将显示超额峰值。

用于仿真闭环 互阻抗增益的电路

如此处所示。

最后, 我总结了

变更反馈 电容值的结果。

如您所见, 对于某个反馈电容值,

巴特沃斯型 响应的一半,

相补角将下降至大约 39°。

但是,闭环 带宽

已从 10 MHz 增至 14 MHz。

另一方面, 反馈电容值翻倍

导致相补角 接近 90°。

不过,带宽的 减幅过半,

降至 4MHz。

这样,通过更改 反馈电容值,

设计人员可通过 控制相补角

来控制 想要在电路中

实现的脉冲响应, 或者可控制所需的

闭环带宽。

解补偿运算放大器 是单位增益不稳定的

放大器。

单位增益稳定放大器 具有第二个 AOL 极点,

该极点通常在 零 dB 交叉处出现。

另一方面, 解补偿运算放大器

将在其单位 增益带宽前,

出现其第二个极点。

解补偿运算 放大器使 IC 设计人员

能够在相同静态电流下是选择 相对更高带宽、更低噪声的放大器

还是选择单位增益稳定的 对应放大器之间做出

折衷。

我们现在比较 两个 TI 放大器,

OPS 656 为单位增益稳定, OPS 657 则在增益为 7 时

稳定。

如您可见,在两个案例中, 消耗的静态电流均为

14 毫安。

然而, 在 OPS 657 案例中,

对于 656, 增益带宽积

约为 1.6GHz 对比 230MHz。

与此类似,657 的噪声 比 OPS 656 的噪声

要低得多。

看一看开环 增益幅度曲线,

您将注意到 在 OPS 656 中,

即此处上方的 蓝色曲线,

斜率从大约 20 dB/十倍频程 降低到每十倍频 40 dB,

接近零 db 交叉处。

但是, 在 OPS 657 中,

其出现要早得多。

现在,让我们看看 补偿放大器

更适合 TIA 应用。

如先前 所讨论,

TIA 的噪声增益 将受到输入和

反馈电容的影响。

由于对噪声增益 曲线存在此影响,

在幅度大于零 dB 处 将出现相补角。

对于适当补偿的 放大器,

在增益为 1 加上总计 C 除以反馈 C 得出的增益处

通常将出现交叉。

在 OPS 657 的案例中, 噪声增益曲线

将在 37 dB 处与 开环增益曲线相交,

而第二个开环增益 极点在 19 dB 处出现。

这表示存在 -20 dB/十倍频程接近率,

而这意味着稳定的 运算放大器配置。

请记住, 对于巴特沃斯型响应,

相补角 为 65°,

闭环带宽 由该方程式得出。

要实现 该闭环带宽的

相应 反馈电容

由此处的方程式得出。

现在,我已扫描从 1 千欧姆 至 10 兆欧姆的

反馈电阻, 并抽取了

所需的闭环带宽 和反馈电容值。

我已检查了 四个不同的

具有增益带宽的放大器产品, 频率范围涵盖 500MHz

至 2GHz,应有尽有。

正如预期,更高的 增益带宽放大器

能够产生 更高的闭环带宽。

在各自情况下, 我假定输入电容为

10 皮法拉。

随着输入 电容值增加,

可实现的带宽 将减少。

现在,让我们 来看看反馈电容。

闭环带宽 越高,

获得巴特沃斯响应 所需的反馈电容值

就变得 极小,

并可以是数十飞法拉。

在此类情况下, 此类反馈电容值

可能就很难 在硬件中实现。

实现极低的 反馈电容值

可能不切实际, 因为没有足够的

0.2 皮法拉以下的 芯片电容器,

并且因为 存在 PCB 寄生,

这使外部 电容器显得逊色。

此外, 反馈电阻器包

自身具有自己的 寄生电容,

应将该电容值加上, 从而防止

设计人员得出 极低的反馈

电容值。

通过移除 低于放大器、

反向输入、其输出以及 反馈路径下的接地平面和电源平面,

可以减小 寄生电流。

有可能通过 使用电容 T 形网络,

实现极小的 电容器值,

如此电路中所示, 其有效电容

由此方程式给出。

例如,C1 等于 C2 等于 1 皮法拉,

C3 等于 47 皮法拉,

该 T 形网络的 等效电容

结果是 20 飞法拉。

同样,要获得 极大的反馈电阻,

可使用电阻器 树形网络,

其中冷却剂电阻 由此方程式给出。

同样,如果 R1 等于 R2,

等于 100 千欧姆, 且 R3 等于 10 千欧姆,

则可获得等效电阻 或 1.2 兆欧姆。

现在,让我们看看 影响互阻抗放大器

总输出噪声的 各种元件。

存在 4 个 影响因素。

还有放大器的 电压噪声

影响的噪声, 运算放大器的

电流噪声 影响的噪声,

反馈电阻器元件 影响的噪声,

并且存在 因放大器的

电压噪声和 噪声增益形状产生的

总输出电压噪声。

我们现在将分别检查 四个影响因子中的

一个。

在极低频率时, 输入电容

与反馈电容 为开路,

从而在放大器的 输出端

将出现增益为 1 的 放大器电压噪声。

在反馈电阻 作用下,

放大器的 电流噪声将提高,

并以其输出的形式出现。

同样, 反馈电阻器的噪声

将直接出现在 放大器的输出端,

且增益为零 dB。

请注意,此处所有 噪声项

均指噪声密度, 其单位为每根赫兹。

在下张幻灯片上 将详细讨论

最终噪声项。

TIA 的噪声增益 将使高频下的

电压噪声 成形。

我已仿真 TIA 的 输出噪声,

假定放大器噪声 为 4 纳伏/根赫兹,

以及输入和输出元件 如先前所述。

TIA 在 低频率下的噪声为

4 纳伏/根赫兹, 与预期相符。

在 100KHz 零频率后,

噪声开始以 20dB/十倍频程的速率增加。

噪声在极点频率处 乘以 37 dB 最大值,

并自此 保持不变。

但是,TIA 的 输出噪声

将以 20dB/十倍频程的速度递减, 因为它存在闭环增益

滚降。

TIA 在高频处的 输出噪声

可按此方程式逼近, 其中 F 通常是

任何 TIA 后滤波的带宽,

或者是 TIA 本身的 闭环带宽。

称作 TIA 噪声的 总输入是

所有单个 影响因素

除以互阻抗增益 RF 结果平方和的

平方根。

重要的是,在 JFET 或 CMOS 输入放大器案例中,

可以忽略 电流噪声项,

因为它极小。

这可导致 TIA 设计人员相信

JFET 或 CMOS 输入放大器

将始终提供 最低噪声解决方案。

但是,这可能不是真的, 因为传统上 BJT 输入放大器

与其 FET 对应产品相比 具有低电压

噪声。

本示例中, 我将双极输入放大器

OPA846 与 JFET 输入放大器 OPA657

进行了对比。

如您在 JFET 的 例子中所见,

电流噪声比 BJT 输入放大器低得多。

然而,其电压 噪声

也比双极输入 放大器高得多。

在本图中, 我将在扫描反馈电阻期间

将 OPA846 和 OPA657 的 输入参考噪声进行了

比较。

在电阻较低处, OPA846 影响的噪声

低于 657,

这是因为此处的 主要因素是电压噪声。

不过,随着反馈 电容值增加,

您可以看到 JFET 输入放大器趋于

变成更佳的解决方案。

这是因为双极输入 放大器 OPA846 的

电流噪声 在反馈电阻的作用下

放大。

它将开始主导 总输出噪声。

总而言之, BJT 输入放大器

在高频的中到高 互阻抗增益应用中

将展示卓越的 SNR 性能,

而 FET 和 CMOS 输入放大器

将在中到低频率 但互阻抗增益极高的应用中

展示卓越的 SNR 性能。

总之, 互阻抗放大器

具有二阶 闭环响应。

封闭型方程式 表明它将使设计人员

能够根据期望的 互阻抗增益

和输入电容 推导带宽和

反馈电容。

由于噪声增益 始终是高值处

穿过开环增益曲线, 因此如得到正确补偿,

运算放大器就 无需稳定的单位增益。

事实上,解补偿放大器 可能会变成更佳。

互阻抗放大器的 输出噪声

在较高频率下将 很大程度上受到

峰值上升电压噪声的影响。

一般而言, 双极输入放大器

更适于在较宽带宽处 提供低至中的

互阻抗增益, 而 JEFT 与 CMOS 输入放大器

更适于在较低 带宽处提供高

高互阻抗增益。

当使用 BJT 输入放大器时,

必须将等于 反馈电阻的电阻器

放在介于从运算 放大器非反向终端至

接地之间的位置。

这用于抵消 BJT 放大器 偏移电流的

效应。

除此之外, 将旁路电容器

并联非反向 终端上的电阻器

以降低较高 频率处电阻器的

噪声影响量。

我在此列出了 一些其他资源

以帮助您 设计 TIA。

此博客文章包含 指向 Excel 计算器的链接,

其中包含在此演示中 讨论的方程式。

我希望您觉得这对于 简化您的设计有用。

此外,在 TI 网站上

还提供了完整的 端到端参考设计

以使您能够评估 光学前端的

系统性能。

该设计包含激光 及其激光驱动器、

带偏置电源的 光电二极管、

放大器信号链以及 包含时钟电路、

FGA 以及 内存的 ADC 板。

我希望您觉得这 有助于评估您的系统

性能。

谢谢。

手机看

扫码用手机观看

-

未学习 高速Transimpedence放大器设计流程

未学习 高速Transimpedence放大器设计流程

00:25:31

播放中

视频简介

视频简介

高速Transimpedence放大器设计流程

所属课程:高速Transimpedence放大器设计流程

发布时间:2019.03.11

视频集数:1

本节视频时长:00:25:31

跨阻放大器虽然在概念上很简单,但在尝试在噪声,带宽和脉冲响应方面最大化系统性能时,可以进行相当复杂的分析。 演讲将涵盖理论设计概念。 然后,该理论将应用于SPICE环境,以展示工程师可用于优化TIA应用的各种自由度。 提供的示例将使观众能够在设计TIA时直观地了解各种权衡。