PRU-ICSS:将处理器与多个ADC连接

播放器加载失败: 未检测到Flash Player,请到

安装

将在30s后自动为您播放下一课程

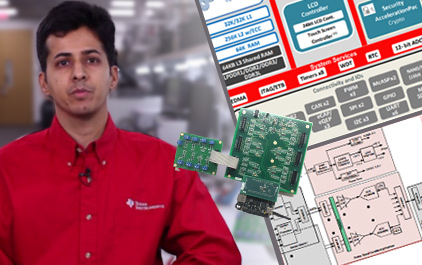

[音乐播放] 您好,我是 Prasana。 在这段视频中, 我将向您介绍 一个 Sitara 系列处理器中的子系统, 即 PRU-ICSS。 特别是,我将向您展示 如何使用 PRU-ICSS 来连接处理器 和多种 ADC,而非 FPGA。 让我们来看一下设置方法。 我们这里有四块电路板。 一块传感器板、 一块 BeagleBone Black 板、 还有一块接口板。 其中传感器板用于 连接到 PT 和 CT 的次级侧。 将输出连接至 模拟前端卡 此卡配备 6 个数据转换器、 1 个增益级和 1 个驱动级。 模拟前端卡的输出 通过接口卡 与 BeagleBone Black EVM 板连接。 现在,让我们 看一下方框图。 在左侧,您可以 看到 6 个 ADC 每个 ADC 都具有 8 个通道 或者说,总共有 48 个通道。 每个 ADC 的运行速率为 256kSPS。 右侧是 Sitara 处理器。 左侧的来自 PRU 子系统的 GPIO 与全部的 6 个通道相连。 每个 PRU 有两个内核。 第一个内核与 ADC 的 SPI 接口相连 并且单独控制 ADC 的 时序和 同步。 第二个内核用于 处理捕获的数据。 这两个内核结合起来 可以帮助我们估算 内核一的信号频率, 并改变内核零的采样率。 有三个主要优势。 第一,ADC 吞吐量增加。 PRU-ICSS 可以 在 ADC 接口 独立控制时序。 SPI 和 数据总线不相连 从而使得吞吐量 明显提高。 第二,处理器得到解放。 处理器再也不用 管理资源配置, 因此可以 释放带宽。 第三,数据采集性能提高。 相干的采样 通过 利用 PRU-ICSS 的内核一和内核零 将频谱泄露降低最低。 有关更多信息, 请访问下方链接 或者在 ti.com.cn 搜索 TIDA-01555。 谢谢您观看本视频。 [音乐播放]

[音乐播放] 您好,我是 Prasana。 在这段视频中, 我将向您介绍 一个 Sitara 系列处理器中的子系统, 即 PRU-ICSS。 特别是,我将向您展示 如何使用 PRU-ICSS 来连接处理器 和多种 ADC,而非 FPGA。 让我们来看一下设置方法。 我们这里有四块电路板。 一块传感器板、 一块 BeagleBone Black 板、 还有一块接口板。 其中传感器板用于 连接到 PT 和 CT 的次级侧。 将输出连接至 模拟前端卡 此卡配备 6 个数据转换器、 1 个增益级和 1 个驱动级。 模拟前端卡的输出 通过接口卡 与 BeagleBone Black EVM 板连接。 现在,让我们 看一下方框图。 在左侧,您可以 看到 6 个 ADC 每个 ADC 都具有 8 个通道 或者说,总共有 48 个通道。 每个 ADC 的运行速率为 256kSPS。 右侧是 Sitara 处理器。 左侧的来自 PRU 子系统的 GPIO 与全部的 6 个通道相连。 每个 PRU 有两个内核。 第一个内核与 ADC 的 SPI 接口相连 并且单独控制 ADC 的 时序和 同步。 第二个内核用于 处理捕获的数据。 这两个内核结合起来 可以帮助我们估算 内核一的信号频率, 并改变内核零的采样率。 有三个主要优势。 第一,ADC 吞吐量增加。 PRU-ICSS 可以 在 ADC 接口 独立控制时序。 SPI 和 数据总线不相连 从而使得吞吐量 明显提高。 第二,处理器得到解放。 处理器再也不用 管理资源配置, 因此可以 释放带宽。 第三,数据采集性能提高。 相干的采样 通过 利用 PRU-ICSS 的内核一和内核零 将频谱泄露降低最低。 有关更多信息, 请访问下方链接 或者在 ti.com.cn 搜索 TIDA-01555。 谢谢您观看本视频。 [音乐播放]

[音乐播放]

您好,我是 Prasana。

在这段视频中, 我将向您介绍

一个 Sitara 系列处理器中的子系统,

即 PRU-ICSS。

特别是,我将向您展示 如何使用 PRU-ICSS

来连接处理器

和多种 ADC,而非 FPGA。

让我们来看一下设置方法。

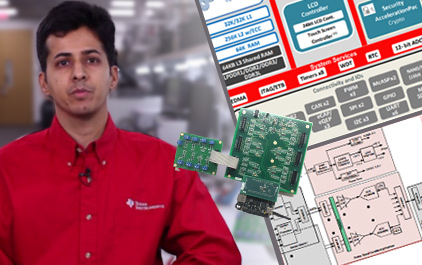

我们这里有四块电路板。

一块传感器板、 一块 BeagleBone Black 板、

还有一块接口板。

其中传感器板用于

连接到 PT 和 CT 的次级侧。

将输出连接至 模拟前端卡

此卡配备 6 个数据转换器、 1 个增益级和 1 个驱动级。

模拟前端卡的输出 通过接口卡

与 BeagleBone Black EVM 板连接。

现在,让我们 看一下方框图。

在左侧,您可以 看到 6 个 ADC

每个 ADC 都具有 8 个通道 或者说,总共有 48 个通道。

每个 ADC 的运行速率为 256kSPS。

右侧是 Sitara 处理器。

左侧的来自 PRU 子系统的 GPIO

与全部的 6 个通道相连。

每个 PRU 有两个内核。

第一个内核与 ADC 的 SPI 接口相连

并且单独控制 ADC 的 时序和

同步。

第二个内核用于 处理捕获的数据。

这两个内核结合起来 可以帮助我们估算

内核一的信号频率, 并改变内核零的采样率。

有三个主要优势。

第一,ADC 吞吐量增加。

PRU-ICSS 可以 在 ADC 接口

独立控制时序。

SPI 和 数据总线不相连

从而使得吞吐量

明显提高。

第二,处理器得到解放。

处理器再也不用 管理资源配置,

因此可以 释放带宽。

第三,数据采集性能提高。

相干的采样 通过

利用 PRU-ICSS 的内核一和内核零 将频谱泄露降低最低。

有关更多信息, 请访问下方链接

或者在 ti.com.cn 搜索 TIDA-01555。

谢谢您观看本视频。

[音乐播放]

[音乐播放] 您好,我是 Prasana。 在这段视频中, 我将向您介绍 一个 Sitara 系列处理器中的子系统, 即 PRU-ICSS。 特别是,我将向您展示 如何使用 PRU-ICSS 来连接处理器 和多种 ADC,而非 FPGA。 让我们来看一下设置方法。 我们这里有四块电路板。 一块传感器板、 一块 BeagleBone Black 板、 还有一块接口板。 其中传感器板用于 连接到 PT 和 CT 的次级侧。 将输出连接至 模拟前端卡 此卡配备 6 个数据转换器、 1 个增益级和 1 个驱动级。 模拟前端卡的输出 通过接口卡 与 BeagleBone Black EVM 板连接。 现在,让我们 看一下方框图。 在左侧,您可以 看到 6 个 ADC 每个 ADC 都具有 8 个通道 或者说,总共有 48 个通道。 每个 ADC 的运行速率为 256kSPS。 右侧是 Sitara 处理器。 左侧的来自 PRU 子系统的 GPIO 与全部的 6 个通道相连。 每个 PRU 有两个内核。 第一个内核与 ADC 的 SPI 接口相连 并且单独控制 ADC 的 时序和 同步。 第二个内核用于 处理捕获的数据。 这两个内核结合起来 可以帮助我们估算 内核一的信号频率, 并改变内核零的采样率。 有三个主要优势。 第一,ADC 吞吐量增加。 PRU-ICSS 可以 在 ADC 接口 独立控制时序。 SPI 和 数据总线不相连 从而使得吞吐量 明显提高。 第二,处理器得到解放。 处理器再也不用 管理资源配置, 因此可以 释放带宽。 第三,数据采集性能提高。 相干的采样 通过 利用 PRU-ICSS 的内核一和内核零 将频谱泄露降低最低。 有关更多信息, 请访问下方链接 或者在 ti.com.cn 搜索 TIDA-01555。 谢谢您观看本视频。 [音乐播放]

[音乐播放]

您好,我是 Prasana。

在这段视频中, 我将向您介绍

一个 Sitara 系列处理器中的子系统,

即 PRU-ICSS。

特别是,我将向您展示 如何使用 PRU-ICSS

来连接处理器

和多种 ADC,而非 FPGA。

让我们来看一下设置方法。

我们这里有四块电路板。

一块传感器板、 一块 BeagleBone Black 板、

还有一块接口板。

其中传感器板用于

连接到 PT 和 CT 的次级侧。

将输出连接至 模拟前端卡

此卡配备 6 个数据转换器、 1 个增益级和 1 个驱动级。

模拟前端卡的输出 通过接口卡

与 BeagleBone Black EVM 板连接。

现在,让我们 看一下方框图。

在左侧,您可以 看到 6 个 ADC

每个 ADC 都具有 8 个通道 或者说,总共有 48 个通道。

每个 ADC 的运行速率为 256kSPS。

右侧是 Sitara 处理器。

左侧的来自 PRU 子系统的 GPIO

与全部的 6 个通道相连。

每个 PRU 有两个内核。

第一个内核与 ADC 的 SPI 接口相连

并且单独控制 ADC 的 时序和

同步。

第二个内核用于 处理捕获的数据。

这两个内核结合起来 可以帮助我们估算

内核一的信号频率, 并改变内核零的采样率。

有三个主要优势。

第一,ADC 吞吐量增加。

PRU-ICSS 可以 在 ADC 接口

独立控制时序。

SPI 和 数据总线不相连

从而使得吞吐量

明显提高。

第二,处理器得到解放。

处理器再也不用 管理资源配置,

因此可以 释放带宽。

第三,数据采集性能提高。

相干的采样 通过

利用 PRU-ICSS 的内核一和内核零 将频谱泄露降低最低。

有关更多信息, 请访问下方链接

或者在 ti.com.cn 搜索 TIDA-01555。

谢谢您观看本视频。

[音乐播放]

手机看

扫码用手机观看

-

未学习 PRU-ICSS:将处理器与多个ADC连接

未学习 PRU-ICSS:将处理器与多个ADC连接

00:02:33

播放中

视频简介

视频简介

PRU-ICSS:将处理器与多个ADC连接

所属课程:PRU-ICSS:将处理器与多个ADC连接

发布时间:2018.06.25

视频集数:1

本节视频时长:00:02:33

TI的Sitara™处理器具有独特的子系统,称为可编程实时单元工业通信子系统(PRU-ICSS),可实现实时工业通信协议的集成,并且无需外部ASIC或FPGA。 本视频演示了PRU-ICSS子系统如何在处理器和多个模数转换器(ADC)之间提供灵活的接口,以提高数据采集性能。 Tune正在审查PRU-ICSS的优势,并使用单个PRU-ICSS从六个8通道ADC中采集数据,每个采样率为256ksps。