1.1 TI 高精度实验室-时钟和计时:系统概述

Loading the player...

将在30s后自动为您播放下一课程

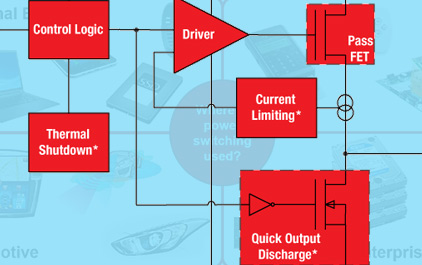

大家好,欢迎观看 TI 高精度实验室。 当大家听到时钟和 计时系统这两个术语时, 会想到什么呢? 实际上这涉及很多东西。 但是,如何知道 哪个时钟最合适呢? 本入门培训模块概述了 不同时钟和计时功能的 应用。 红色显示的 锁相环和 VCO 功能 是各种时钟 解决方案中使用的核心 构建块。 这些 PLL 和 VCO 功能 以及关键性能参数 在其他高精度 实验室培训模块中 进行了讨论。 什么是时钟? 时钟在电子系统中 提供脉冲。 在信号链中,时钟 是关键构建块, 可为 ADC、DAC、 处理器和任何接口媒体 提供参考采样计时。 任何需要 参考时间进行 同步、执行命令 和传输数据的系统 都需要时钟。 它们向各种设备 提供频率输入, 使它们能够 执行预期的功能。 时钟也可以 用作功能块, 该功能块将信号源 进行倍频和分频, 从而扇出特定频率, 甚至几个不同的频率。 如果系统中 需要处理器、 高速接口或 数据转换器, 则需要时钟解决方案。 我们先来介绍 最常用的功能 - 晶体 振荡器。 关键参数 是以 PPM 度量的 振荡频率和 精度,及以抖动或 相位噪声度量的信号质量。 图中显示了简化的 晶体输入电路。 晶体连接在 逆变器的输入和输出之间, 其中,R sub S 是一个串联电阻, 用于在需要时降低驱动电平。 芯片内部的 有源电路 会产生一个 正反馈回路 该回路也称为 负电阻,用来提供刺激, 使晶体开始 并维持振荡。 由于晶体的 高机械共振 (q), 仅允许特定的 频率振荡, 这取决于晶体的切割。 通常,这将在小于 100MHz 的频率范围内, 最常见的基本共振 小于 40MHz 左右。 负载电容 CL1 和 CL2 用于控制晶体的 初始频率精度。 输出类型可以是 单端或差分。 参考振荡器的 不同风格可以推断出 精度和稳定性。 TCXO 经过温度补偿, 在工作温度范围内 具有低 PPM。 OCXO 包括用于 保持温度的烤箱 或加热器,并在 整个温度范围内 具有更低的 PPM。 我们还可以添加 电压控制 来调整 VCXO 或 VCTCXO 中的 负载、电容和频率。 压控振荡器 在某些方面 类似于 VCXO。 但 VCO 通常 具有更高的频率和 更宽的调谐范围。 参考振荡器 和 VCO 都是 锁相环的组件。 并且它们各自产生的噪声 相加形成整体 PLL 噪声。 几乎所有 电子系统中都有 实时时钟 (RTC)。 大家可以 将它想象为 上一张幻灯片中 晶体振荡器的 低功耗实现。 诀窍是在不影响 太多频率精度的 情况下尽可能减少电流。 RTC 通常以 32KHz 运行, 功耗在微安范围内, 但 PPM 精度可能较低, 以每天的秒数度量。 许多应用中 都使用了计时器, 但最常用于 电池供电的电路, 尤其是备用电池 需要延长使用寿命时。 没有人希望 电池意外地没电。 对于计时器,可以向 内部振荡器添加一些逻辑, 并且计数器 将以毫秒或分钟进行倒计时。 一旦计数器为空 且计时器到期, 将提供唤醒信号。 此技术允许 关闭整个系统, 并在几分钟或几小时后 唤醒控制器 以执行管理任务 或开始正常运行。 睡眠电流可以 大幅降低至 纳安范围。 睡眠时间 在看门狗计时器中非常重要, 因为它也会影响 整个系统的 电流消耗。 如果系统具有处理器、 高速 I/O、 通信或物理层 连接, 则将需要多个 时钟频率 来支持这些 处理和通信 网络。 还有一些 IC 时钟解决方案 具有更高的 集成度, 可以以更低的 制造材料成本和 更高的可靠性 提供类似的功能。 当需要 单个频率的 多个副本时 (例如 25MHz 需要四次), 或者可能需要 8 个 时钟频率为 100MHz 的信号, 那么 时钟缓冲器可能比 多个 XO 更适合。 时钟缓冲器 (也称为扇出) 接收输入,并将 输入频率的副本 扇出到多个输出。 时钟缓冲器通常 可以有 1-n 个输出, 其中,n 为 2, 最多可以达到 1-12,甚至 1-20。 在简单的扇出 缓冲器中,通常需要的是 抖动极低或 解决方案成本低, 以及较低的输出到输出偏斜。 与晶体 振荡器相似, 有差分和 单端输出类型, 以及可以提供灵活性 和性能的 其他选项。 在通用缓冲器中, 与差分形式一样, 希望获得更高的性能。 而且, 除了附加抖动中的偏斜之外, 传播延迟和 可能的延迟变化等规范 可能也很重要。 还需要一种 配置功能的方法, 例如 I2C、 窥探或引脚控制, 以选择所需的 输入/输出类型 和 I/O 电压电平, 以适应系统 需求。 支持的典型格式 包括 LVCMOS、LVDS 和 LVPECL、HCSL 等。 现在,通常情况下, 系统需要 比简单的扇出缓冲器更多的资源 来支持多个频率。 例如, 如果需要 25MHz、 100MHz 和 156.25MHz, 该怎么办? 时钟发生器是 一种特殊的电路, 可通过 一个或多个锁相环 从单个参考输入 产生多个频率输出。 时钟发生器采用 激励或参考输入, 可以是晶体、 振荡器或 时钟树上一级的 时钟输出,并从中产生 多个频率 或所需 相同频率的 多个副本。 锁相环 (PLL) 是一种反馈系统, 在此系统中,VCO 跟踪 参考输入的 相位和频率。 因此, VCO 输出频率 是相位检测器频率 乘以时间。 有关 PLL 和 VCO 构建块的更多详细信息, 请访问高精度实验室 锁相环基础知识 培训系列。 时钟发生器中的 每个输出分频器 D 可以选择一个 PLL, 对其进行分频并产生 输出频率。 有时,多个输出 组合在一起 并共享一个公共的 输出分频器。 在这种情况下,这些 输出将始终 具有相同的时钟频率。 为什么需要时钟发生器? 当系统用例 (例如网络和工厂 自动化,也可能是 医学成像) 需要不同的 时钟频率时, 与使用 多个振荡器 和/或晶体相比, 时钟发生器更合适。 为便于 以后讨论, 我们将输出缓冲器分频器 称为 时钟分配块。 以不同的方式 查看时钟操作, 可分为三种主要的 模拟时钟架构。 这里显示的是简化框图, 显示了 时钟分配网络中的参考。 时钟分配 或时钟缓冲器 不过滤任何噪声。 它只能增加抖动。 但这是简单且低功耗的。 时钟发生器中 常见的单环路 在同一步骤中 同时进行抖动消除 和倍频。 由于 PLL VCO 工作, 单环路 的确为 大于 10KHz 的更高频率噪声 提供了参考 滤波。 但是,双环路 或级联环路 将在更接近载波的 频率偏移处 更好地清除抖动, 因为它将在 第一个抖动清除 PLL 中 使用 VCXO 晶体振荡器。 第一个 PLL (PLL1) 应该 具有较窄的环路带宽, 以滤除 参考噪声。 第二个 PLL (PLL2) 应该 具有较宽的环路带宽, 以利用 清除抖动后的参考噪声。 第二个 PLL 执行更多的 倍频功能, 以允许 分配块分频为 所需的 输出频率。 例如, 如果想使用恢复的[听不清]时钟 作为输入参考时钟, 或者需要 在载波附近 产生低相位噪声, 则在参考输入 噪声较大的情况下, 将使用双级联 环路架构, 因为典型的 VCO 在 10KHz 以下的 近端相位噪声性能 较差。 当输入和输出 频率的整数关系 不佳时,可能还需要 使用抖动清除器。 例如,如果 参考频率为 12.288MHz, 而 VCO 的参考频率 为 2.5GHz, 则将导致非常低的 32KHz 相位检测器 频率。 较高的相位检测器 比较频率 通常会改善 PLL 性能。 双环路可以为 第二个 PLL 提供 10MHz 或 100MHz 的参考输入, 这是比较频率的 300 或 3,000 倍。 需要同步 多个频率源, 以在输入和 多个频率输出之间 提供确定的相位关系。 通常,抖动清除器 将在分配路径中 包括 延迟补偿网络, 以帮助 平衡输出之间的 任何路由差异。 实际上, 对于 时间紧迫的应用, 同步变得越来越重要。 为了实现此功能, 网络同步器 是关键组件, 通常用于 满足一些 更具挑战性的 ITU 和 电信标准。 许多 ITU、电信 和 4G、5G 标准 都要求 始终保证 时间和频率同步。 网络同步器 始终提供 高度稳定的时钟, 而不管是否存在 参考输入。 基于合格性和优先级, 以无中断的方式 监视和切换 冗余输入, 并且相位干扰非常低。 数字锁相环 (DPLL) 可在 参考丢失时 提供保持功能, 并可进行编程 以使环路带宽 小于 1Hz。 想象一下, 要在模拟域中 达到低于 1Hz 的带宽, 需要一个电容器。 频率输出 跟踪参考近端的 稳定性。 DPLL 带宽 决定了长期漂移方面和 相位瞬变。 XO 和 APLL 决定了 短期时钟方面、 相位噪声和杂散。 混合信号技术 用于获得出色性能。 但是,片上 LCVCO 通常会带来一些限制。 一种 将体声波 (BAW) 振荡器 集成到 网络同步器的新架构 采用了 DPLL 和 APLL 的主要优势, 并将它们 组合在一起, 从而降低了带内噪声。 通常,只有 低频 XO 足以实现小于 100 飞秒的抖动。 本培训视频 到此结束。 谢谢观看。 我们设置了一个包含 五个问题的简单测验, 请完成该测验,检验您对 视频内容的理解程度。 如果您需要有关 TI 时钟和计时产品的 更多信息,请访问 ti.com/clocks。 我们来核对一下答案。 第一个问题的答案是“错误”。 时钟发生器、 抖动清除器 或网络同步器可以 从单个参考 提供多个频域。 第二个问题的答案是“正确”。 所有这些功能 都可以包含在 时钟分配块中, 并且始终至少 存在一个输出缓冲器。 第三个问题的答案是“错误”。 由于时钟缓冲器 复制了输入, 因此不会引入 频率误差。 偏斜用于衡量输出 之间的相位差。 第四个问题的答案是“正确”。 PLL1 的环路带宽较窄, 可滤除参考源的噪声。 PLL2 执行倍频, 允许分配块 分频为所需的 输出频率。 最后一个问题的 答案也是“错误”。 无论是在参考 之间切换还是 进入没有参考的 保持模式,网络同步器 都可以保持 时间和频率精度。 因此,对于参考是否稳定 或是否进出基本不受影响。 the reference is stable or goes in and out.

大家好,欢迎观看 TI 高精度实验室。 当大家听到时钟和 计时系统这两个术语时, 会想到什么呢? 实际上这涉及很多东西。 但是,如何知道 哪个时钟最合适呢? 本入门培训模块概述了 不同时钟和计时功能的 应用。 红色显示的 锁相环和 VCO 功能 是各种时钟 解决方案中使用的核心 构建块。 这些 PLL 和 VCO 功能 以及关键性能参数 在其他高精度 实验室培训模块中 进行了讨论。 什么是时钟? 时钟在电子系统中 提供脉冲。 在信号链中,时钟 是关键构建块, 可为 ADC、DAC、 处理器和任何接口媒体 提供参考采样计时。 任何需要 参考时间进行 同步、执行命令 和传输数据的系统 都需要时钟。 它们向各种设备 提供频率输入, 使它们能够 执行预期的功能。 时钟也可以 用作功能块, 该功能块将信号源 进行倍频和分频, 从而扇出特定频率, 甚至几个不同的频率。 如果系统中 需要处理器、 高速接口或 数据转换器, 则需要时钟解决方案。 我们先来介绍 最常用的功能 - 晶体 振荡器。 关键参数 是以 PPM 度量的 振荡频率和 精度,及以抖动或 相位噪声度量的信号质量。 图中显示了简化的 晶体输入电路。 晶体连接在 逆变器的输入和输出之间, 其中,R sub S 是一个串联电阻, 用于在需要时降低驱动电平。 芯片内部的 有源电路 会产生一个 正反馈回路 该回路也称为 负电阻,用来提供刺激, 使晶体开始 并维持振荡。 由于晶体的 高机械共振 (q), 仅允许特定的 频率振荡, 这取决于晶体的切割。 通常,这将在小于 100MHz 的频率范围内, 最常见的基本共振 小于 40MHz 左右。 负载电容 CL1 和 CL2 用于控制晶体的 初始频率精度。 输出类型可以是 单端或差分。 参考振荡器的 不同风格可以推断出 精度和稳定性。 TCXO 经过温度补偿, 在工作温度范围内 具有低 PPM。 OCXO 包括用于 保持温度的烤箱 或加热器,并在 整个温度范围内 具有更低的 PPM。 我们还可以添加 电压控制 来调整 VCXO 或 VCTCXO 中的 负载、电容和频率。 压控振荡器 在某些方面 类似于 VCXO。 但 VCO 通常 具有更高的频率和 更宽的调谐范围。 参考振荡器 和 VCO 都是 锁相环的组件。 并且它们各自产生的噪声 相加形成整体 PLL 噪声。 几乎所有 电子系统中都有 实时时钟 (RTC)。 大家可以 将它想象为 上一张幻灯片中 晶体振荡器的 低功耗实现。 诀窍是在不影响 太多频率精度的 情况下尽可能减少电流。 RTC 通常以 32KHz 运行, 功耗在微安范围内, 但 PPM 精度可能较低, 以每天的秒数度量。 许多应用中 都使用了计时器, 但最常用于 电池供电的电路, 尤其是备用电池 需要延长使用寿命时。 没有人希望 电池意外地没电。 对于计时器,可以向 内部振荡器添加一些逻辑, 并且计数器 将以毫秒或分钟进行倒计时。 一旦计数器为空 且计时器到期, 将提供唤醒信号。 此技术允许 关闭整个系统, 并在几分钟或几小时后 唤醒控制器 以执行管理任务 或开始正常运行。 睡眠电流可以 大幅降低至 纳安范围。 睡眠时间 在看门狗计时器中非常重要, 因为它也会影响 整个系统的 电流消耗。 如果系统具有处理器、 高速 I/O、 通信或物理层 连接, 则将需要多个 时钟频率 来支持这些 处理和通信 网络。 还有一些 IC 时钟解决方案 具有更高的 集成度, 可以以更低的 制造材料成本和 更高的可靠性 提供类似的功能。 当需要 单个频率的 多个副本时 (例如 25MHz 需要四次), 或者可能需要 8 个 时钟频率为 100MHz 的信号, 那么 时钟缓冲器可能比 多个 XO 更适合。 时钟缓冲器 (也称为扇出) 接收输入,并将 输入频率的副本 扇出到多个输出。 时钟缓冲器通常 可以有 1-n 个输出, 其中,n 为 2, 最多可以达到 1-12,甚至 1-20。 在简单的扇出 缓冲器中,通常需要的是 抖动极低或 解决方案成本低, 以及较低的输出到输出偏斜。 与晶体 振荡器相似, 有差分和 单端输出类型, 以及可以提供灵活性 和性能的 其他选项。 在通用缓冲器中, 与差分形式一样, 希望获得更高的性能。 而且, 除了附加抖动中的偏斜之外, 传播延迟和 可能的延迟变化等规范 可能也很重要。 还需要一种 配置功能的方法, 例如 I2C、 窥探或引脚控制, 以选择所需的 输入/输出类型 和 I/O 电压电平, 以适应系统 需求。 支持的典型格式 包括 LVCMOS、LVDS 和 LVPECL、HCSL 等。 现在,通常情况下, 系统需要 比简单的扇出缓冲器更多的资源 来支持多个频率。 例如, 如果需要 25MHz、 100MHz 和 156.25MHz, 该怎么办? 时钟发生器是 一种特殊的电路, 可通过 一个或多个锁相环 从单个参考输入 产生多个频率输出。 时钟发生器采用 激励或参考输入, 可以是晶体、 振荡器或 时钟树上一级的 时钟输出,并从中产生 多个频率 或所需 相同频率的 多个副本。 锁相环 (PLL) 是一种反馈系统, 在此系统中,VCO 跟踪 参考输入的 相位和频率。 因此, VCO 输出频率 是相位检测器频率 乘以时间。 有关 PLL 和 VCO 构建块的更多详细信息, 请访问高精度实验室 锁相环基础知识 培训系列。 时钟发生器中的 每个输出分频器 D 可以选择一个 PLL, 对其进行分频并产生 输出频率。 有时,多个输出 组合在一起 并共享一个公共的 输出分频器。 在这种情况下,这些 输出将始终 具有相同的时钟频率。 为什么需要时钟发生器? 当系统用例 (例如网络和工厂 自动化,也可能是 医学成像) 需要不同的 时钟频率时, 与使用 多个振荡器 和/或晶体相比, 时钟发生器更合适。 为便于 以后讨论, 我们将输出缓冲器分频器 称为 时钟分配块。 以不同的方式 查看时钟操作, 可分为三种主要的 模拟时钟架构。 这里显示的是简化框图, 显示了 时钟分配网络中的参考。 时钟分配 或时钟缓冲器 不过滤任何噪声。 它只能增加抖动。 但这是简单且低功耗的。 时钟发生器中 常见的单环路 在同一步骤中 同时进行抖动消除 和倍频。 由于 PLL VCO 工作, 单环路 的确为 大于 10KHz 的更高频率噪声 提供了参考 滤波。 但是,双环路 或级联环路 将在更接近载波的 频率偏移处 更好地清除抖动, 因为它将在 第一个抖动清除 PLL 中 使用 VCXO 晶体振荡器。 第一个 PLL (PLL1) 应该 具有较窄的环路带宽, 以滤除 参考噪声。 第二个 PLL (PLL2) 应该 具有较宽的环路带宽, 以利用 清除抖动后的参考噪声。 第二个 PLL 执行更多的 倍频功能, 以允许 分配块分频为 所需的 输出频率。 例如, 如果想使用恢复的[听不清]时钟 作为输入参考时钟, 或者需要 在载波附近 产生低相位噪声, 则在参考输入 噪声较大的情况下, 将使用双级联 环路架构, 因为典型的 VCO 在 10KHz 以下的 近端相位噪声性能 较差。 当输入和输出 频率的整数关系 不佳时,可能还需要 使用抖动清除器。 例如,如果 参考频率为 12.288MHz, 而 VCO 的参考频率 为 2.5GHz, 则将导致非常低的 32KHz 相位检测器 频率。 较高的相位检测器 比较频率 通常会改善 PLL 性能。 双环路可以为 第二个 PLL 提供 10MHz 或 100MHz 的参考输入, 这是比较频率的 300 或 3,000 倍。 需要同步 多个频率源, 以在输入和 多个频率输出之间 提供确定的相位关系。 通常,抖动清除器 将在分配路径中 包括 延迟补偿网络, 以帮助 平衡输出之间的 任何路由差异。 实际上, 对于 时间紧迫的应用, 同步变得越来越重要。 为了实现此功能, 网络同步器 是关键组件, 通常用于 满足一些 更具挑战性的 ITU 和 电信标准。 许多 ITU、电信 和 4G、5G 标准 都要求 始终保证 时间和频率同步。 网络同步器 始终提供 高度稳定的时钟, 而不管是否存在 参考输入。 基于合格性和优先级, 以无中断的方式 监视和切换 冗余输入, 并且相位干扰非常低。 数字锁相环 (DPLL) 可在 参考丢失时 提供保持功能, 并可进行编程 以使环路带宽 小于 1Hz。 想象一下, 要在模拟域中 达到低于 1Hz 的带宽, 需要一个电容器。 频率输出 跟踪参考近端的 稳定性。 DPLL 带宽 决定了长期漂移方面和 相位瞬变。 XO 和 APLL 决定了 短期时钟方面、 相位噪声和杂散。 混合信号技术 用于获得出色性能。 但是,片上 LCVCO 通常会带来一些限制。 一种 将体声波 (BAW) 振荡器 集成到 网络同步器的新架构 采用了 DPLL 和 APLL 的主要优势, 并将它们 组合在一起, 从而降低了带内噪声。 通常,只有 低频 XO 足以实现小于 100 飞秒的抖动。 本培训视频 到此结束。 谢谢观看。 我们设置了一个包含 五个问题的简单测验, 请完成该测验,检验您对 视频内容的理解程度。 如果您需要有关 TI 时钟和计时产品的 更多信息,请访问 ti.com/clocks。 我们来核对一下答案。 第一个问题的答案是“错误”。 时钟发生器、 抖动清除器 或网络同步器可以 从单个参考 提供多个频域。 第二个问题的答案是“正确”。 所有这些功能 都可以包含在 时钟分配块中, 并且始终至少 存在一个输出缓冲器。 第三个问题的答案是“错误”。 由于时钟缓冲器 复制了输入, 因此不会引入 频率误差。 偏斜用于衡量输出 之间的相位差。 第四个问题的答案是“正确”。 PLL1 的环路带宽较窄, 可滤除参考源的噪声。 PLL2 执行倍频, 允许分配块 分频为所需的 输出频率。 最后一个问题的 答案也是“错误”。 无论是在参考 之间切换还是 进入没有参考的 保持模式,网络同步器 都可以保持 时间和频率精度。 因此,对于参考是否稳定 或是否进出基本不受影响。 the reference is stable or goes in and out.

大家好,欢迎观看 TI 高精度实验室。

当大家听到时钟和 计时系统这两个术语时,

会想到什么呢?

实际上这涉及很多东西。

但是,如何知道 哪个时钟最合适呢?

本入门培训模块概述了

不同时钟和计时功能的

应用。

红色显示的 锁相环和 VCO 功能

是各种时钟 解决方案中使用的核心

构建块。

这些 PLL 和 VCO 功能 以及关键性能参数

在其他高精度 实验室培训模块中

进行了讨论。

什么是时钟?

时钟在电子系统中 提供脉冲。

在信号链中,时钟 是关键构建块,

可为 ADC、DAC、 处理器和任何接口媒体

提供参考采样计时。

任何需要 参考时间进行

同步、执行命令 和传输数据的系统

都需要时钟。

它们向各种设备 提供频率输入,

使它们能够 执行预期的功能。

时钟也可以 用作功能块,

该功能块将信号源 进行倍频和分频,

从而扇出特定频率, 甚至几个不同的频率。

如果系统中 需要处理器、

高速接口或 数据转换器,

则需要时钟解决方案。

我们先来介绍 最常用的功能 - 晶体

振荡器。

关键参数 是以 PPM 度量的

振荡频率和 精度,及以抖动或

相位噪声度量的信号质量。

图中显示了简化的

晶体输入电路。

晶体连接在 逆变器的输入和输出之间,

其中,R sub S 是一个串联电阻,

用于在需要时降低驱动电平。

芯片内部的 有源电路

会产生一个 正反馈回路

该回路也称为 负电阻,用来提供刺激,

使晶体开始 并维持振荡。

由于晶体的 高机械共振 (q),

仅允许特定的 频率振荡,

这取决于晶体的切割。

通常,这将在小于 100MHz 的频率范围内,

最常见的基本共振

小于 40MHz 左右。

负载电容 CL1 和 CL2

用于控制晶体的

初始频率精度。

输出类型可以是 单端或差分。

参考振荡器的 不同风格可以推断出

精度和稳定性。

TCXO 经过温度补偿,

在工作温度范围内 具有低 PPM。

OCXO 包括用于 保持温度的烤箱

或加热器,并在 整个温度范围内

具有更低的 PPM。

我们还可以添加 电压控制

来调整 VCXO 或 VCTCXO 中的

负载、电容和频率。

压控振荡器 在某些方面

类似于 VCXO。

但 VCO 通常 具有更高的频率和

更宽的调谐范围。

参考振荡器 和 VCO 都是

锁相环的组件。

并且它们各自产生的噪声 相加形成整体 PLL 噪声。

几乎所有 电子系统中都有

实时时钟 (RTC)。

大家可以 将它想象为

上一张幻灯片中 晶体振荡器的

低功耗实现。

诀窍是在不影响 太多频率精度的

情况下尽可能减少电流。

RTC 通常以 32KHz 运行,

功耗在微安范围内,

但 PPM 精度可能较低,

以每天的秒数度量。

许多应用中 都使用了计时器,

但最常用于 电池供电的电路,

尤其是备用电池 需要延长使用寿命时。

没有人希望 电池意外地没电。

对于计时器,可以向 内部振荡器添加一些逻辑,

并且计数器 将以毫秒或分钟进行倒计时。

一旦计数器为空 且计时器到期,

将提供唤醒信号。

此技术允许 关闭整个系统,

并在几分钟或几小时后 唤醒控制器

以执行管理任务 或开始正常运行。

睡眠电流可以 大幅降低至

纳安范围。

睡眠时间 在看门狗计时器中非常重要,

因为它也会影响 整个系统的

电流消耗。

如果系统具有处理器、 高速 I/O、

通信或物理层 连接,

则将需要多个 时钟频率

来支持这些 处理和通信

网络。

还有一些 IC 时钟解决方案

具有更高的 集成度,

可以以更低的 制造材料成本和

更高的可靠性 提供类似的功能。

当需要 单个频率的

多个副本时 (例如 25MHz 需要四次),

或者可能需要 8 个 时钟频率为

100MHz 的信号, 那么

时钟缓冲器可能比 多个 XO 更适合。

时钟缓冲器 (也称为扇出)

接收输入,并将 输入频率的副本

扇出到多个输出。

时钟缓冲器通常 可以有 1-n 个输出,

其中,n 为 2, 最多可以达到 1-12,甚至 1-20。

在简单的扇出 缓冲器中,通常需要的是

抖动极低或 解决方案成本低,

以及较低的输出到输出偏斜。

与晶体 振荡器相似,

有差分和 单端输出类型,

以及可以提供灵活性 和性能的

其他选项。

在通用缓冲器中, 与差分形式一样,

希望获得更高的性能。

而且, 除了附加抖动中的偏斜之外,

传播延迟和 可能的延迟变化等规范

可能也很重要。

还需要一种 配置功能的方法,

例如 I2C、 窥探或引脚控制,

以选择所需的 输入/输出类型

和 I/O 电压电平, 以适应系统

需求。

支持的典型格式 包括 LVCMOS、LVDS

和 LVPECL、HCSL 等。

现在,通常情况下, 系统需要

比简单的扇出缓冲器更多的资源 来支持多个频率。

例如, 如果需要 25MHz、

100MHz 和 156.25MHz,

该怎么办?

时钟发生器是 一种特殊的电路,

可通过 一个或多个锁相环

从单个参考输入 产生多个频率输出。

时钟发生器采用 激励或参考输入,

可以是晶体、 振荡器或

时钟树上一级的 时钟输出,并从中产生

多个频率 或所需

相同频率的 多个副本。

锁相环 (PLL) 是一种反馈系统,

在此系统中,VCO 跟踪 参考输入的

相位和频率。

因此, VCO 输出频率

是相位检测器频率 乘以时间。

有关 PLL 和 VCO 构建块的更多详细信息,

请访问高精度实验室 锁相环基础知识

培训系列。

时钟发生器中的 每个输出分频器 D

可以选择一个 PLL, 对其进行分频并产生

输出频率。

有时,多个输出 组合在一起

并共享一个公共的 输出分频器。

在这种情况下,这些 输出将始终

具有相同的时钟频率。

为什么需要时钟发生器?

当系统用例 (例如网络和工厂

自动化,也可能是 医学成像)

需要不同的 时钟频率时,

与使用 多个振荡器

和/或晶体相比, 时钟发生器更合适。

为便于 以后讨论,

我们将输出缓冲器分频器 称为

时钟分配块。

以不同的方式 查看时钟操作,

可分为三种主要的 模拟时钟架构。

这里显示的是简化框图, 显示了

时钟分配网络中的参考。

时钟分配 或时钟缓冲器

不过滤任何噪声。

它只能增加抖动。

但这是简单且低功耗的。

时钟发生器中 常见的单环路

在同一步骤中 同时进行抖动消除

和倍频。

由于 PLL VCO 工作, 单环路

的确为 大于 10KHz

的更高频率噪声 提供了参考

滤波。

但是,双环路 或级联环路

将在更接近载波的 频率偏移处

更好地清除抖动, 因为它将在

第一个抖动清除 PLL 中 使用 VCXO 晶体振荡器。

第一个 PLL (PLL1) 应该 具有较窄的环路带宽,

以滤除 参考噪声。

第二个 PLL (PLL2) 应该 具有较宽的环路带宽,

以利用 清除抖动后的参考噪声。

第二个 PLL 执行更多的 倍频功能,

以允许 分配块分频为

所需的 输出频率。

例如, 如果想使用恢复的[听不清]时钟

作为输入参考时钟, 或者需要

在载波附近 产生低相位噪声,

则在参考输入 噪声较大的情况下,

将使用双级联 环路架构,

因为典型的 VCO 在 10KHz 以下的

近端相位噪声性能 较差。

当输入和输出 频率的整数关系

不佳时,可能还需要 使用抖动清除器。

例如,如果 参考频率为 12.288MHz,

而 VCO 的参考频率 为 2.5GHz,

则将导致非常低的 32KHz 相位检测器

频率。

较高的相位检测器 比较频率

通常会改善 PLL 性能。

双环路可以为 第二个 PLL 提供

10MHz 或 100MHz 的参考输入,

这是比较频率的 300 或

3,000 倍。

需要同步 多个频率源,

以在输入和 多个频率输出之间

提供确定的相位关系。

通常,抖动清除器 将在分配路径中

包括 延迟补偿网络,

以帮助 平衡输出之间的

任何路由差异。

实际上, 对于

时间紧迫的应用, 同步变得越来越重要。

为了实现此功能, 网络同步器

是关键组件, 通常用于

满足一些 更具挑战性的 ITU 和

电信标准。

许多 ITU、电信 和 4G、5G 标准

都要求 始终保证

时间和频率同步。

网络同步器 始终提供

高度稳定的时钟, 而不管是否存在

参考输入。

基于合格性和优先级, 以无中断的方式

监视和切换 冗余输入,

并且相位干扰非常低。

数字锁相环 (DPLL) 可在

参考丢失时 提供保持功能,

并可进行编程 以使环路带宽

小于 1Hz。

想象一下, 要在模拟域中

达到低于 1Hz 的带宽, 需要一个电容器。

频率输出 跟踪参考近端的

稳定性。

DPLL 带宽 决定了长期漂移方面和

相位瞬变。

XO 和 APLL 决定了 短期时钟方面、

相位噪声和杂散。

混合信号技术 用于获得出色性能。

但是,片上 LCVCO 通常会带来一些限制。

一种 将体声波 (BAW) 振荡器

集成到 网络同步器的新架构

采用了 DPLL 和 APLL 的主要优势,

并将它们 组合在一起,

从而降低了带内噪声。

通常,只有 低频 XO

足以实现小于 100 飞秒的抖动。

本培训视频 到此结束。

谢谢观看。

我们设置了一个包含 五个问题的简单测验,

请完成该测验,检验您对 视频内容的理解程度。

如果您需要有关 TI 时钟和计时产品的

更多信息,请访问

ti.com/clocks。

我们来核对一下答案。

第一个问题的答案是“错误”。

时钟发生器、 抖动清除器

或网络同步器可以 从单个参考

提供多个频域。

第二个问题的答案是“正确”。

所有这些功能 都可以包含在

时钟分配块中, 并且始终至少

存在一个输出缓冲器。

第三个问题的答案是“错误”。

由于时钟缓冲器 复制了输入,

因此不会引入 频率误差。

偏斜用于衡量输出 之间的相位差。

第四个问题的答案是“正确”。

PLL1 的环路带宽较窄,

可滤除参考源的噪声。

PLL2 执行倍频,

允许分配块 分频为所需的

输出频率。

最后一个问题的 答案也是“错误”。

无论是在参考 之间切换还是

进入没有参考的 保持模式,网络同步器

都可以保持 时间和频率精度。

因此,对于参考是否稳定 或是否进出基本不受影响。

the reference is stable or goes in and out.

大家好,欢迎观看 TI 高精度实验室。 当大家听到时钟和 计时系统这两个术语时, 会想到什么呢? 实际上这涉及很多东西。 但是,如何知道 哪个时钟最合适呢? 本入门培训模块概述了 不同时钟和计时功能的 应用。 红色显示的 锁相环和 VCO 功能 是各种时钟 解决方案中使用的核心 构建块。 这些 PLL 和 VCO 功能 以及关键性能参数 在其他高精度 实验室培训模块中 进行了讨论。 什么是时钟? 时钟在电子系统中 提供脉冲。 在信号链中,时钟 是关键构建块, 可为 ADC、DAC、 处理器和任何接口媒体 提供参考采样计时。 任何需要 参考时间进行 同步、执行命令 和传输数据的系统 都需要时钟。 它们向各种设备 提供频率输入, 使它们能够 执行预期的功能。 时钟也可以 用作功能块, 该功能块将信号源 进行倍频和分频, 从而扇出特定频率, 甚至几个不同的频率。 如果系统中 需要处理器、 高速接口或 数据转换器, 则需要时钟解决方案。 我们先来介绍 最常用的功能 - 晶体 振荡器。 关键参数 是以 PPM 度量的 振荡频率和 精度,及以抖动或 相位噪声度量的信号质量。 图中显示了简化的 晶体输入电路。 晶体连接在 逆变器的输入和输出之间, 其中,R sub S 是一个串联电阻, 用于在需要时降低驱动电平。 芯片内部的 有源电路 会产生一个 正反馈回路 该回路也称为 负电阻,用来提供刺激, 使晶体开始 并维持振荡。 由于晶体的 高机械共振 (q), 仅允许特定的 频率振荡, 这取决于晶体的切割。 通常,这将在小于 100MHz 的频率范围内, 最常见的基本共振 小于 40MHz 左右。 负载电容 CL1 和 CL2 用于控制晶体的 初始频率精度。 输出类型可以是 单端或差分。 参考振荡器的 不同风格可以推断出 精度和稳定性。 TCXO 经过温度补偿, 在工作温度范围内 具有低 PPM。 OCXO 包括用于 保持温度的烤箱 或加热器,并在 整个温度范围内 具有更低的 PPM。 我们还可以添加 电压控制 来调整 VCXO 或 VCTCXO 中的 负载、电容和频率。 压控振荡器 在某些方面 类似于 VCXO。 但 VCO 通常 具有更高的频率和 更宽的调谐范围。 参考振荡器 和 VCO 都是 锁相环的组件。 并且它们各自产生的噪声 相加形成整体 PLL 噪声。 几乎所有 电子系统中都有 实时时钟 (RTC)。 大家可以 将它想象为 上一张幻灯片中 晶体振荡器的 低功耗实现。 诀窍是在不影响 太多频率精度的 情况下尽可能减少电流。 RTC 通常以 32KHz 运行, 功耗在微安范围内, 但 PPM 精度可能较低, 以每天的秒数度量。 许多应用中 都使用了计时器, 但最常用于 电池供电的电路, 尤其是备用电池 需要延长使用寿命时。 没有人希望 电池意外地没电。 对于计时器,可以向 内部振荡器添加一些逻辑, 并且计数器 将以毫秒或分钟进行倒计时。 一旦计数器为空 且计时器到期, 将提供唤醒信号。 此技术允许 关闭整个系统, 并在几分钟或几小时后 唤醒控制器 以执行管理任务 或开始正常运行。 睡眠电流可以 大幅降低至 纳安范围。 睡眠时间 在看门狗计时器中非常重要, 因为它也会影响 整个系统的 电流消耗。 如果系统具有处理器、 高速 I/O、 通信或物理层 连接, 则将需要多个 时钟频率 来支持这些 处理和通信 网络。 还有一些 IC 时钟解决方案 具有更高的 集成度, 可以以更低的 制造材料成本和 更高的可靠性 提供类似的功能。 当需要 单个频率的 多个副本时 (例如 25MHz 需要四次), 或者可能需要 8 个 时钟频率为 100MHz 的信号, 那么 时钟缓冲器可能比 多个 XO 更适合。 时钟缓冲器 (也称为扇出) 接收输入,并将 输入频率的副本 扇出到多个输出。 时钟缓冲器通常 可以有 1-n 个输出, 其中,n 为 2, 最多可以达到 1-12,甚至 1-20。 在简单的扇出 缓冲器中,通常需要的是 抖动极低或 解决方案成本低, 以及较低的输出到输出偏斜。 与晶体 振荡器相似, 有差分和 单端输出类型, 以及可以提供灵活性 和性能的 其他选项。 在通用缓冲器中, 与差分形式一样, 希望获得更高的性能。 而且, 除了附加抖动中的偏斜之外, 传播延迟和 可能的延迟变化等规范 可能也很重要。 还需要一种 配置功能的方法, 例如 I2C、 窥探或引脚控制, 以选择所需的 输入/输出类型 和 I/O 电压电平, 以适应系统 需求。 支持的典型格式 包括 LVCMOS、LVDS 和 LVPECL、HCSL 等。 现在,通常情况下, 系统需要 比简单的扇出缓冲器更多的资源 来支持多个频率。 例如, 如果需要 25MHz、 100MHz 和 156.25MHz, 该怎么办? 时钟发生器是 一种特殊的电路, 可通过 一个或多个锁相环 从单个参考输入 产生多个频率输出。 时钟发生器采用 激励或参考输入, 可以是晶体、 振荡器或 时钟树上一级的 时钟输出,并从中产生 多个频率 或所需 相同频率的 多个副本。 锁相环 (PLL) 是一种反馈系统, 在此系统中,VCO 跟踪 参考输入的 相位和频率。 因此, VCO 输出频率 是相位检测器频率 乘以时间。 有关 PLL 和 VCO 构建块的更多详细信息, 请访问高精度实验室 锁相环基础知识 培训系列。 时钟发生器中的 每个输出分频器 D 可以选择一个 PLL, 对其进行分频并产生 输出频率。 有时,多个输出 组合在一起 并共享一个公共的 输出分频器。 在这种情况下,这些 输出将始终 具有相同的时钟频率。 为什么需要时钟发生器? 当系统用例 (例如网络和工厂 自动化,也可能是 医学成像) 需要不同的 时钟频率时, 与使用 多个振荡器 和/或晶体相比, 时钟发生器更合适。 为便于 以后讨论, 我们将输出缓冲器分频器 称为 时钟分配块。 以不同的方式 查看时钟操作, 可分为三种主要的 模拟时钟架构。 这里显示的是简化框图, 显示了 时钟分配网络中的参考。 时钟分配 或时钟缓冲器 不过滤任何噪声。 它只能增加抖动。 但这是简单且低功耗的。 时钟发生器中 常见的单环路 在同一步骤中 同时进行抖动消除 和倍频。 由于 PLL VCO 工作, 单环路 的确为 大于 10KHz 的更高频率噪声 提供了参考 滤波。 但是,双环路 或级联环路 将在更接近载波的 频率偏移处 更好地清除抖动, 因为它将在 第一个抖动清除 PLL 中 使用 VCXO 晶体振荡器。 第一个 PLL (PLL1) 应该 具有较窄的环路带宽, 以滤除 参考噪声。 第二个 PLL (PLL2) 应该 具有较宽的环路带宽, 以利用 清除抖动后的参考噪声。 第二个 PLL 执行更多的 倍频功能, 以允许 分配块分频为 所需的 输出频率。 例如, 如果想使用恢复的[听不清]时钟 作为输入参考时钟, 或者需要 在载波附近 产生低相位噪声, 则在参考输入 噪声较大的情况下, 将使用双级联 环路架构, 因为典型的 VCO 在 10KHz 以下的 近端相位噪声性能 较差。 当输入和输出 频率的整数关系 不佳时,可能还需要 使用抖动清除器。 例如,如果 参考频率为 12.288MHz, 而 VCO 的参考频率 为 2.5GHz, 则将导致非常低的 32KHz 相位检测器 频率。 较高的相位检测器 比较频率 通常会改善 PLL 性能。 双环路可以为 第二个 PLL 提供 10MHz 或 100MHz 的参考输入, 这是比较频率的 300 或 3,000 倍。 需要同步 多个频率源, 以在输入和 多个频率输出之间 提供确定的相位关系。 通常,抖动清除器 将在分配路径中 包括 延迟补偿网络, 以帮助 平衡输出之间的 任何路由差异。 实际上, 对于 时间紧迫的应用, 同步变得越来越重要。 为了实现此功能, 网络同步器 是关键组件, 通常用于 满足一些 更具挑战性的 ITU 和 电信标准。 许多 ITU、电信 和 4G、5G 标准 都要求 始终保证 时间和频率同步。 网络同步器 始终提供 高度稳定的时钟, 而不管是否存在 参考输入。 基于合格性和优先级, 以无中断的方式 监视和切换 冗余输入, 并且相位干扰非常低。 数字锁相环 (DPLL) 可在 参考丢失时 提供保持功能, 并可进行编程 以使环路带宽 小于 1Hz。 想象一下, 要在模拟域中 达到低于 1Hz 的带宽, 需要一个电容器。 频率输出 跟踪参考近端的 稳定性。 DPLL 带宽 决定了长期漂移方面和 相位瞬变。 XO 和 APLL 决定了 短期时钟方面、 相位噪声和杂散。 混合信号技术 用于获得出色性能。 但是,片上 LCVCO 通常会带来一些限制。 一种 将体声波 (BAW) 振荡器 集成到 网络同步器的新架构 采用了 DPLL 和 APLL 的主要优势, 并将它们 组合在一起, 从而降低了带内噪声。 通常,只有 低频 XO 足以实现小于 100 飞秒的抖动。 本培训视频 到此结束。 谢谢观看。 我们设置了一个包含 五个问题的简单测验, 请完成该测验,检验您对 视频内容的理解程度。 如果您需要有关 TI 时钟和计时产品的 更多信息,请访问 ti.com/clocks。 我们来核对一下答案。 第一个问题的答案是“错误”。 时钟发生器、 抖动清除器 或网络同步器可以 从单个参考 提供多个频域。 第二个问题的答案是“正确”。 所有这些功能 都可以包含在 时钟分配块中, 并且始终至少 存在一个输出缓冲器。 第三个问题的答案是“错误”。 由于时钟缓冲器 复制了输入, 因此不会引入 频率误差。 偏斜用于衡量输出 之间的相位差。 第四个问题的答案是“正确”。 PLL1 的环路带宽较窄, 可滤除参考源的噪声。 PLL2 执行倍频, 允许分配块 分频为所需的 输出频率。 最后一个问题的 答案也是“错误”。 无论是在参考 之间切换还是 进入没有参考的 保持模式,网络同步器 都可以保持 时间和频率精度。 因此,对于参考是否稳定 或是否进出基本不受影响。 the reference is stable or goes in and out.

大家好,欢迎观看 TI 高精度实验室。

当大家听到时钟和 计时系统这两个术语时,

会想到什么呢?

实际上这涉及很多东西。

但是,如何知道 哪个时钟最合适呢?

本入门培训模块概述了

不同时钟和计时功能的

应用。

红色显示的 锁相环和 VCO 功能

是各种时钟 解决方案中使用的核心

构建块。

这些 PLL 和 VCO 功能 以及关键性能参数

在其他高精度 实验室培训模块中

进行了讨论。

什么是时钟?

时钟在电子系统中 提供脉冲。

在信号链中,时钟 是关键构建块,

可为 ADC、DAC、 处理器和任何接口媒体

提供参考采样计时。

任何需要 参考时间进行

同步、执行命令 和传输数据的系统

都需要时钟。

它们向各种设备 提供频率输入,

使它们能够 执行预期的功能。

时钟也可以 用作功能块,

该功能块将信号源 进行倍频和分频,

从而扇出特定频率, 甚至几个不同的频率。

如果系统中 需要处理器、

高速接口或 数据转换器,

则需要时钟解决方案。

我们先来介绍 最常用的功能 - 晶体

振荡器。

关键参数 是以 PPM 度量的

振荡频率和 精度,及以抖动或

相位噪声度量的信号质量。

图中显示了简化的

晶体输入电路。

晶体连接在 逆变器的输入和输出之间,

其中,R sub S 是一个串联电阻,

用于在需要时降低驱动电平。

芯片内部的 有源电路

会产生一个 正反馈回路

该回路也称为 负电阻,用来提供刺激,

使晶体开始 并维持振荡。

由于晶体的 高机械共振 (q),

仅允许特定的 频率振荡,

这取决于晶体的切割。

通常,这将在小于 100MHz 的频率范围内,

最常见的基本共振

小于 40MHz 左右。

负载电容 CL1 和 CL2

用于控制晶体的

初始频率精度。

输出类型可以是 单端或差分。

参考振荡器的 不同风格可以推断出

精度和稳定性。

TCXO 经过温度补偿,

在工作温度范围内 具有低 PPM。

OCXO 包括用于 保持温度的烤箱

或加热器,并在 整个温度范围内

具有更低的 PPM。

我们还可以添加 电压控制

来调整 VCXO 或 VCTCXO 中的

负载、电容和频率。

压控振荡器 在某些方面

类似于 VCXO。

但 VCO 通常 具有更高的频率和

更宽的调谐范围。

参考振荡器 和 VCO 都是

锁相环的组件。

并且它们各自产生的噪声 相加形成整体 PLL 噪声。

几乎所有 电子系统中都有

实时时钟 (RTC)。

大家可以 将它想象为

上一张幻灯片中 晶体振荡器的

低功耗实现。

诀窍是在不影响 太多频率精度的

情况下尽可能减少电流。

RTC 通常以 32KHz 运行,

功耗在微安范围内,

但 PPM 精度可能较低,

以每天的秒数度量。

许多应用中 都使用了计时器,

但最常用于 电池供电的电路,

尤其是备用电池 需要延长使用寿命时。

没有人希望 电池意外地没电。

对于计时器,可以向 内部振荡器添加一些逻辑,

并且计数器 将以毫秒或分钟进行倒计时。

一旦计数器为空 且计时器到期,

将提供唤醒信号。

此技术允许 关闭整个系统,

并在几分钟或几小时后 唤醒控制器

以执行管理任务 或开始正常运行。

睡眠电流可以 大幅降低至

纳安范围。

睡眠时间 在看门狗计时器中非常重要,

因为它也会影响 整个系统的

电流消耗。

如果系统具有处理器、 高速 I/O、

通信或物理层 连接,

则将需要多个 时钟频率

来支持这些 处理和通信

网络。

还有一些 IC 时钟解决方案

具有更高的 集成度,

可以以更低的 制造材料成本和

更高的可靠性 提供类似的功能。

当需要 单个频率的

多个副本时 (例如 25MHz 需要四次),

或者可能需要 8 个 时钟频率为

100MHz 的信号, 那么

时钟缓冲器可能比 多个 XO 更适合。

时钟缓冲器 (也称为扇出)

接收输入,并将 输入频率的副本

扇出到多个输出。

时钟缓冲器通常 可以有 1-n 个输出,

其中,n 为 2, 最多可以达到 1-12,甚至 1-20。

在简单的扇出 缓冲器中,通常需要的是

抖动极低或 解决方案成本低,

以及较低的输出到输出偏斜。

与晶体 振荡器相似,

有差分和 单端输出类型,

以及可以提供灵活性 和性能的

其他选项。

在通用缓冲器中, 与差分形式一样,

希望获得更高的性能。

而且, 除了附加抖动中的偏斜之外,

传播延迟和 可能的延迟变化等规范

可能也很重要。

还需要一种 配置功能的方法,

例如 I2C、 窥探或引脚控制,

以选择所需的 输入/输出类型

和 I/O 电压电平, 以适应系统

需求。

支持的典型格式 包括 LVCMOS、LVDS

和 LVPECL、HCSL 等。

现在,通常情况下, 系统需要

比简单的扇出缓冲器更多的资源 来支持多个频率。

例如, 如果需要 25MHz、

100MHz 和 156.25MHz,

该怎么办?

时钟发生器是 一种特殊的电路,

可通过 一个或多个锁相环

从单个参考输入 产生多个频率输出。

时钟发生器采用 激励或参考输入,

可以是晶体、 振荡器或

时钟树上一级的 时钟输出,并从中产生

多个频率 或所需

相同频率的 多个副本。

锁相环 (PLL) 是一种反馈系统,

在此系统中,VCO 跟踪 参考输入的

相位和频率。

因此, VCO 输出频率

是相位检测器频率 乘以时间。

有关 PLL 和 VCO 构建块的更多详细信息,

请访问高精度实验室 锁相环基础知识

培训系列。

时钟发生器中的 每个输出分频器 D

可以选择一个 PLL, 对其进行分频并产生

输出频率。

有时,多个输出 组合在一起

并共享一个公共的 输出分频器。

在这种情况下,这些 输出将始终

具有相同的时钟频率。

为什么需要时钟发生器?

当系统用例 (例如网络和工厂

自动化,也可能是 医学成像)

需要不同的 时钟频率时,

与使用 多个振荡器

和/或晶体相比, 时钟发生器更合适。

为便于 以后讨论,

我们将输出缓冲器分频器 称为

时钟分配块。

以不同的方式 查看时钟操作,

可分为三种主要的 模拟时钟架构。

这里显示的是简化框图, 显示了

时钟分配网络中的参考。

时钟分配 或时钟缓冲器

不过滤任何噪声。

它只能增加抖动。

但这是简单且低功耗的。

时钟发生器中 常见的单环路

在同一步骤中 同时进行抖动消除

和倍频。

由于 PLL VCO 工作, 单环路

的确为 大于 10KHz

的更高频率噪声 提供了参考

滤波。

但是,双环路 或级联环路

将在更接近载波的 频率偏移处

更好地清除抖动, 因为它将在

第一个抖动清除 PLL 中 使用 VCXO 晶体振荡器。

第一个 PLL (PLL1) 应该 具有较窄的环路带宽,

以滤除 参考噪声。

第二个 PLL (PLL2) 应该 具有较宽的环路带宽,

以利用 清除抖动后的参考噪声。

第二个 PLL 执行更多的 倍频功能,

以允许 分配块分频为

所需的 输出频率。

例如, 如果想使用恢复的[听不清]时钟

作为输入参考时钟, 或者需要

在载波附近 产生低相位噪声,

则在参考输入 噪声较大的情况下,

将使用双级联 环路架构,

因为典型的 VCO 在 10KHz 以下的

近端相位噪声性能 较差。

当输入和输出 频率的整数关系

不佳时,可能还需要 使用抖动清除器。

例如,如果 参考频率为 12.288MHz,

而 VCO 的参考频率 为 2.5GHz,

则将导致非常低的 32KHz 相位检测器

频率。

较高的相位检测器 比较频率

通常会改善 PLL 性能。

双环路可以为 第二个 PLL 提供

10MHz 或 100MHz 的参考输入,

这是比较频率的 300 或

3,000 倍。

需要同步 多个频率源,

以在输入和 多个频率输出之间

提供确定的相位关系。

通常,抖动清除器 将在分配路径中

包括 延迟补偿网络,

以帮助 平衡输出之间的

任何路由差异。

实际上, 对于

时间紧迫的应用, 同步变得越来越重要。

为了实现此功能, 网络同步器

是关键组件, 通常用于

满足一些 更具挑战性的 ITU 和

电信标准。

许多 ITU、电信 和 4G、5G 标准

都要求 始终保证

时间和频率同步。

网络同步器 始终提供

高度稳定的时钟, 而不管是否存在

参考输入。

基于合格性和优先级, 以无中断的方式

监视和切换 冗余输入,

并且相位干扰非常低。

数字锁相环 (DPLL) 可在

参考丢失时 提供保持功能,

并可进行编程 以使环路带宽

小于 1Hz。

想象一下, 要在模拟域中

达到低于 1Hz 的带宽, 需要一个电容器。

频率输出 跟踪参考近端的

稳定性。

DPLL 带宽 决定了长期漂移方面和

相位瞬变。

XO 和 APLL 决定了 短期时钟方面、

相位噪声和杂散。

混合信号技术 用于获得出色性能。

但是,片上 LCVCO 通常会带来一些限制。

一种 将体声波 (BAW) 振荡器

集成到 网络同步器的新架构

采用了 DPLL 和 APLL 的主要优势,

并将它们 组合在一起,

从而降低了带内噪声。

通常,只有 低频 XO

足以实现小于 100 飞秒的抖动。

本培训视频 到此结束。

谢谢观看。

我们设置了一个包含 五个问题的简单测验,

请完成该测验,检验您对 视频内容的理解程度。

如果您需要有关 TI 时钟和计时产品的

更多信息,请访问

ti.com/clocks。

我们来核对一下答案。

第一个问题的答案是“错误”。

时钟发生器、 抖动清除器

或网络同步器可以 从单个参考

提供多个频域。

第二个问题的答案是“正确”。

所有这些功能 都可以包含在

时钟分配块中, 并且始终至少

存在一个输出缓冲器。

第三个问题的答案是“错误”。

由于时钟缓冲器 复制了输入,

因此不会引入 频率误差。

偏斜用于衡量输出 之间的相位差。

第四个问题的答案是“正确”。

PLL1 的环路带宽较窄,

可滤除参考源的噪声。

PLL2 执行倍频,

允许分配块 分频为所需的

输出频率。

最后一个问题的 答案也是“错误”。

无论是在参考 之间切换还是

进入没有参考的 保持模式,网络同步器

都可以保持 时间和频率精度。

因此,对于参考是否稳定 或是否进出基本不受影响。

the reference is stable or goes in and out.

手机看

扫码用手机观看

视频简介

视频简介

1.1 TI 高精度实验室-时钟和计时:系统概述

所属课程:TI 高精度实验室-时钟和计时:简介

发布时间:2020.07.28

视频集数:6

本节视频时长:00:12:47

时钟和定时可以覆盖很多系统用例,但是如何知道哪一个时钟IC最合适呢?

这个入门培训模块概述了不同时钟和计时功能的应用程序和系统用例。

未学习 1.1 TI 高精度实验室-时钟和计时:系统概述

未学习 1.1 TI 高精度实验室-时钟和计时:系统概述

未学习 1.2 TI 高精度实验室-时钟和计时:RF锁相环(PLL)和合成器关键参数

未学习 1.2 TI 高精度实验室-时钟和计时:RF锁相环(PLL)和合成器关键参数

未学习 振荡器主要参数和规格

未学习 振荡器主要参数和规格

未学习 时钟缓冲器主要参数和规格

未学习 时钟缓冲器主要参数和规格

未学习 (中文)振荡器主要参数和规格

未学习 (中文)振荡器主要参数和规格

未学习 (中文)时钟缓冲器主要参数和规格

未学习 (中文)时钟缓冲器主要参数和规格