如何以及为什么用负载开关替换分立MOSFET

Loading the player...

将在30s后自动为您播放下一课程

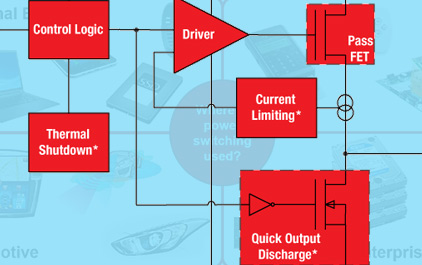

本视频的标题为 电源开关解决方案对比 - 分立式 MOSFET 与 集成负载开关。 本次培训中,您将 学习什么是电源开关 解决方案及如何识别 电路图中的分立式 MOSFET 开关解决方案。 在此过程中,我们将从 直流电与交流电角度 分析分立式开关 解决方案的性能。 然后介绍负载 开关解决方案 并将其性能 与 MOSFET 解决 方案进行比较。 接着,让我们 开始介绍。 电源开关 通常指的是 连接和断开 到负载的电源。 电源开关位于 系统电源 与负载之间, 此开关将控制 何时从电源 对负载供电 或不供电。 工程师在其系统中 使用电源开关的 原因是多方面的。 系统启动期间, 如果电源必须同时 对所有系统 负载供电, 供电压力 会较大。 使用电源开关, 这些负载 则可以一次开启一个, 这样可以毫无问题地 启动电源。 电源开关还可以 被用来降低 电源电压 升高的速度。 这会有助于控制 大负载电容 充电过程中产生的 涌浪电流数量。 电源开关的 另一个原因 是减少电力消耗。 在具有功耗意识的 系统中,如使用 电池供电的应用, 电力消耗 是关键问题所在。 为使系统 更有效率, 可将不需要 供电的负载关闭, 不使用时可以 使用电源开关 断开负载 与电源。 对于处理器和 FPGA 应用程序, 需使用电源轨排序 以便正常运行。 电源开关可被用来 对这些电源轨进行排序 并保证正确 启动系统。 哪些市场和终端设备 使用电源开关? 几乎所有都使用。 在个人电子 产品中, 有许多使用电池 供电的应用, 如笔记本电脑、平板电脑 及穿戴式计算机, 它们均采用电源 开关来禁用 未用的子系统。 这样可以降低 系统的电力消耗 并提高电池寿命。 在工业市场中, 移动销售点机器 使用电源开关以节约 电池寿命,而 COM express 模块 使用电源 开关来调节 哪些电压轨 投入使用 及系统是否 处于待机状态。 汽车使用电源 开关以便对应用 处理器和 信息娱乐系统和仪表组应用 进行电力排序。 电源开关还可 用于打开和关闭 汽车照明灯。 在企业市场中, 服务器需要 电源开关来 控制系统启动。 各服务器拥有多个 必须通电的硬驱动。 若要防止 供电压力, 可使用开关同时 打开少数硬驱动。 这样将允许 电源供应 逐渐安全开启。 实现电源开关的 一种方法就是 使用分立式解决方案。 这些解决方案使用 MOSFET 来接通和切断 对某负载的电源。 许多时候,MOSFET 周围设有几个 分立组件, 以帮助控制开关 或添加额外功能。 若要在电路图中 找到其中一个解决方案, 建议搜索 水平绘制的 FET。 许多时候会为系统中 某电源开关应用采用 这些 MOSFET。 我们将查看的第一个 分立式 MOSFET 解决方案 是 PMOS 解决方案。 使用该解决方案的较大 优势就在于它的简单。 仅需一个组件。 通过连接 PMOS 栅极至 GPIO, GPIO 可以控制 是接通还是切断 PMOS。 但是,这是一种 低电平解决方案, 意味着 GPIO 必须较高 开关才会关闭。 这会是一种弊端, 因为需要先接通 系统电源,然后才会将电源 从 VIN 拦截到 VOUT。 该解决方案中的 另一个弊端是 GPIO 变化。 至于该解决方案的 最佳性能, 当开关打开时, MOSFET 从 VIN 到 VOUT 的导通电阻 或电阻应非常低。 这导致给定负载 电流情况下, VIN 落到 VOUT的 电压最低。 若要最大程度 减少导通电阻, 电源与 PMOS 栅极间的 电压差必须较高。 因此,该解决 方案的最佳性能 是将栅极拉至 0 伏特时。 如果 GPIO 信号 出现变化, 那么数字低输出 会更接近 更接近 200 或 300 毫伏, 导致解决方案 性能不理想。 这也会使该解决 方案很难使用 较低电压。 VIN 不能低于 MOSFET 的 通电阈值。 所以,如果电压 低于该阈值, 它会阻止 系统通电。 对于下列 范围截屏,每个轨迹 均贴有标签 并对右图 进行颜色编码。 从顶部开始,我们 拥有 ON 引脚电压、 VIN 电压、 VOUT 电压 及流过 FET 的电流。 对于本例, VOUT 电容 为 4.7 微法拉。 范围截屏显示 ON 引脚从高走向低。 因此低电平解决方案 从切断改为接通。 VOUT 电压 如预期般升高。 但我们发现,VIN 电压 降低,电流高峰 大约为 2.2 安培。 这是因为 开关接通时, 电压升温速率 失控并在几纳秒内 升高。 这种快速通电 会导致电容 快速充电。 根据方程式 I = C/dt, 这会导致 涌浪电流较大。 在这种情况下, 仅需 4.7 微法拉 即可产生 2 安培 以上涌浪电流。 因此,电源供应 无法处理负载, 必须降低电压进行补偿。 该涌浪电流会导致 意外的系统性能, 如外接口或 PCB 轨迹重置 或损坏。 第二种解决方案增加了 电阻和 NMOS 晶体管。 通过控制 NMOS 晶体管栅极, 本解决方案 变为高电平, 意味着电压高时 可以接通系统, 电压低时可以 切断系统。 而且,NMOS 可以 将 PMOS 栅极 拉至 0 伏特状态, 这样可以优化 该解决方案的 导通电阻性能。 但是,较低 电压仍然 不能用于 该解决方案。 当解决方案接通时, 增加电阻器 会增加其 漏电路径。 电阻越低, 漏电量越高。 电阻越高, 漏电量越低。 从交流电角度来看, 变化不大。 解决方案仍然不能 控制输出电压 升高的速率。 输出电容 再次导致 大涌浪电流。 我们将查看的最后一个 PMOS 解决方案 增加了一个附加电容器, 并对涌浪电流有所帮助。 从直流电角度来看, 没有任何变化。 高电平解决 方案仍然可以 优化导通 电阻性能, 当解决方案 通电时 放电路径仍然存在。 使用此解决方案,电压 斜坡率会得到控制。 通过增加栅极与 VOUT 之间的电容, 电压上升时间 可能会增长, 这会使 涌浪电流降低。 例如,电容为 47 微法拉时, 电压上升 时间大约 为 150 微秒 且涌浪电流 由 2 安培 降至 200 毫安。 电容较高时, 涌浪电流 甚至降低更多。 请记住, 如果通电时间 增加,断电 时间也会增加, 这意味着解决方案 如需要缓慢通电 和快速断电时间 则不能正常运行。 左侧显示的范围 表明本解决方案 通电并连接 3 安培负载, 我们可以看到, 电压和电流 均受控。 虽然此解决方案 能够提供 电压和电流 均适用的线性斜坡, 但是观察到一项异常。 在首次开启 解决方案时, 负电压和 负电流均会出现。 这是开机时 电容的 预充方式造成的。 在此期间, PMOS 的栅极较高, 且 VOUT 为 0 伏。 电容器将 充电至 VIN 值, 如图所示。 当此解决方案开启后, PMOS 栅极变低, 并且电容 会通过 NMOS 放电至接地。 在该解决方案 有时间完全开启前, 此放电将 VOUT 下拉。 虽然较高的电阻能够 有助于降低涌浪电流, 它还会为 该解决方案 产生更多的负电压和电流。 在 47 微法拉条件下, 在 VOUT 观察到负 1 伏。 如果负载输入 无法处理此负电压, 这可导致 负载受损。 当首次 应用 VIN 时, 此解决方案还会出现 另一问题。 在系统中,此情况可以是 插入电池 或初始系统启动。 在此期间, 栅极电压为 0 伏。 当应用 VIN 后,栅极至 VOUT 的电容器 使 PMOS 栅极的 充电时间变长。 虽然栅极 仍然在充电, 但是该解决方案 未完全关闭, 并且可见到功率 从 VIN 流至 VOUT, 即使该解决方案 已关闭,也是如此。 如果在系统启动期间 不要求对负载加电, 则不能使用 该解决方案。 现在,我们研究了 PMOS 解决方案, 接下来我们将讨论 NMOS 解决方案。 从交流电角度来看, 规则没变。 需要添加电容 以降满栅极充电速度, 从而可以控制 输出电压。 如不添加, 则输出电压将失控, 并且将产生大 涌浪电流。 从直流电角度来看, 事情对于 NMOS 略有不同。 栅极需要高于 VIN 才能使解决方案启动。 这意味着该解决方案 能够开关较低的输入电压, 而不会有任何问题。 为获得最佳 导通电阻性能, VIN 和栅极 之间的电压差 应是高电压差。 为此, 栅极电压 必须远高于 VIN。 左侧显示了此问题的 两个解决方案。 第一个解决方案使用 充电泵,取 VIN 的值并 从中生成 较高的电压, 这可与栅极上使用。 第二个解决方案 使用多个分立式组件, 并可在系统中 有较高电压轨时 使用。 虽然两个解决方案 均可使用高栅极电压 以最大程度减少导通电阻, 它们占用许多空间 并使用许多组件 才能达成目标。 现在,让我们看一看, 向这些分立式解决方案 添加附加功能 所需的一些 分立式电路。 快速输出 放电,或者说 QOD, 用于拉低开关 解决方案关闭时的 输出电压。 这将保证 负载的电压 拉低至 0 伏 并且该负载 已完全关闭。 要以分立形式达成此目的, 有两种解决方案。 选项 1 是在 输出端添加 旁漏电阻,这将 在解决方案关闭时 使负载放电。 但是,这也会在 解决方案开启时, 通过该电阻提供 漏电路径。 选项 2 使用 逆变器和晶体管。 该解决方案将仅 通过晶体管 在关闭开关时 在输出端放电。 由于在分立式 开关解决方案中 MOSFET 体二极管具有朝向, 从 VIN 至 VOUT 的 电流被阻断。 但是,如果 VOUT 大于 VIN, 则电流能够从 VOUT 流至 VIN。 要实施反向 电流阻断, 必须额外添加两个晶体管, 且将其体二极管 朝相反方向。 该解决方案将在关闭时 阻断两个方向的电流, 但是将使开关的 导通电阻翻倍, 因为两个 MOSFET 为相互串联。 Power Good(电源正常)功能会在 开关解决方案开启 并且输出电压高时 提供 高态有源信号。 此信号可用于 启用其余系统的 下游电路或 活动状态指示。 此功能的 分立式实施 使用所示的 分立式组件, 以在 VOUT 拉高时 生成电源备妥信号。 当此解决方案工作时, 它需要许多组件 并会增加总体 解决方案尺寸。 有关电源开关, 讨论的最后一个解决方案 是负载开关。 通过在启用的引脚上 使用 GPIO 信号 可以控制这个 单片解决方案,且高电平和低电平解决方案均 存在。 对于 PMOS 开关, 开态电阻 通过将 PMOS 门 驱动到地面来优化。 对于 MSOS 开关, 此项同样的优化 是通过使用内部 充电泵生成 高栅极电压实现的。 在顶端部分, 负载开关 与其他 功能集成, 以使开关 更为稳定。 此处唯一优势是 设计灵活性, 因为分立式解决方案 可使用该应用程序需要的 任何 MOSFET, 存在数千 MOSFET 可供选择。 话虽如此, 我们有许多负载开关可用, 有些开关甚至能够 配置为更好地满足 特定应用需要。 查看左侧的 负载开关开启行为, 负载开关 能够控制 输出电压 和电流, 使其能够线性上升。 与先前讨论的 PMOS 解决方案相比, 该解决方案没有任何 负输出电压。 有些负载开关甚至 使用外部电容器 提供可调节的上升时间。 将涌浪电流与失控的 分立式解决方案进行比较, 我们可以见到 涌浪电流低得多, 并且在整个输出 电压斜升过程中保持连续。 需要注意的另一点是, 在将 VIN 首次 应用到 负载开关时, 没有输出电压 或一路穿行至输出端的 输出电压。 第三 PMOS 解决方案 可出现此情况, 因为电容使栅极 充电减慢。 与右侧的 负载开关相比, 该图在左侧展示了 分立解决方案的 二进制记数法。 使用 PMOS-NMOS 电阻器与电容器的 分立式解决方案 好比右侧的 负载开关 TPS22965。 负载开关尺寸小 77% 并使用更少组件。 这意味着挑选和 置入成本已降低 并且系统 PCB 可能会更小, 使得能够 获得更小的外形。 现在,让我们了解一下 将额外特性添加到 负载开关解决方案。 如采用分立式解决方案, 则添加快速输出放电 就需要逆变器 和晶体管。 如采用负载开关, 则已集成 快速输出放电, 在器件已禁用后, 实施内部 电阻接地, 接至输出端。 此外,还有在系统不需要时 就不进行 快速输出放电的 负载开关。 该解决方案 无需配备。 要将反向电流阻断 添加到分立式解决方案, 需要添加额外的 MOSFET。 对于具有反向 电流阻断的负载开关, 无需 额外的组件。 当负载开关 关闭后, 开关将自动 阻断反向电流。 电源正常的 分立式实施 涉及多种 分立式元件 以在 VOUT 高时 生成合适的信号。 如采用负载开关, 则提供了开漏 PG 引脚。 通过使用电阻 拉高引脚, 可生成有源 高 PG 信号。 总而言之, 左侧的电路 显示 电源开关的 分立式实施, 且具有快速输出放电, 反向电流阻断 以及电源正常。 要实施具有所有 这些功能的 负载开关解决方案, 只需带 PG 电阻器的 TPS22953 负载 开关即可。 扼要重述一下,让我们回顾 展示的所有对比 解决方案。 第一个 RMOS 解决方案简单, 仅需一个组件。 但是,此解决方案受到 非理想化导通电阻性能 以及失控开启影响, 导致开关期间的 涌浪电流大。 第二个解决方案 优化了导通电阻性能, 但是,增加了 一个经由其添加的 电阻器接地漏电的路径。 并且,它也未修正 在开关期间出现的 电压斜坡失控 或涌浪电流问题。 第三个解决方案能够控制 电压斜坡和涌浪电流, 但是增加了负输出电压, 并且未能阻断 在 VIN 首次应用到 该解决方案时的 电压和电流。 NMOS 解决方案在交流电方面 需要考虑的事项与 PMOS 解决方案相同, 它还能够在 低输入电压下 提供更佳的性能。 这些解决方案 可能更为复杂, 但是,由于需要将电路 应用到 NMOS 的 高压栅极。 负载开关提供 具有受控的上升时间、 小解决方案尺寸、 优化的导通电阻, 以及多项集成功能的 单片解决方案。 在此幻灯片上列有 要记住的多项关键内容。 首先,电源开关已广泛 应用到各个市场领域 以及多种不同的终端设备上。 要查找原理图上的 分立式电源开关 解决方案, 查找水平 MOSFET。 第二,简单的 分立式解决方案 没有受控的 上升时间 并会产生大量 涌浪电流。 可以添加更多组件 以控制电压斜坡速率, 但是这会增加解决方案尺寸 和 BOM 计数。 最终,可将 负载开关用作 电源开关的 单片解决方案, 并用于在分立式 实施过程中 提供多项改善。 有关负载开关的 更多信息, 请查阅德州仪器 (TI) 提供的其他 一些附加资源。 我们提供了 多项 TI 设计, 以展示可以如何使用负载开关 来解决现实中的终端设备 问题。 此 TI 设计创建了 SSD 电力输送 解决方案,展示了 TPS22954 负载开关的 功能和小尺寸。 可穿戴设备的 发运模式显示了 可如何使用 负载开关 在最终设备仍在置物架上时 就断开电池与系统其余部分的 连接。 这最大程度 减少了终端设备的 电池消耗并增强了客户的 开箱即用体验。 此 TI 设计占空比 周期负载开关 可显示动态 切换负载开关 可如何为最终设备 产生实质性的功率节省。 左侧的 TI 设计显示 并联多个 负载开关 可如何降低 开态电阻, 并提高载流能力。 右侧的 TI 设计显示了 可如何使用 负载开关进行 电源多路复用和反向电流阻断。 德州仪器 (TI) 还 向多种负载开关 提供 WEBENCH 支持, 这能够有助于负载开关的 参数与性能建模。 最后,我们提供了 多份应用手册, 其中 提供了 有关各种不同负载开关的 功能与配置的详细信息。 感谢您抽时间 观看本演示。 有关更多信息和 查看所有资源, 请访问德州仪器 (TI) 负载开关主页, 网址为 www.ti.com/loadswitch。 如有任何问题,请在负载开关 与电源路径 保护 E2E 论坛上 发帖。

本视频的标题为 电源开关解决方案对比 - 分立式 MOSFET 与 集成负载开关。 本次培训中,您将 学习什么是电源开关 解决方案及如何识别 电路图中的分立式 MOSFET 开关解决方案。 在此过程中,我们将从 直流电与交流电角度 分析分立式开关 解决方案的性能。 然后介绍负载 开关解决方案 并将其性能 与 MOSFET 解决 方案进行比较。 接着,让我们 开始介绍。 电源开关 通常指的是 连接和断开 到负载的电源。 电源开关位于 系统电源 与负载之间, 此开关将控制 何时从电源 对负载供电 或不供电。 工程师在其系统中 使用电源开关的 原因是多方面的。 系统启动期间, 如果电源必须同时 对所有系统 负载供电, 供电压力 会较大。 使用电源开关, 这些负载 则可以一次开启一个, 这样可以毫无问题地 启动电源。 电源开关还可以 被用来降低 电源电压 升高的速度。 这会有助于控制 大负载电容 充电过程中产生的 涌浪电流数量。 电源开关的 另一个原因 是减少电力消耗。 在具有功耗意识的 系统中,如使用 电池供电的应用, 电力消耗 是关键问题所在。 为使系统 更有效率, 可将不需要 供电的负载关闭, 不使用时可以 使用电源开关 断开负载 与电源。 对于处理器和 FPGA 应用程序, 需使用电源轨排序 以便正常运行。 电源开关可被用来 对这些电源轨进行排序 并保证正确 启动系统。 哪些市场和终端设备 使用电源开关? 几乎所有都使用。 在个人电子 产品中, 有许多使用电池 供电的应用, 如笔记本电脑、平板电脑 及穿戴式计算机, 它们均采用电源 开关来禁用 未用的子系统。 这样可以降低 系统的电力消耗 并提高电池寿命。 在工业市场中, 移动销售点机器 使用电源开关以节约 电池寿命,而 COM express 模块 使用电源 开关来调节 哪些电压轨 投入使用 及系统是否 处于待机状态。 汽车使用电源 开关以便对应用 处理器和 信息娱乐系统和仪表组应用 进行电力排序。 电源开关还可 用于打开和关闭 汽车照明灯。 在企业市场中, 服务器需要 电源开关来 控制系统启动。 各服务器拥有多个 必须通电的硬驱动。 若要防止 供电压力, 可使用开关同时 打开少数硬驱动。 这样将允许 电源供应 逐渐安全开启。 实现电源开关的 一种方法就是 使用分立式解决方案。 这些解决方案使用 MOSFET 来接通和切断 对某负载的电源。 许多时候,MOSFET 周围设有几个 分立组件, 以帮助控制开关 或添加额外功能。 若要在电路图中 找到其中一个解决方案, 建议搜索 水平绘制的 FET。 许多时候会为系统中 某电源开关应用采用 这些 MOSFET。 我们将查看的第一个 分立式 MOSFET 解决方案 是 PMOS 解决方案。 使用该解决方案的较大 优势就在于它的简单。 仅需一个组件。 通过连接 PMOS 栅极至 GPIO, GPIO 可以控制 是接通还是切断 PMOS。 但是,这是一种 低电平解决方案, 意味着 GPIO 必须较高 开关才会关闭。 这会是一种弊端, 因为需要先接通 系统电源,然后才会将电源 从 VIN 拦截到 VOUT。 该解决方案中的 另一个弊端是 GPIO 变化。 至于该解决方案的 最佳性能, 当开关打开时, MOSFET 从 VIN 到 VOUT 的导通电阻 或电阻应非常低。 这导致给定负载 电流情况下, VIN 落到 VOUT的 电压最低。 若要最大程度 减少导通电阻, 电源与 PMOS 栅极间的 电压差必须较高。 因此,该解决 方案的最佳性能 是将栅极拉至 0 伏特时。 如果 GPIO 信号 出现变化, 那么数字低输出 会更接近 更接近 200 或 300 毫伏, 导致解决方案 性能不理想。 这也会使该解决 方案很难使用 较低电压。 VIN 不能低于 MOSFET 的 通电阈值。 所以,如果电压 低于该阈值, 它会阻止 系统通电。 对于下列 范围截屏,每个轨迹 均贴有标签 并对右图 进行颜色编码。 从顶部开始,我们 拥有 ON 引脚电压、 VIN 电压、 VOUT 电压 及流过 FET 的电流。 对于本例, VOUT 电容 为 4.7 微法拉。 范围截屏显示 ON 引脚从高走向低。 因此低电平解决方案 从切断改为接通。 VOUT 电压 如预期般升高。 但我们发现,VIN 电压 降低,电流高峰 大约为 2.2 安培。 这是因为 开关接通时, 电压升温速率 失控并在几纳秒内 升高。 这种快速通电 会导致电容 快速充电。 根据方程式 I = C/dt, 这会导致 涌浪电流较大。 在这种情况下, 仅需 4.7 微法拉 即可产生 2 安培 以上涌浪电流。 因此,电源供应 无法处理负载, 必须降低电压进行补偿。 该涌浪电流会导致 意外的系统性能, 如外接口或 PCB 轨迹重置 或损坏。 第二种解决方案增加了 电阻和 NMOS 晶体管。 通过控制 NMOS 晶体管栅极, 本解决方案 变为高电平, 意味着电压高时 可以接通系统, 电压低时可以 切断系统。 而且,NMOS 可以 将 PMOS 栅极 拉至 0 伏特状态, 这样可以优化 该解决方案的 导通电阻性能。 但是,较低 电压仍然 不能用于 该解决方案。 当解决方案接通时, 增加电阻器 会增加其 漏电路径。 电阻越低, 漏电量越高。 电阻越高, 漏电量越低。 从交流电角度来看, 变化不大。 解决方案仍然不能 控制输出电压 升高的速率。 输出电容 再次导致 大涌浪电流。 我们将查看的最后一个 PMOS 解决方案 增加了一个附加电容器, 并对涌浪电流有所帮助。 从直流电角度来看, 没有任何变化。 高电平解决 方案仍然可以 优化导通 电阻性能, 当解决方案 通电时 放电路径仍然存在。 使用此解决方案,电压 斜坡率会得到控制。 通过增加栅极与 VOUT 之间的电容, 电压上升时间 可能会增长, 这会使 涌浪电流降低。 例如,电容为 47 微法拉时, 电压上升 时间大约 为 150 微秒 且涌浪电流 由 2 安培 降至 200 毫安。 电容较高时, 涌浪电流 甚至降低更多。 请记住, 如果通电时间 增加,断电 时间也会增加, 这意味着解决方案 如需要缓慢通电 和快速断电时间 则不能正常运行。 左侧显示的范围 表明本解决方案 通电并连接 3 安培负载, 我们可以看到, 电压和电流 均受控。 虽然此解决方案 能够提供 电压和电流 均适用的线性斜坡, 但是观察到一项异常。 在首次开启 解决方案时, 负电压和 负电流均会出现。 这是开机时 电容的 预充方式造成的。 在此期间, PMOS 的栅极较高, 且 VOUT 为 0 伏。 电容器将 充电至 VIN 值, 如图所示。 当此解决方案开启后, PMOS 栅极变低, 并且电容 会通过 NMOS 放电至接地。 在该解决方案 有时间完全开启前, 此放电将 VOUT 下拉。 虽然较高的电阻能够 有助于降低涌浪电流, 它还会为 该解决方案 产生更多的负电压和电流。 在 47 微法拉条件下, 在 VOUT 观察到负 1 伏。 如果负载输入 无法处理此负电压, 这可导致 负载受损。 当首次 应用 VIN 时, 此解决方案还会出现 另一问题。 在系统中,此情况可以是 插入电池 或初始系统启动。 在此期间, 栅极电压为 0 伏。 当应用 VIN 后,栅极至 VOUT 的电容器 使 PMOS 栅极的 充电时间变长。 虽然栅极 仍然在充电, 但是该解决方案 未完全关闭, 并且可见到功率 从 VIN 流至 VOUT, 即使该解决方案 已关闭,也是如此。 如果在系统启动期间 不要求对负载加电, 则不能使用 该解决方案。 现在,我们研究了 PMOS 解决方案, 接下来我们将讨论 NMOS 解决方案。 从交流电角度来看, 规则没变。 需要添加电容 以降满栅极充电速度, 从而可以控制 输出电压。 如不添加, 则输出电压将失控, 并且将产生大 涌浪电流。 从直流电角度来看, 事情对于 NMOS 略有不同。 栅极需要高于 VIN 才能使解决方案启动。 这意味着该解决方案 能够开关较低的输入电压, 而不会有任何问题。 为获得最佳 导通电阻性能, VIN 和栅极 之间的电压差 应是高电压差。 为此, 栅极电压 必须远高于 VIN。 左侧显示了此问题的 两个解决方案。 第一个解决方案使用 充电泵,取 VIN 的值并 从中生成 较高的电压, 这可与栅极上使用。 第二个解决方案 使用多个分立式组件, 并可在系统中 有较高电压轨时 使用。 虽然两个解决方案 均可使用高栅极电压 以最大程度减少导通电阻, 它们占用许多空间 并使用许多组件 才能达成目标。 现在,让我们看一看, 向这些分立式解决方案 添加附加功能 所需的一些 分立式电路。 快速输出 放电,或者说 QOD, 用于拉低开关 解决方案关闭时的 输出电压。 这将保证 负载的电压 拉低至 0 伏 并且该负载 已完全关闭。 要以分立形式达成此目的, 有两种解决方案。 选项 1 是在 输出端添加 旁漏电阻,这将 在解决方案关闭时 使负载放电。 但是,这也会在 解决方案开启时, 通过该电阻提供 漏电路径。 选项 2 使用 逆变器和晶体管。 该解决方案将仅 通过晶体管 在关闭开关时 在输出端放电。 由于在分立式 开关解决方案中 MOSFET 体二极管具有朝向, 从 VIN 至 VOUT 的 电流被阻断。 但是,如果 VOUT 大于 VIN, 则电流能够从 VOUT 流至 VIN。 要实施反向 电流阻断, 必须额外添加两个晶体管, 且将其体二极管 朝相反方向。 该解决方案将在关闭时 阻断两个方向的电流, 但是将使开关的 导通电阻翻倍, 因为两个 MOSFET 为相互串联。 Power Good(电源正常)功能会在 开关解决方案开启 并且输出电压高时 提供 高态有源信号。 此信号可用于 启用其余系统的 下游电路或 活动状态指示。 此功能的 分立式实施 使用所示的 分立式组件, 以在 VOUT 拉高时 生成电源备妥信号。 当此解决方案工作时, 它需要许多组件 并会增加总体 解决方案尺寸。 有关电源开关, 讨论的最后一个解决方案 是负载开关。 通过在启用的引脚上 使用 GPIO 信号 可以控制这个 单片解决方案,且高电平和低电平解决方案均 存在。 对于 PMOS 开关, 开态电阻 通过将 PMOS 门 驱动到地面来优化。 对于 MSOS 开关, 此项同样的优化 是通过使用内部 充电泵生成 高栅极电压实现的。 在顶端部分, 负载开关 与其他 功能集成, 以使开关 更为稳定。 此处唯一优势是 设计灵活性, 因为分立式解决方案 可使用该应用程序需要的 任何 MOSFET, 存在数千 MOSFET 可供选择。 话虽如此, 我们有许多负载开关可用, 有些开关甚至能够 配置为更好地满足 特定应用需要。 查看左侧的 负载开关开启行为, 负载开关 能够控制 输出电压 和电流, 使其能够线性上升。 与先前讨论的 PMOS 解决方案相比, 该解决方案没有任何 负输出电压。 有些负载开关甚至 使用外部电容器 提供可调节的上升时间。 将涌浪电流与失控的 分立式解决方案进行比较, 我们可以见到 涌浪电流低得多, 并且在整个输出 电压斜升过程中保持连续。 需要注意的另一点是, 在将 VIN 首次 应用到 负载开关时, 没有输出电压 或一路穿行至输出端的 输出电压。 第三 PMOS 解决方案 可出现此情况, 因为电容使栅极 充电减慢。 与右侧的 负载开关相比, 该图在左侧展示了 分立解决方案的 二进制记数法。 使用 PMOS-NMOS 电阻器与电容器的 分立式解决方案 好比右侧的 负载开关 TPS22965。 负载开关尺寸小 77% 并使用更少组件。 这意味着挑选和 置入成本已降低 并且系统 PCB 可能会更小, 使得能够 获得更小的外形。 现在,让我们了解一下 将额外特性添加到 负载开关解决方案。 如采用分立式解决方案, 则添加快速输出放电 就需要逆变器 和晶体管。 如采用负载开关, 则已集成 快速输出放电, 在器件已禁用后, 实施内部 电阻接地, 接至输出端。 此外,还有在系统不需要时 就不进行 快速输出放电的 负载开关。 该解决方案 无需配备。 要将反向电流阻断 添加到分立式解决方案, 需要添加额外的 MOSFET。 对于具有反向 电流阻断的负载开关, 无需 额外的组件。 当负载开关 关闭后, 开关将自动 阻断反向电流。 电源正常的 分立式实施 涉及多种 分立式元件 以在 VOUT 高时 生成合适的信号。 如采用负载开关, 则提供了开漏 PG 引脚。 通过使用电阻 拉高引脚, 可生成有源 高 PG 信号。 总而言之, 左侧的电路 显示 电源开关的 分立式实施, 且具有快速输出放电, 反向电流阻断 以及电源正常。 要实施具有所有 这些功能的 负载开关解决方案, 只需带 PG 电阻器的 TPS22953 负载 开关即可。 扼要重述一下,让我们回顾 展示的所有对比 解决方案。 第一个 RMOS 解决方案简单, 仅需一个组件。 但是,此解决方案受到 非理想化导通电阻性能 以及失控开启影响, 导致开关期间的 涌浪电流大。 第二个解决方案 优化了导通电阻性能, 但是,增加了 一个经由其添加的 电阻器接地漏电的路径。 并且,它也未修正 在开关期间出现的 电压斜坡失控 或涌浪电流问题。 第三个解决方案能够控制 电压斜坡和涌浪电流, 但是增加了负输出电压, 并且未能阻断 在 VIN 首次应用到 该解决方案时的 电压和电流。 NMOS 解决方案在交流电方面 需要考虑的事项与 PMOS 解决方案相同, 它还能够在 低输入电压下 提供更佳的性能。 这些解决方案 可能更为复杂, 但是,由于需要将电路 应用到 NMOS 的 高压栅极。 负载开关提供 具有受控的上升时间、 小解决方案尺寸、 优化的导通电阻, 以及多项集成功能的 单片解决方案。 在此幻灯片上列有 要记住的多项关键内容。 首先,电源开关已广泛 应用到各个市场领域 以及多种不同的终端设备上。 要查找原理图上的 分立式电源开关 解决方案, 查找水平 MOSFET。 第二,简单的 分立式解决方案 没有受控的 上升时间 并会产生大量 涌浪电流。 可以添加更多组件 以控制电压斜坡速率, 但是这会增加解决方案尺寸 和 BOM 计数。 最终,可将 负载开关用作 电源开关的 单片解决方案, 并用于在分立式 实施过程中 提供多项改善。 有关负载开关的 更多信息, 请查阅德州仪器 (TI) 提供的其他 一些附加资源。 我们提供了 多项 TI 设计, 以展示可以如何使用负载开关 来解决现实中的终端设备 问题。 此 TI 设计创建了 SSD 电力输送 解决方案,展示了 TPS22954 负载开关的 功能和小尺寸。 可穿戴设备的 发运模式显示了 可如何使用 负载开关 在最终设备仍在置物架上时 就断开电池与系统其余部分的 连接。 这最大程度 减少了终端设备的 电池消耗并增强了客户的 开箱即用体验。 此 TI 设计占空比 周期负载开关 可显示动态 切换负载开关 可如何为最终设备 产生实质性的功率节省。 左侧的 TI 设计显示 并联多个 负载开关 可如何降低 开态电阻, 并提高载流能力。 右侧的 TI 设计显示了 可如何使用 负载开关进行 电源多路复用和反向电流阻断。 德州仪器 (TI) 还 向多种负载开关 提供 WEBENCH 支持, 这能够有助于负载开关的 参数与性能建模。 最后,我们提供了 多份应用手册, 其中 提供了 有关各种不同负载开关的 功能与配置的详细信息。 感谢您抽时间 观看本演示。 有关更多信息和 查看所有资源, 请访问德州仪器 (TI) 负载开关主页, 网址为 www.ti.com/loadswitch。 如有任何问题,请在负载开关 与电源路径 保护 E2E 论坛上 发帖。

本视频的标题为 电源开关解决方案对比 -

分立式 MOSFET 与 集成负载开关。

本次培训中,您将 学习什么是电源开关

解决方案及如何识别 电路图中的分立式 MOSFET

开关解决方案。

在此过程中,我们将从 直流电与交流电角度

分析分立式开关 解决方案的性能。

然后介绍负载 开关解决方案

并将其性能 与 MOSFET 解决

方案进行比较。

接着,让我们 开始介绍。

电源开关 通常指的是

连接和断开 到负载的电源。

电源开关位于 系统电源

与负载之间, 此开关将控制

何时从电源 对负载供电

或不供电。

工程师在其系统中 使用电源开关的

原因是多方面的。

系统启动期间, 如果电源必须同时

对所有系统 负载供电,

供电压力 会较大。

使用电源开关, 这些负载

则可以一次开启一个, 这样可以毫无问题地

启动电源。

电源开关还可以 被用来降低

电源电压 升高的速度。

这会有助于控制 大负载电容

充电过程中产生的 涌浪电流数量。

电源开关的 另一个原因

是减少电力消耗。

在具有功耗意识的 系统中,如使用

电池供电的应用, 电力消耗

是关键问题所在。

为使系统 更有效率,

可将不需要 供电的负载关闭,

不使用时可以 使用电源开关

断开负载 与电源。

对于处理器和 FPGA 应用程序,

需使用电源轨排序 以便正常运行。

电源开关可被用来 对这些电源轨进行排序

并保证正确 启动系统。

哪些市场和终端设备 使用电源开关?

几乎所有都使用。

在个人电子 产品中,

有许多使用电池 供电的应用,

如笔记本电脑、平板电脑 及穿戴式计算机,

它们均采用电源 开关来禁用

未用的子系统。

这样可以降低 系统的电力消耗

并提高电池寿命。

在工业市场中, 移动销售点机器

使用电源开关以节约 电池寿命,而 COM express 模块

使用电源 开关来调节

哪些电压轨 投入使用

及系统是否 处于待机状态。

汽车使用电源 开关以便对应用

处理器和 信息娱乐系统和仪表组应用

进行电力排序。

电源开关还可 用于打开和关闭

汽车照明灯。

在企业市场中, 服务器需要

电源开关来 控制系统启动。

各服务器拥有多个 必须通电的硬驱动。

若要防止 供电压力,

可使用开关同时 打开少数硬驱动。

这样将允许 电源供应

逐渐安全开启。

实现电源开关的 一种方法就是

使用分立式解决方案。

这些解决方案使用 MOSFET 来接通和切断

对某负载的电源。

许多时候,MOSFET 周围设有几个

分立组件, 以帮助控制开关

或添加额外功能。

若要在电路图中 找到其中一个解决方案,

建议搜索 水平绘制的

FET。

许多时候会为系统中 某电源开关应用采用

这些 MOSFET。

我们将查看的第一个 分立式 MOSFET 解决方案

是 PMOS 解决方案。

使用该解决方案的较大 优势就在于它的简单。

仅需一个组件。

通过连接 PMOS 栅极至 GPIO,

GPIO 可以控制 是接通还是切断 PMOS。

但是,这是一种 低电平解决方案,

意味着 GPIO 必须较高

开关才会关闭。

这会是一种弊端, 因为需要先接通

系统电源,然后才会将电源 从 VIN 拦截到 VOUT。

该解决方案中的 另一个弊端是 GPIO 变化。

至于该解决方案的 最佳性能,

当开关打开时, MOSFET 从 VIN

到 VOUT 的导通电阻 或电阻应非常低。

这导致给定负载 电流情况下,

VIN 落到 VOUT的 电压最低。

若要最大程度 减少导通电阻,

电源与 PMOS 栅极间的 电压差必须较高。

因此,该解决 方案的最佳性能

是将栅极拉至 0 伏特时。

如果 GPIO 信号 出现变化,

那么数字低输出 会更接近

更接近 200 或 300 毫伏,

导致解决方案 性能不理想。

这也会使该解决 方案很难使用

较低电压。 VIN 不能低于 MOSFET 的

通电阈值。

所以,如果电压 低于该阈值,

它会阻止 系统通电。

对于下列 范围截屏,每个轨迹

均贴有标签 并对右图

进行颜色编码。

从顶部开始,我们 拥有 ON 引脚电压、

VIN 电压、 VOUT 电压

及流过 FET 的电流。

对于本例, VOUT 电容

为 4.7 微法拉。

范围截屏显示 ON 引脚从高走向低。

因此低电平解决方案 从切断改为接通。

VOUT 电压 如预期般升高。

但我们发现,VIN 电压 降低,电流高峰

大约为 2.2 安培。

这是因为 开关接通时,

电压升温速率 失控并在几纳秒内

升高。

这种快速通电 会导致电容

快速充电。

根据方程式 I = C/dt,

这会导致 涌浪电流较大。

在这种情况下, 仅需 4.7 微法拉

即可产生 2 安培 以上涌浪电流。

因此,电源供应 无法处理负载,

必须降低电压进行补偿。

该涌浪电流会导致 意外的系统性能,

如外接口或 PCB 轨迹重置

或损坏。

第二种解决方案增加了 电阻和 NMOS 晶体管。

通过控制 NMOS 晶体管栅极,

本解决方案 变为高电平,

意味着电压高时 可以接通系统,

电压低时可以 切断系统。

而且,NMOS 可以 将 PMOS 栅极

拉至 0 伏特状态, 这样可以优化

该解决方案的 导通电阻性能。

但是,较低 电压仍然

不能用于 该解决方案。

当解决方案接通时, 增加电阻器

会增加其 漏电路径。

电阻越低, 漏电量越高。

电阻越高, 漏电量越低。

从交流电角度来看, 变化不大。

解决方案仍然不能 控制输出电压

升高的速率。

输出电容 再次导致

大涌浪电流。

我们将查看的最后一个 PMOS 解决方案

增加了一个附加电容器, 并对涌浪电流有所帮助。

从直流电角度来看, 没有任何变化。

高电平解决 方案仍然可以

优化导通 电阻性能,

当解决方案 通电时

放电路径仍然存在。

使用此解决方案,电压 斜坡率会得到控制。

通过增加栅极与 VOUT 之间的电容,

电压上升时间 可能会增长,

这会使 涌浪电流降低。

例如,电容为 47 微法拉时,

电压上升 时间大约

为 150 微秒 且涌浪电流

由 2 安培 降至 200 毫安。

电容较高时, 涌浪电流

甚至降低更多。

请记住, 如果通电时间

增加,断电 时间也会增加,

这意味着解决方案 如需要缓慢通电

和快速断电时间 则不能正常运行。

左侧显示的范围 表明本解决方案

通电并连接 3 安培负载,

我们可以看到, 电压和电流

均受控。

虽然此解决方案 能够提供

电压和电流 均适用的线性斜坡,

但是观察到一项异常。

在首次开启 解决方案时,

负电压和 负电流均会出现。

这是开机时 电容的

预充方式造成的。

在此期间, PMOS 的栅极较高,

且 VOUT 为 0 伏。

电容器将 充电至 VIN 值,

如图所示。

当此解决方案开启后, PMOS 栅极变低,

并且电容 会通过 NMOS

放电至接地。

在该解决方案 有时间完全开启前,

此放电将 VOUT 下拉。

虽然较高的电阻能够 有助于降低涌浪电流,

它还会为 该解决方案

产生更多的负电压和电流。

在 47 微法拉条件下, 在 VOUT 观察到负 1 伏。

如果负载输入 无法处理此负电压,

这可导致 负载受损。

当首次 应用 VIN 时,

此解决方案还会出现 另一问题。

在系统中,此情况可以是 插入电池

或初始系统启动。

在此期间, 栅极电压为 0 伏。

当应用 VIN 后,栅极至 VOUT 的电容器

使 PMOS 栅极的 充电时间变长。

虽然栅极 仍然在充电,

但是该解决方案 未完全关闭,

并且可见到功率 从 VIN 流至 VOUT,

即使该解决方案 已关闭,也是如此。

如果在系统启动期间 不要求对负载加电,

则不能使用 该解决方案。

现在,我们研究了 PMOS 解决方案,

接下来我们将讨论 NMOS 解决方案。

从交流电角度来看, 规则没变。

需要添加电容 以降满栅极充电速度,

从而可以控制 输出电压。

如不添加, 则输出电压将失控,

并且将产生大 涌浪电流。

从直流电角度来看, 事情对于

NMOS 略有不同。

栅极需要高于 VIN 才能使解决方案启动。

这意味着该解决方案 能够开关较低的输入电压,

而不会有任何问题。

为获得最佳 导通电阻性能,

VIN 和栅极 之间的电压差

应是高电压差。

为此, 栅极电压

必须远高于 VIN。

左侧显示了此问题的 两个解决方案。

第一个解决方案使用 充电泵,取 VIN 的值并

从中生成 较高的电压,

这可与栅极上使用。

第二个解决方案 使用多个分立式组件,

并可在系统中 有较高电压轨时

使用。

虽然两个解决方案 均可使用高栅极电压

以最大程度减少导通电阻, 它们占用许多空间

并使用许多组件 才能达成目标。

现在,让我们看一看, 向这些分立式解决方案

添加附加功能 所需的一些

分立式电路。

快速输出 放电,或者说 QOD,

用于拉低开关 解决方案关闭时的

输出电压。

这将保证 负载的电压

拉低至 0 伏 并且该负载

已完全关闭。

要以分立形式达成此目的, 有两种解决方案。

选项 1 是在 输出端添加

旁漏电阻,这将 在解决方案关闭时

使负载放电。

但是,这也会在 解决方案开启时,

通过该电阻提供 漏电路径。

选项 2 使用 逆变器和晶体管。

该解决方案将仅 通过晶体管

在关闭开关时 在输出端放电。

由于在分立式 开关解决方案中

MOSFET 体二极管具有朝向,

从 VIN 至 VOUT 的 电流被阻断。

但是,如果 VOUT 大于 VIN,

则电流能够从 VOUT 流至 VIN。

要实施反向 电流阻断,

必须额外添加两个晶体管, 且将其体二极管

朝相反方向。

该解决方案将在关闭时 阻断两个方向的电流,

但是将使开关的 导通电阻翻倍,

因为两个 MOSFET 为相互串联。

Power Good(电源正常)功能会在 开关解决方案开启

并且输出电压高时 提供

高态有源信号。

此信号可用于 启用其余系统的

下游电路或 活动状态指示。

此功能的 分立式实施

使用所示的 分立式组件,

以在 VOUT 拉高时

生成电源备妥信号。

当此解决方案工作时, 它需要许多组件

并会增加总体 解决方案尺寸。

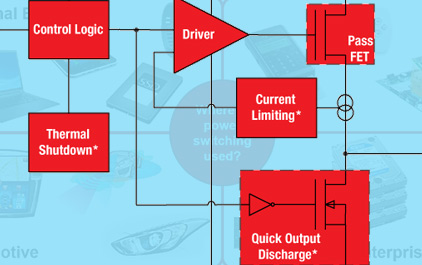

有关电源开关, 讨论的最后一个解决方案

是负载开关。

通过在启用的引脚上 使用 GPIO 信号

可以控制这个 单片解决方案,且高电平和低电平解决方案均

存在。

对于 PMOS 开关, 开态电阻

通过将 PMOS 门 驱动到地面来优化。

对于 MSOS 开关, 此项同样的优化

是通过使用内部 充电泵生成

高栅极电压实现的。

在顶端部分, 负载开关

与其他 功能集成,

以使开关 更为稳定。

此处唯一优势是 设计灵活性,

因为分立式解决方案 可使用该应用程序需要的

任何 MOSFET, 存在数千 MOSFET

可供选择。

话虽如此, 我们有许多负载开关可用,

有些开关甚至能够 配置为更好地满足

特定应用需要。

查看左侧的 负载开关开启行为,

负载开关 能够控制

输出电压 和电流,

使其能够线性上升。

与先前讨论的 PMOS 解决方案相比,

该解决方案没有任何 负输出电压。

有些负载开关甚至 使用外部电容器

提供可调节的上升时间。

将涌浪电流与失控的 分立式解决方案进行比较,

我们可以见到 涌浪电流低得多,

并且在整个输出 电压斜升过程中保持连续。

需要注意的另一点是, 在将 VIN 首次

应用到 负载开关时,

没有输出电压 或一路穿行至输出端的

输出电压。

第三 PMOS 解决方案 可出现此情况,

因为电容使栅极 充电减慢。

与右侧的 负载开关相比,

该图在左侧展示了 分立解决方案的

二进制记数法。

使用 PMOS-NMOS 电阻器与电容器的

分立式解决方案 好比右侧的

负载开关 TPS22965。

负载开关尺寸小 77% 并使用更少组件。

这意味着挑选和 置入成本已降低

并且系统 PCB 可能会更小,

使得能够 获得更小的外形。

现在,让我们了解一下 将额外特性添加到

负载开关解决方案。

如采用分立式解决方案, 则添加快速输出放电

就需要逆变器 和晶体管。

如采用负载开关, 则已集成

快速输出放电, 在器件已禁用后,

实施内部 电阻接地,

接至输出端。

此外,还有在系统不需要时 就不进行

快速输出放电的 负载开关。

该解决方案 无需配备。

要将反向电流阻断 添加到分立式解决方案,

需要添加额外的 MOSFET。

对于具有反向 电流阻断的负载开关,

无需 额外的组件。

当负载开关 关闭后,

开关将自动 阻断反向电流。

电源正常的 分立式实施

涉及多种 分立式元件

以在 VOUT 高时 生成合适的信号。

如采用负载开关, 则提供了开漏 PG 引脚。

通过使用电阻 拉高引脚,

可生成有源 高 PG 信号。

总而言之, 左侧的电路

显示 电源开关的

分立式实施, 且具有快速输出放电,

反向电流阻断 以及电源正常。

要实施具有所有 这些功能的

负载开关解决方案, 只需带 PG 电阻器的

TPS22953 负载 开关即可。

扼要重述一下,让我们回顾 展示的所有对比

解决方案。

第一个 RMOS 解决方案简单,

仅需一个组件。

但是,此解决方案受到 非理想化导通电阻性能

以及失控开启影响,

导致开关期间的 涌浪电流大。

第二个解决方案 优化了导通电阻性能,

但是,增加了 一个经由其添加的

电阻器接地漏电的路径。

并且,它也未修正 在开关期间出现的

电压斜坡失控 或涌浪电流问题。

第三个解决方案能够控制 电压斜坡和涌浪电流,

但是增加了负输出电压, 并且未能阻断

在 VIN 首次应用到 该解决方案时的

电压和电流。

NMOS 解决方案在交流电方面 需要考虑的事项与 PMOS 解决方案相同,

它还能够在 低输入电压下

提供更佳的性能。

这些解决方案 可能更为复杂,

但是,由于需要将电路 应用到 NMOS 的

高压栅极。

负载开关提供 具有受控的上升时间、

小解决方案尺寸、 优化的导通电阻,

以及多项集成功能的 单片解决方案。

在此幻灯片上列有 要记住的多项关键内容。

首先,电源开关已广泛 应用到各个市场领域

以及多种不同的终端设备上。

要查找原理图上的 分立式电源开关

解决方案, 查找水平 MOSFET。

第二,简单的 分立式解决方案

没有受控的 上升时间

并会产生大量 涌浪电流。

可以添加更多组件 以控制电压斜坡速率,

但是这会增加解决方案尺寸 和 BOM 计数。

最终,可将 负载开关用作

电源开关的 单片解决方案,

并用于在分立式 实施过程中

提供多项改善。

有关负载开关的 更多信息,

请查阅德州仪器 (TI) 提供的其他

一些附加资源。

我们提供了 多项 TI 设计,

以展示可以如何使用负载开关 来解决现实中的终端设备

问题。

此 TI 设计创建了 SSD 电力输送

解决方案,展示了 TPS22954 负载开关的

功能和小尺寸。

可穿戴设备的 发运模式显示了

可如何使用 负载开关

在最终设备仍在置物架上时 就断开电池与系统其余部分的

连接。

这最大程度 减少了终端设备的

电池消耗并增强了客户的 开箱即用体验。

此 TI 设计占空比 周期负载开关

可显示动态 切换负载开关

可如何为最终设备 产生实质性的功率节省。

左侧的 TI 设计显示

并联多个 负载开关

可如何降低 开态电阻,

并提高载流能力。

右侧的 TI 设计显示了

可如何使用 负载开关进行

电源多路复用和反向电流阻断。

德州仪器 (TI) 还 向多种负载开关

提供 WEBENCH 支持, 这能够有助于负载开关的

参数与性能建模。

最后,我们提供了 多份应用手册,

其中 提供了

有关各种不同负载开关的 功能与配置的详细信息。

感谢您抽时间 观看本演示。

有关更多信息和 查看所有资源,

请访问德州仪器 (TI) 负载开关主页,

网址为 www.ti.com/loadswitch。

如有任何问题,请在负载开关 与电源路径

保护 E2E 论坛上 发帖。

本视频的标题为 电源开关解决方案对比 - 分立式 MOSFET 与 集成负载开关。 本次培训中,您将 学习什么是电源开关 解决方案及如何识别 电路图中的分立式 MOSFET 开关解决方案。 在此过程中,我们将从 直流电与交流电角度 分析分立式开关 解决方案的性能。 然后介绍负载 开关解决方案 并将其性能 与 MOSFET 解决 方案进行比较。 接着,让我们 开始介绍。 电源开关 通常指的是 连接和断开 到负载的电源。 电源开关位于 系统电源 与负载之间, 此开关将控制 何时从电源 对负载供电 或不供电。 工程师在其系统中 使用电源开关的 原因是多方面的。 系统启动期间, 如果电源必须同时 对所有系统 负载供电, 供电压力 会较大。 使用电源开关, 这些负载 则可以一次开启一个, 这样可以毫无问题地 启动电源。 电源开关还可以 被用来降低 电源电压 升高的速度。 这会有助于控制 大负载电容 充电过程中产生的 涌浪电流数量。 电源开关的 另一个原因 是减少电力消耗。 在具有功耗意识的 系统中,如使用 电池供电的应用, 电力消耗 是关键问题所在。 为使系统 更有效率, 可将不需要 供电的负载关闭, 不使用时可以 使用电源开关 断开负载 与电源。 对于处理器和 FPGA 应用程序, 需使用电源轨排序 以便正常运行。 电源开关可被用来 对这些电源轨进行排序 并保证正确 启动系统。 哪些市场和终端设备 使用电源开关? 几乎所有都使用。 在个人电子 产品中, 有许多使用电池 供电的应用, 如笔记本电脑、平板电脑 及穿戴式计算机, 它们均采用电源 开关来禁用 未用的子系统。 这样可以降低 系统的电力消耗 并提高电池寿命。 在工业市场中, 移动销售点机器 使用电源开关以节约 电池寿命,而 COM express 模块 使用电源 开关来调节 哪些电压轨 投入使用 及系统是否 处于待机状态。 汽车使用电源 开关以便对应用 处理器和 信息娱乐系统和仪表组应用 进行电力排序。 电源开关还可 用于打开和关闭 汽车照明灯。 在企业市场中, 服务器需要 电源开关来 控制系统启动。 各服务器拥有多个 必须通电的硬驱动。 若要防止 供电压力, 可使用开关同时 打开少数硬驱动。 这样将允许 电源供应 逐渐安全开启。 实现电源开关的 一种方法就是 使用分立式解决方案。 这些解决方案使用 MOSFET 来接通和切断 对某负载的电源。 许多时候,MOSFET 周围设有几个 分立组件, 以帮助控制开关 或添加额外功能。 若要在电路图中 找到其中一个解决方案, 建议搜索 水平绘制的 FET。 许多时候会为系统中 某电源开关应用采用 这些 MOSFET。 我们将查看的第一个 分立式 MOSFET 解决方案 是 PMOS 解决方案。 使用该解决方案的较大 优势就在于它的简单。 仅需一个组件。 通过连接 PMOS 栅极至 GPIO, GPIO 可以控制 是接通还是切断 PMOS。 但是,这是一种 低电平解决方案, 意味着 GPIO 必须较高 开关才会关闭。 这会是一种弊端, 因为需要先接通 系统电源,然后才会将电源 从 VIN 拦截到 VOUT。 该解决方案中的 另一个弊端是 GPIO 变化。 至于该解决方案的 最佳性能, 当开关打开时, MOSFET 从 VIN 到 VOUT 的导通电阻 或电阻应非常低。 这导致给定负载 电流情况下, VIN 落到 VOUT的 电压最低。 若要最大程度 减少导通电阻, 电源与 PMOS 栅极间的 电压差必须较高。 因此,该解决 方案的最佳性能 是将栅极拉至 0 伏特时。 如果 GPIO 信号 出现变化, 那么数字低输出 会更接近 更接近 200 或 300 毫伏, 导致解决方案 性能不理想。 这也会使该解决 方案很难使用 较低电压。 VIN 不能低于 MOSFET 的 通电阈值。 所以,如果电压 低于该阈值, 它会阻止 系统通电。 对于下列 范围截屏,每个轨迹 均贴有标签 并对右图 进行颜色编码。 从顶部开始,我们 拥有 ON 引脚电压、 VIN 电压、 VOUT 电压 及流过 FET 的电流。 对于本例, VOUT 电容 为 4.7 微法拉。 范围截屏显示 ON 引脚从高走向低。 因此低电平解决方案 从切断改为接通。 VOUT 电压 如预期般升高。 但我们发现,VIN 电压 降低,电流高峰 大约为 2.2 安培。 这是因为 开关接通时, 电压升温速率 失控并在几纳秒内 升高。 这种快速通电 会导致电容 快速充电。 根据方程式 I = C/dt, 这会导致 涌浪电流较大。 在这种情况下, 仅需 4.7 微法拉 即可产生 2 安培 以上涌浪电流。 因此,电源供应 无法处理负载, 必须降低电压进行补偿。 该涌浪电流会导致 意外的系统性能, 如外接口或 PCB 轨迹重置 或损坏。 第二种解决方案增加了 电阻和 NMOS 晶体管。 通过控制 NMOS 晶体管栅极, 本解决方案 变为高电平, 意味着电压高时 可以接通系统, 电压低时可以 切断系统。 而且,NMOS 可以 将 PMOS 栅极 拉至 0 伏特状态, 这样可以优化 该解决方案的 导通电阻性能。 但是,较低 电压仍然 不能用于 该解决方案。 当解决方案接通时, 增加电阻器 会增加其 漏电路径。 电阻越低, 漏电量越高。 电阻越高, 漏电量越低。 从交流电角度来看, 变化不大。 解决方案仍然不能 控制输出电压 升高的速率。 输出电容 再次导致 大涌浪电流。 我们将查看的最后一个 PMOS 解决方案 增加了一个附加电容器, 并对涌浪电流有所帮助。 从直流电角度来看, 没有任何变化。 高电平解决 方案仍然可以 优化导通 电阻性能, 当解决方案 通电时 放电路径仍然存在。 使用此解决方案,电压 斜坡率会得到控制。 通过增加栅极与 VOUT 之间的电容, 电压上升时间 可能会增长, 这会使 涌浪电流降低。 例如,电容为 47 微法拉时, 电压上升 时间大约 为 150 微秒 且涌浪电流 由 2 安培 降至 200 毫安。 电容较高时, 涌浪电流 甚至降低更多。 请记住, 如果通电时间 增加,断电 时间也会增加, 这意味着解决方案 如需要缓慢通电 和快速断电时间 则不能正常运行。 左侧显示的范围 表明本解决方案 通电并连接 3 安培负载, 我们可以看到, 电压和电流 均受控。 虽然此解决方案 能够提供 电压和电流 均适用的线性斜坡, 但是观察到一项异常。 在首次开启 解决方案时, 负电压和 负电流均会出现。 这是开机时 电容的 预充方式造成的。 在此期间, PMOS 的栅极较高, 且 VOUT 为 0 伏。 电容器将 充电至 VIN 值, 如图所示。 当此解决方案开启后, PMOS 栅极变低, 并且电容 会通过 NMOS 放电至接地。 在该解决方案 有时间完全开启前, 此放电将 VOUT 下拉。 虽然较高的电阻能够 有助于降低涌浪电流, 它还会为 该解决方案 产生更多的负电压和电流。 在 47 微法拉条件下, 在 VOUT 观察到负 1 伏。 如果负载输入 无法处理此负电压, 这可导致 负载受损。 当首次 应用 VIN 时, 此解决方案还会出现 另一问题。 在系统中,此情况可以是 插入电池 或初始系统启动。 在此期间, 栅极电压为 0 伏。 当应用 VIN 后,栅极至 VOUT 的电容器 使 PMOS 栅极的 充电时间变长。 虽然栅极 仍然在充电, 但是该解决方案 未完全关闭, 并且可见到功率 从 VIN 流至 VOUT, 即使该解决方案 已关闭,也是如此。 如果在系统启动期间 不要求对负载加电, 则不能使用 该解决方案。 现在,我们研究了 PMOS 解决方案, 接下来我们将讨论 NMOS 解决方案。 从交流电角度来看, 规则没变。 需要添加电容 以降满栅极充电速度, 从而可以控制 输出电压。 如不添加, 则输出电压将失控, 并且将产生大 涌浪电流。 从直流电角度来看, 事情对于 NMOS 略有不同。 栅极需要高于 VIN 才能使解决方案启动。 这意味着该解决方案 能够开关较低的输入电压, 而不会有任何问题。 为获得最佳 导通电阻性能, VIN 和栅极 之间的电压差 应是高电压差。 为此, 栅极电压 必须远高于 VIN。 左侧显示了此问题的 两个解决方案。 第一个解决方案使用 充电泵,取 VIN 的值并 从中生成 较高的电压, 这可与栅极上使用。 第二个解决方案 使用多个分立式组件, 并可在系统中 有较高电压轨时 使用。 虽然两个解决方案 均可使用高栅极电压 以最大程度减少导通电阻, 它们占用许多空间 并使用许多组件 才能达成目标。 现在,让我们看一看, 向这些分立式解决方案 添加附加功能 所需的一些 分立式电路。 快速输出 放电,或者说 QOD, 用于拉低开关 解决方案关闭时的 输出电压。 这将保证 负载的电压 拉低至 0 伏 并且该负载 已完全关闭。 要以分立形式达成此目的, 有两种解决方案。 选项 1 是在 输出端添加 旁漏电阻,这将 在解决方案关闭时 使负载放电。 但是,这也会在 解决方案开启时, 通过该电阻提供 漏电路径。 选项 2 使用 逆变器和晶体管。 该解决方案将仅 通过晶体管 在关闭开关时 在输出端放电。 由于在分立式 开关解决方案中 MOSFET 体二极管具有朝向, 从 VIN 至 VOUT 的 电流被阻断。 但是,如果 VOUT 大于 VIN, 则电流能够从 VOUT 流至 VIN。 要实施反向 电流阻断, 必须额外添加两个晶体管, 且将其体二极管 朝相反方向。 该解决方案将在关闭时 阻断两个方向的电流, 但是将使开关的 导通电阻翻倍, 因为两个 MOSFET 为相互串联。 Power Good(电源正常)功能会在 开关解决方案开启 并且输出电压高时 提供 高态有源信号。 此信号可用于 启用其余系统的 下游电路或 活动状态指示。 此功能的 分立式实施 使用所示的 分立式组件, 以在 VOUT 拉高时 生成电源备妥信号。 当此解决方案工作时, 它需要许多组件 并会增加总体 解决方案尺寸。 有关电源开关, 讨论的最后一个解决方案 是负载开关。 通过在启用的引脚上 使用 GPIO 信号 可以控制这个 单片解决方案,且高电平和低电平解决方案均 存在。 对于 PMOS 开关, 开态电阻 通过将 PMOS 门 驱动到地面来优化。 对于 MSOS 开关, 此项同样的优化 是通过使用内部 充电泵生成 高栅极电压实现的。 在顶端部分, 负载开关 与其他 功能集成, 以使开关 更为稳定。 此处唯一优势是 设计灵活性, 因为分立式解决方案 可使用该应用程序需要的 任何 MOSFET, 存在数千 MOSFET 可供选择。 话虽如此, 我们有许多负载开关可用, 有些开关甚至能够 配置为更好地满足 特定应用需要。 查看左侧的 负载开关开启行为, 负载开关 能够控制 输出电压 和电流, 使其能够线性上升。 与先前讨论的 PMOS 解决方案相比, 该解决方案没有任何 负输出电压。 有些负载开关甚至 使用外部电容器 提供可调节的上升时间。 将涌浪电流与失控的 分立式解决方案进行比较, 我们可以见到 涌浪电流低得多, 并且在整个输出 电压斜升过程中保持连续。 需要注意的另一点是, 在将 VIN 首次 应用到 负载开关时, 没有输出电压 或一路穿行至输出端的 输出电压。 第三 PMOS 解决方案 可出现此情况, 因为电容使栅极 充电减慢。 与右侧的 负载开关相比, 该图在左侧展示了 分立解决方案的 二进制记数法。 使用 PMOS-NMOS 电阻器与电容器的 分立式解决方案 好比右侧的 负载开关 TPS22965。 负载开关尺寸小 77% 并使用更少组件。 这意味着挑选和 置入成本已降低 并且系统 PCB 可能会更小, 使得能够 获得更小的外形。 现在,让我们了解一下 将额外特性添加到 负载开关解决方案。 如采用分立式解决方案, 则添加快速输出放电 就需要逆变器 和晶体管。 如采用负载开关, 则已集成 快速输出放电, 在器件已禁用后, 实施内部 电阻接地, 接至输出端。 此外,还有在系统不需要时 就不进行 快速输出放电的 负载开关。 该解决方案 无需配备。 要将反向电流阻断 添加到分立式解决方案, 需要添加额外的 MOSFET。 对于具有反向 电流阻断的负载开关, 无需 额外的组件。 当负载开关 关闭后, 开关将自动 阻断反向电流。 电源正常的 分立式实施 涉及多种 分立式元件 以在 VOUT 高时 生成合适的信号。 如采用负载开关, 则提供了开漏 PG 引脚。 通过使用电阻 拉高引脚, 可生成有源 高 PG 信号。 总而言之, 左侧的电路 显示 电源开关的 分立式实施, 且具有快速输出放电, 反向电流阻断 以及电源正常。 要实施具有所有 这些功能的 负载开关解决方案, 只需带 PG 电阻器的 TPS22953 负载 开关即可。 扼要重述一下,让我们回顾 展示的所有对比 解决方案。 第一个 RMOS 解决方案简单, 仅需一个组件。 但是,此解决方案受到 非理想化导通电阻性能 以及失控开启影响, 导致开关期间的 涌浪电流大。 第二个解决方案 优化了导通电阻性能, 但是,增加了 一个经由其添加的 电阻器接地漏电的路径。 并且,它也未修正 在开关期间出现的 电压斜坡失控 或涌浪电流问题。 第三个解决方案能够控制 电压斜坡和涌浪电流, 但是增加了负输出电压, 并且未能阻断 在 VIN 首次应用到 该解决方案时的 电压和电流。 NMOS 解决方案在交流电方面 需要考虑的事项与 PMOS 解决方案相同, 它还能够在 低输入电压下 提供更佳的性能。 这些解决方案 可能更为复杂, 但是,由于需要将电路 应用到 NMOS 的 高压栅极。 负载开关提供 具有受控的上升时间、 小解决方案尺寸、 优化的导通电阻, 以及多项集成功能的 单片解决方案。 在此幻灯片上列有 要记住的多项关键内容。 首先,电源开关已广泛 应用到各个市场领域 以及多种不同的终端设备上。 要查找原理图上的 分立式电源开关 解决方案, 查找水平 MOSFET。 第二,简单的 分立式解决方案 没有受控的 上升时间 并会产生大量 涌浪电流。 可以添加更多组件 以控制电压斜坡速率, 但是这会增加解决方案尺寸 和 BOM 计数。 最终,可将 负载开关用作 电源开关的 单片解决方案, 并用于在分立式 实施过程中 提供多项改善。 有关负载开关的 更多信息, 请查阅德州仪器 (TI) 提供的其他 一些附加资源。 我们提供了 多项 TI 设计, 以展示可以如何使用负载开关 来解决现实中的终端设备 问题。 此 TI 设计创建了 SSD 电力输送 解决方案,展示了 TPS22954 负载开关的 功能和小尺寸。 可穿戴设备的 发运模式显示了 可如何使用 负载开关 在最终设备仍在置物架上时 就断开电池与系统其余部分的 连接。 这最大程度 减少了终端设备的 电池消耗并增强了客户的 开箱即用体验。 此 TI 设计占空比 周期负载开关 可显示动态 切换负载开关 可如何为最终设备 产生实质性的功率节省。 左侧的 TI 设计显示 并联多个 负载开关 可如何降低 开态电阻, 并提高载流能力。 右侧的 TI 设计显示了 可如何使用 负载开关进行 电源多路复用和反向电流阻断。 德州仪器 (TI) 还 向多种负载开关 提供 WEBENCH 支持, 这能够有助于负载开关的 参数与性能建模。 最后,我们提供了 多份应用手册, 其中 提供了 有关各种不同负载开关的 功能与配置的详细信息。 感谢您抽时间 观看本演示。 有关更多信息和 查看所有资源, 请访问德州仪器 (TI) 负载开关主页, 网址为 www.ti.com/loadswitch。 如有任何问题,请在负载开关 与电源路径 保护 E2E 论坛上 发帖。

本视频的标题为 电源开关解决方案对比 -

分立式 MOSFET 与 集成负载开关。

本次培训中,您将 学习什么是电源开关

解决方案及如何识别 电路图中的分立式 MOSFET

开关解决方案。

在此过程中,我们将从 直流电与交流电角度

分析分立式开关 解决方案的性能。

然后介绍负载 开关解决方案

并将其性能 与 MOSFET 解决

方案进行比较。

接着,让我们 开始介绍。

电源开关 通常指的是

连接和断开 到负载的电源。

电源开关位于 系统电源

与负载之间, 此开关将控制

何时从电源 对负载供电

或不供电。

工程师在其系统中 使用电源开关的

原因是多方面的。

系统启动期间, 如果电源必须同时

对所有系统 负载供电,

供电压力 会较大。

使用电源开关, 这些负载

则可以一次开启一个, 这样可以毫无问题地

启动电源。

电源开关还可以 被用来降低

电源电压 升高的速度。

这会有助于控制 大负载电容

充电过程中产生的 涌浪电流数量。

电源开关的 另一个原因

是减少电力消耗。

在具有功耗意识的 系统中,如使用

电池供电的应用, 电力消耗

是关键问题所在。

为使系统 更有效率,

可将不需要 供电的负载关闭,

不使用时可以 使用电源开关

断开负载 与电源。

对于处理器和 FPGA 应用程序,

需使用电源轨排序 以便正常运行。

电源开关可被用来 对这些电源轨进行排序

并保证正确 启动系统。

哪些市场和终端设备 使用电源开关?

几乎所有都使用。

在个人电子 产品中,

有许多使用电池 供电的应用,

如笔记本电脑、平板电脑 及穿戴式计算机,

它们均采用电源 开关来禁用

未用的子系统。

这样可以降低 系统的电力消耗

并提高电池寿命。

在工业市场中, 移动销售点机器

使用电源开关以节约 电池寿命,而 COM express 模块

使用电源 开关来调节

哪些电压轨 投入使用

及系统是否 处于待机状态。

汽车使用电源 开关以便对应用

处理器和 信息娱乐系统和仪表组应用

进行电力排序。

电源开关还可 用于打开和关闭

汽车照明灯。

在企业市场中, 服务器需要

电源开关来 控制系统启动。

各服务器拥有多个 必须通电的硬驱动。

若要防止 供电压力,

可使用开关同时 打开少数硬驱动。

这样将允许 电源供应

逐渐安全开启。

实现电源开关的 一种方法就是

使用分立式解决方案。

这些解决方案使用 MOSFET 来接通和切断

对某负载的电源。

许多时候,MOSFET 周围设有几个

分立组件, 以帮助控制开关

或添加额外功能。

若要在电路图中 找到其中一个解决方案,

建议搜索 水平绘制的

FET。

许多时候会为系统中 某电源开关应用采用

这些 MOSFET。

我们将查看的第一个 分立式 MOSFET 解决方案

是 PMOS 解决方案。

使用该解决方案的较大 优势就在于它的简单。

仅需一个组件。

通过连接 PMOS 栅极至 GPIO,

GPIO 可以控制 是接通还是切断 PMOS。

但是,这是一种 低电平解决方案,

意味着 GPIO 必须较高

开关才会关闭。

这会是一种弊端, 因为需要先接通

系统电源,然后才会将电源 从 VIN 拦截到 VOUT。

该解决方案中的 另一个弊端是 GPIO 变化。

至于该解决方案的 最佳性能,

当开关打开时, MOSFET 从 VIN

到 VOUT 的导通电阻 或电阻应非常低。

这导致给定负载 电流情况下,

VIN 落到 VOUT的 电压最低。

若要最大程度 减少导通电阻,

电源与 PMOS 栅极间的 电压差必须较高。

因此,该解决 方案的最佳性能

是将栅极拉至 0 伏特时。

如果 GPIO 信号 出现变化,

那么数字低输出 会更接近

更接近 200 或 300 毫伏,

导致解决方案 性能不理想。

这也会使该解决 方案很难使用

较低电压。 VIN 不能低于 MOSFET 的

通电阈值。

所以,如果电压 低于该阈值,

它会阻止 系统通电。

对于下列 范围截屏,每个轨迹

均贴有标签 并对右图

进行颜色编码。

从顶部开始,我们 拥有 ON 引脚电压、

VIN 电压、 VOUT 电压

及流过 FET 的电流。

对于本例, VOUT 电容

为 4.7 微法拉。

范围截屏显示 ON 引脚从高走向低。

因此低电平解决方案 从切断改为接通。

VOUT 电压 如预期般升高。

但我们发现,VIN 电压 降低,电流高峰

大约为 2.2 安培。

这是因为 开关接通时,

电压升温速率 失控并在几纳秒内

升高。

这种快速通电 会导致电容

快速充电。

根据方程式 I = C/dt,

这会导致 涌浪电流较大。

在这种情况下, 仅需 4.7 微法拉

即可产生 2 安培 以上涌浪电流。

因此,电源供应 无法处理负载,

必须降低电压进行补偿。

该涌浪电流会导致 意外的系统性能,

如外接口或 PCB 轨迹重置

或损坏。

第二种解决方案增加了 电阻和 NMOS 晶体管。

通过控制 NMOS 晶体管栅极,

本解决方案 变为高电平,

意味着电压高时 可以接通系统,

电压低时可以 切断系统。

而且,NMOS 可以 将 PMOS 栅极

拉至 0 伏特状态, 这样可以优化

该解决方案的 导通电阻性能。

但是,较低 电压仍然

不能用于 该解决方案。

当解决方案接通时, 增加电阻器

会增加其 漏电路径。

电阻越低, 漏电量越高。

电阻越高, 漏电量越低。

从交流电角度来看, 变化不大。

解决方案仍然不能 控制输出电压

升高的速率。

输出电容 再次导致

大涌浪电流。

我们将查看的最后一个 PMOS 解决方案

增加了一个附加电容器, 并对涌浪电流有所帮助。

从直流电角度来看, 没有任何变化。

高电平解决 方案仍然可以

优化导通 电阻性能,

当解决方案 通电时

放电路径仍然存在。

使用此解决方案,电压 斜坡率会得到控制。

通过增加栅极与 VOUT 之间的电容,

电压上升时间 可能会增长,

这会使 涌浪电流降低。

例如,电容为 47 微法拉时,

电压上升 时间大约

为 150 微秒 且涌浪电流

由 2 安培 降至 200 毫安。

电容较高时, 涌浪电流

甚至降低更多。

请记住, 如果通电时间

增加,断电 时间也会增加,

这意味着解决方案 如需要缓慢通电

和快速断电时间 则不能正常运行。

左侧显示的范围 表明本解决方案

通电并连接 3 安培负载,

我们可以看到, 电压和电流

均受控。

虽然此解决方案 能够提供

电压和电流 均适用的线性斜坡,

但是观察到一项异常。

在首次开启 解决方案时,

负电压和 负电流均会出现。

这是开机时 电容的

预充方式造成的。

在此期间, PMOS 的栅极较高,

且 VOUT 为 0 伏。

电容器将 充电至 VIN 值,

如图所示。

当此解决方案开启后, PMOS 栅极变低,

并且电容 会通过 NMOS

放电至接地。

在该解决方案 有时间完全开启前,

此放电将 VOUT 下拉。

虽然较高的电阻能够 有助于降低涌浪电流,

它还会为 该解决方案

产生更多的负电压和电流。

在 47 微法拉条件下, 在 VOUT 观察到负 1 伏。

如果负载输入 无法处理此负电压,

这可导致 负载受损。

当首次 应用 VIN 时,

此解决方案还会出现 另一问题。

在系统中,此情况可以是 插入电池

或初始系统启动。

在此期间, 栅极电压为 0 伏。

当应用 VIN 后,栅极至 VOUT 的电容器

使 PMOS 栅极的 充电时间变长。

虽然栅极 仍然在充电,

但是该解决方案 未完全关闭,

并且可见到功率 从 VIN 流至 VOUT,

即使该解决方案 已关闭,也是如此。

如果在系统启动期间 不要求对负载加电,

则不能使用 该解决方案。

现在,我们研究了 PMOS 解决方案,

接下来我们将讨论 NMOS 解决方案。

从交流电角度来看, 规则没变。

需要添加电容 以降满栅极充电速度,

从而可以控制 输出电压。

如不添加, 则输出电压将失控,

并且将产生大 涌浪电流。

从直流电角度来看, 事情对于

NMOS 略有不同。

栅极需要高于 VIN 才能使解决方案启动。

这意味着该解决方案 能够开关较低的输入电压,

而不会有任何问题。

为获得最佳 导通电阻性能,

VIN 和栅极 之间的电压差

应是高电压差。

为此, 栅极电压

必须远高于 VIN。

左侧显示了此问题的 两个解决方案。

第一个解决方案使用 充电泵,取 VIN 的值并

从中生成 较高的电压,

这可与栅极上使用。

第二个解决方案 使用多个分立式组件,

并可在系统中 有较高电压轨时

使用。

虽然两个解决方案 均可使用高栅极电压

以最大程度减少导通电阻, 它们占用许多空间

并使用许多组件 才能达成目标。

现在,让我们看一看, 向这些分立式解决方案

添加附加功能 所需的一些

分立式电路。

快速输出 放电,或者说 QOD,

用于拉低开关 解决方案关闭时的

输出电压。

这将保证 负载的电压

拉低至 0 伏 并且该负载

已完全关闭。

要以分立形式达成此目的, 有两种解决方案。

选项 1 是在 输出端添加

旁漏电阻,这将 在解决方案关闭时

使负载放电。

但是,这也会在 解决方案开启时,

通过该电阻提供 漏电路径。

选项 2 使用 逆变器和晶体管。

该解决方案将仅 通过晶体管

在关闭开关时 在输出端放电。

由于在分立式 开关解决方案中

MOSFET 体二极管具有朝向,

从 VIN 至 VOUT 的 电流被阻断。

但是,如果 VOUT 大于 VIN,

则电流能够从 VOUT 流至 VIN。

要实施反向 电流阻断,

必须额外添加两个晶体管, 且将其体二极管

朝相反方向。

该解决方案将在关闭时 阻断两个方向的电流,

但是将使开关的 导通电阻翻倍,

因为两个 MOSFET 为相互串联。

Power Good(电源正常)功能会在 开关解决方案开启

并且输出电压高时 提供

高态有源信号。

此信号可用于 启用其余系统的

下游电路或 活动状态指示。

此功能的 分立式实施

使用所示的 分立式组件,

以在 VOUT 拉高时

生成电源备妥信号。

当此解决方案工作时, 它需要许多组件

并会增加总体 解决方案尺寸。

有关电源开关, 讨论的最后一个解决方案

是负载开关。

通过在启用的引脚上 使用 GPIO 信号

可以控制这个 单片解决方案,且高电平和低电平解决方案均

存在。

对于 PMOS 开关, 开态电阻

通过将 PMOS 门 驱动到地面来优化。

对于 MSOS 开关, 此项同样的优化

是通过使用内部 充电泵生成

高栅极电压实现的。

在顶端部分, 负载开关

与其他 功能集成,

以使开关 更为稳定。

此处唯一优势是 设计灵活性,

因为分立式解决方案 可使用该应用程序需要的

任何 MOSFET, 存在数千 MOSFET

可供选择。

话虽如此, 我们有许多负载开关可用,

有些开关甚至能够 配置为更好地满足

特定应用需要。

查看左侧的 负载开关开启行为,

负载开关 能够控制

输出电压 和电流,

使其能够线性上升。

与先前讨论的 PMOS 解决方案相比,

该解决方案没有任何 负输出电压。

有些负载开关甚至 使用外部电容器

提供可调节的上升时间。

将涌浪电流与失控的 分立式解决方案进行比较,

我们可以见到 涌浪电流低得多,

并且在整个输出 电压斜升过程中保持连续。

需要注意的另一点是, 在将 VIN 首次

应用到 负载开关时,

没有输出电压 或一路穿行至输出端的

输出电压。

第三 PMOS 解决方案 可出现此情况,

因为电容使栅极 充电减慢。

与右侧的 负载开关相比,

该图在左侧展示了 分立解决方案的

二进制记数法。

使用 PMOS-NMOS 电阻器与电容器的

分立式解决方案 好比右侧的

负载开关 TPS22965。

负载开关尺寸小 77% 并使用更少组件。

这意味着挑选和 置入成本已降低

并且系统 PCB 可能会更小,

使得能够 获得更小的外形。

现在,让我们了解一下 将额外特性添加到

负载开关解决方案。

如采用分立式解决方案, 则添加快速输出放电

就需要逆变器 和晶体管。

如采用负载开关, 则已集成

快速输出放电, 在器件已禁用后,

实施内部 电阻接地,

接至输出端。

此外,还有在系统不需要时 就不进行

快速输出放电的 负载开关。

该解决方案 无需配备。

要将反向电流阻断 添加到分立式解决方案,

需要添加额外的 MOSFET。

对于具有反向 电流阻断的负载开关,

无需 额外的组件。

当负载开关 关闭后,

开关将自动 阻断反向电流。

电源正常的 分立式实施

涉及多种 分立式元件

以在 VOUT 高时 生成合适的信号。

如采用负载开关, 则提供了开漏 PG 引脚。

通过使用电阻 拉高引脚,

可生成有源 高 PG 信号。

总而言之, 左侧的电路

显示 电源开关的

分立式实施, 且具有快速输出放电,

反向电流阻断 以及电源正常。

要实施具有所有 这些功能的

负载开关解决方案, 只需带 PG 电阻器的

TPS22953 负载 开关即可。

扼要重述一下,让我们回顾 展示的所有对比

解决方案。

第一个 RMOS 解决方案简单,

仅需一个组件。

但是,此解决方案受到 非理想化导通电阻性能

以及失控开启影响,

导致开关期间的 涌浪电流大。

第二个解决方案 优化了导通电阻性能,

但是,增加了 一个经由其添加的

电阻器接地漏电的路径。

并且,它也未修正 在开关期间出现的

电压斜坡失控 或涌浪电流问题。

第三个解决方案能够控制 电压斜坡和涌浪电流,

但是增加了负输出电压, 并且未能阻断

在 VIN 首次应用到 该解决方案时的

电压和电流。

NMOS 解决方案在交流电方面 需要考虑的事项与 PMOS 解决方案相同,

它还能够在 低输入电压下

提供更佳的性能。

这些解决方案 可能更为复杂,

但是,由于需要将电路 应用到 NMOS 的

高压栅极。

负载开关提供 具有受控的上升时间、

小解决方案尺寸、 优化的导通电阻,

以及多项集成功能的 单片解决方案。

在此幻灯片上列有 要记住的多项关键内容。

首先,电源开关已广泛 应用到各个市场领域

以及多种不同的终端设备上。

要查找原理图上的 分立式电源开关

解决方案, 查找水平 MOSFET。

第二,简单的 分立式解决方案

没有受控的 上升时间

并会产生大量 涌浪电流。

可以添加更多组件 以控制电压斜坡速率,

但是这会增加解决方案尺寸 和 BOM 计数。

最终,可将 负载开关用作

电源开关的 单片解决方案,

并用于在分立式 实施过程中

提供多项改善。

有关负载开关的 更多信息,

请查阅德州仪器 (TI) 提供的其他

一些附加资源。

我们提供了 多项 TI 设计,

以展示可以如何使用负载开关 来解决现实中的终端设备

问题。

此 TI 设计创建了 SSD 电力输送

解决方案,展示了 TPS22954 负载开关的

功能和小尺寸。

可穿戴设备的 发运模式显示了

可如何使用 负载开关

在最终设备仍在置物架上时 就断开电池与系统其余部分的

连接。

这最大程度 减少了终端设备的

电池消耗并增强了客户的 开箱即用体验。

此 TI 设计占空比 周期负载开关

可显示动态 切换负载开关

可如何为最终设备 产生实质性的功率节省。

左侧的 TI 设计显示

并联多个 负载开关

可如何降低 开态电阻,

并提高载流能力。

右侧的 TI 设计显示了

可如何使用 负载开关进行

电源多路复用和反向电流阻断。

德州仪器 (TI) 还 向多种负载开关

提供 WEBENCH 支持, 这能够有助于负载开关的

参数与性能建模。

最后,我们提供了 多份应用手册,

其中 提供了

有关各种不同负载开关的 功能与配置的详细信息。

感谢您抽时间 观看本演示。

有关更多信息和 查看所有资源,

请访问德州仪器 (TI) 负载开关主页,

网址为 www.ti.com/loadswitch。

如有任何问题,请在负载开关 与电源路径

保护 E2E 论坛上 发帖。

手机看

扫码用手机观看

-

未学习 如何以及为什么用负载开关替换分立MOSFET

未学习 如何以及为什么用负载开关替换分立MOSFET

00:21:51

播放中

视频简介

视频简介

如何以及为什么用负载开关替换分立MOSFET

所属课程:如何以及为什么用负载开关替换分立MOSFET

发布时间:2019.03.11

视频集数:1

本节视频时长:00:21:51

“你将学到什么:

如何在原理图中识别分立功率开关解决方案

使用分立解决方案的挑战

负载开关如何为功率开关提供更好的性能,具有更多功能和更小的解决方案尺寸“