CC2640R2F硬件射频从设计到成型之二-CC2640R2F原理图及器件选型

播放器加载失败: 未检测到Flash Player,请到

安装

将在30s后自动为您播放下一课程

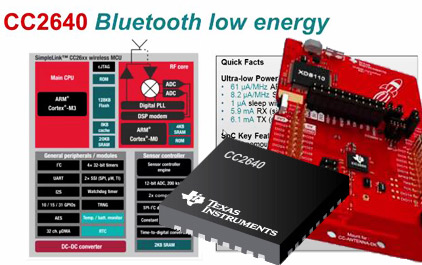

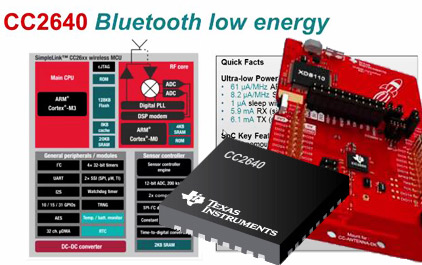

欢迎回来 我是张希伟 我们来继续介绍一下CC2640以及CC2640R2F 它的硬件射频方面的一些相关知识 首先在这个章节当中 会给大家介绍一下原理图方面的一些相关知识和 会介绍一些原理图的各个部分和功能 以及器械选型方面 需要注意的一些东西 以及射频前端 怎么样去选 好 首先我们看一下这张原理图 这张原理图 我是拿了一个TI的CC2640 5X5的一个设计 给大家大概介绍一下 首先对于TI的芯片4X4 5X5 7X7来说 对于IO口的数量是不同的 但是其他的一些设计 比如说电源 射频前端 晶振方面 还有debug接口 等等 这些方面都是一模一样的 所以大家在设计的时候 可以互相抄袭一下 就是IO口的数量不同而已 就这么一个变化 对于原理图来说 比方我们来看一下这张图 它是5X5的设计 5X5的设计 射频前端是叉分的 外部偏置的设计 比如说你在看4X4的时候 可能我们只提供了 4X4的单端这么一个设计 其实很简单 你可以直接把5X5的差分设计 拷贝到4X4的设计里面就可以了 就是这样的一些方法 接下来我会带大家 从各模块做一个剖析和介绍 首先我们来看电源部分的设计 这个就是最标准的(听不清)工作范围的设计 它的电压工作范围是从1.8-3.8伏 这个电压范围也非常好 非常适合两节五号电池 供电 它基本可以让两节5号电池把它的电池放到100% 放光 因为它最低支持的工作电压是1.8伏 外围电路是非常标准的 DC-DC外围电路 就是大电杆加电容的架构 包括输入部分也有大电容来支持DC-DC的正常工作 最后这个部分DC-DC电路会送出一个电压 叫 VDDR R应该是regulatory的意思 它再去送到我们芯片内部来工作 大家在做器械选型的时候 一定要记得 这个10(听不清) 对于电感和电容来说非常非常重要 它是整个电路中非常重要的器件 如果器件不满足 我们所要求的指标的话 就比如说电流 包括它在额定电流下的感量或电容量的话 这个芯片可能面临频繁进到掉电重启的状态 大家在选型的时候需要注意到这些点 然后我们看一下另外一种供电方式 叫external regulator mode 就是VDDR直接给它供电 相当于我们把DC-DC bypass掉了 直接给它供一个1.8伏的电压 它的范围是1.7到1.9伏 其实这个应用也非常广泛 比如说大家整个的系统电压 就是1.8伏 比如说你和你的modem做一个手表 这样的话 你可以直接用这种模式 它所有的IO口都是1.8伏 这样它可以让你节省一些电频转换的工作 如果大家用这种模式 TI有一些相关的电源推荐 这种高效的TPS62740 它可以支持不同模式 好我们看一下VDDR 其实整个电源链的架构就是这样 我们在系统里有一个DC-DC 包括跟它并行地我们还有一个global LDO 它们最后输出的电压叫VDDR 就是我们拐角上看到这个电压 然后再经过内部一系列电源链的分 分别分发给各个模块的系统来工作 我来介绍这张图主要的意思呢 这个VDDR是非常非常重要的 如果大家在debug的时候 可以测试一下VDDR 另外 系统是由global LDO 和DC-DC 来供电的 它俩是或者的关系 就说你可以选DC-DC模式 也可以选global LDO模式 当然 DC-DC 可以给你更好的效率 好我们来看一下设计里另一个重要的部分 就是clock部分 clock部分一般分为两种clock 第一部分是fast clock fast clock主要是支持在芯片active模式下 以及射频电路上面的参考时钟 所以时钟对射频指标的影响 非常非常大 关于具体的crystal设计的guideline 和器件选型 大家可以参照这篇文档 这里面我给大家提一下的就是咱们的负载电容 和 等效串联电阻这些值 一定要满足咱们的设计需求 因为这些负载电容值和ESR 会直接影响到咱们 crystal的机身条件 如果机身条件不好的话 这个芯片有可能面临停 (听不清) 然后slow clock主要是在维持芯片在启动 或者在低功耗模式下 它的一些时钟的管理 比如我们可以外接一个32khz的crystal 另外最主要的 我们在最新地芯片上可以节省外部的RC电路 它可以达到一些响应的指标 具体地我们可以参考一下这篇文档 它在不同地状态下会省点或者会更费电 或者怎么样 好我们来看一下debug电路 debug电路这块芯片支持jtag 在我们TI主要提供几种这样的仿真器 一个是XDS100V3这个在我们的smart F001B上用的就是这 个仿真器 另外就是XDS110 这个是在我们的launchpad上面应用到的一个仿真器 同时也是支持其他一些市面上 比较流行的jtag仿真器 好 我们来看一下射频部分 射频在我们的参考设计里 一般都会设成两个射频的 端口 一个是SMA的connector 这种SMA的连接器 或者其他类型的连接器 它的主要作用就是 让我们来测试和评估 它的射频指标 另外就是还有一个板载天线 板载天线在我们的launchpad上面 就是那种倒F的天线 就是(听不清)天线 上面设计我们一般设计了一个(听不清)的流用电阻 当你朝这边焊接的时候 你是来测试它的射频指标 朝这边焊接的时候 你是来调软件 然后用一些板载天线做一些测试 这一部分 R12和C15 我们是预留 用来调试天线的匹配的 好 射频口主要有三个端口 一个是RFP和RFN 就是叉分的RF端口 等一会儿可以给大家介绍 射频可以非常灵活地配置 不但支持叉分 还支持单端 另外还有RX-TX 这样的bias拐角 它主要是给内部的(听不清)做bias用的 会影响接收器灵敏度的一些指标 这张slice主要给大家介绍一下射频前端不同的选项 我们可以看到这里面有四个象限 横坐标我们可以看 这里面有差分的区别 和单端的射频前端的区别 纵坐标我们可以看一下 有internal bias和external bias的区别 internal bias和external bias的区别主要是看RX-TX拐角有没有用于 我们内部RNA的馈电 differential和single-ended设计主要是看我们射频前端 是用了差分的设计还是单端的设计 这样的一些区别 我们可以看到 差分的射频前端的设计 加上 external bias 它拥有最高的发射功率 和最好的接收机灵敏度的指标 但是它的器件也是非常多的 也是最多的一个 另外期间最少的 最大发射器和接收机灵敏度最差的设计 是在这里 它只需要四个器件 但是它最大的发射功率是2DBM 接收机的灵敏度大概在BLE模式下 会比我们的EXTERNAL BIAS 差分要低3DB 是这样的一个设计 但是它的尺寸和 器件数量都是最少的 所以大家如果对于cost 或者 设计尺寸要求非常非常苛刻的话 我是建议大家用差分的方式来做 另外大家可以看一下 在另外两个象限 我们提供了折中的方案 大家可以根据自己的设计进行选择 好 这个是总的参考表 我们可以看到 对于不同的 射频前端的选项 我们会得到不同地射频指标 比如说 我们想要最大的电路预算 我们可以选择差分的EXTERNAL BIAS的设计 如果我们要最小的尺寸 我们可以选择INTERNAL BIAS加SINGLE ENDED这样 的一个设计 好 谢谢大家 这个就是原理图部分的介绍

欢迎回来 我是张希伟 我们来继续介绍一下CC2640以及CC2640R2F 它的硬件射频方面的一些相关知识 首先在这个章节当中 会给大家介绍一下原理图方面的一些相关知识和 会介绍一些原理图的各个部分和功能 以及器械选型方面 需要注意的一些东西 以及射频前端 怎么样去选 好 首先我们看一下这张原理图 这张原理图 我是拿了一个TI的CC2640 5X5的一个设计 给大家大概介绍一下 首先对于TI的芯片4X4 5X5 7X7来说 对于IO口的数量是不同的 但是其他的一些设计 比如说电源 射频前端 晶振方面 还有debug接口 等等 这些方面都是一模一样的 所以大家在设计的时候 可以互相抄袭一下 就是IO口的数量不同而已 就这么一个变化 对于原理图来说 比方我们来看一下这张图 它是5X5的设计 5X5的设计 射频前端是叉分的 外部偏置的设计 比如说你在看4X4的时候 可能我们只提供了 4X4的单端这么一个设计 其实很简单 你可以直接把5X5的差分设计 拷贝到4X4的设计里面就可以了 就是这样的一些方法 接下来我会带大家 从各模块做一个剖析和介绍 首先我们来看电源部分的设计 这个就是最标准的(听不清)工作范围的设计 它的电压工作范围是从1.8-3.8伏 这个电压范围也非常好 非常适合两节五号电池 供电 它基本可以让两节5号电池把它的电池放到100% 放光 因为它最低支持的工作电压是1.8伏 外围电路是非常标准的 DC-DC外围电路 就是大电杆加电容的架构 包括输入部分也有大电容来支持DC-DC的正常工作 最后这个部分DC-DC电路会送出一个电压 叫 VDDR R应该是regulatory的意思 它再去送到我们芯片内部来工作 大家在做器械选型的时候 一定要记得 这个10(听不清) 对于电感和电容来说非常非常重要 它是整个电路中非常重要的器件 如果器件不满足 我们所要求的指标的话 就比如说电流 包括它在额定电流下的感量或电容量的话 这个芯片可能面临频繁进到掉电重启的状态 大家在选型的时候需要注意到这些点 然后我们看一下另外一种供电方式 叫external regulator mode 就是VDDR直接给它供电 相当于我们把DC-DC bypass掉了 直接给它供一个1.8伏的电压 它的范围是1.7到1.9伏 其实这个应用也非常广泛 比如说大家整个的系统电压 就是1.8伏 比如说你和你的modem做一个手表 这样的话 你可以直接用这种模式 它所有的IO口都是1.8伏 这样它可以让你节省一些电频转换的工作 如果大家用这种模式 TI有一些相关的电源推荐 这种高效的TPS62740 它可以支持不同模式 好我们看一下VDDR 其实整个电源链的架构就是这样 我们在系统里有一个DC-DC 包括跟它并行地我们还有一个global LDO 它们最后输出的电压叫VDDR 就是我们拐角上看到这个电压 然后再经过内部一系列电源链的分 分别分发给各个模块的系统来工作 我来介绍这张图主要的意思呢 这个VDDR是非常非常重要的 如果大家在debug的时候 可以测试一下VDDR 另外 系统是由global LDO 和DC-DC 来供电的 它俩是或者的关系 就说你可以选DC-DC模式 也可以选global LDO模式 当然 DC-DC 可以给你更好的效率 好我们来看一下设计里另一个重要的部分 就是clock部分 clock部分一般分为两种clock 第一部分是fast clock fast clock主要是支持在芯片active模式下 以及射频电路上面的参考时钟 所以时钟对射频指标的影响 非常非常大 关于具体的crystal设计的guideline 和器件选型 大家可以参照这篇文档 这里面我给大家提一下的就是咱们的负载电容 和 等效串联电阻这些值 一定要满足咱们的设计需求 因为这些负载电容值和ESR 会直接影响到咱们 crystal的机身条件 如果机身条件不好的话 这个芯片有可能面临停 (听不清) 然后slow clock主要是在维持芯片在启动 或者在低功耗模式下 它的一些时钟的管理 比如我们可以外接一个32khz的crystal 另外最主要的 我们在最新地芯片上可以节省外部的RC电路 它可以达到一些响应的指标 具体地我们可以参考一下这篇文档 它在不同地状态下会省点或者会更费电 或者怎么样 好我们来看一下debug电路 debug电路这块芯片支持jtag 在我们TI主要提供几种这样的仿真器 一个是XDS100V3这个在我们的smart F001B上用的就是这 个仿真器 另外就是XDS110 这个是在我们的launchpad上面应用到的一个仿真器 同时也是支持其他一些市面上 比较流行的jtag仿真器 好 我们来看一下射频部分 射频在我们的参考设计里 一般都会设成两个射频的 端口 一个是SMA的connector 这种SMA的连接器 或者其他类型的连接器 它的主要作用就是 让我们来测试和评估 它的射频指标 另外就是还有一个板载天线 板载天线在我们的launchpad上面 就是那种倒F的天线 就是(听不清)天线 上面设计我们一般设计了一个(听不清)的流用电阻 当你朝这边焊接的时候 你是来测试它的射频指标 朝这边焊接的时候 你是来调软件 然后用一些板载天线做一些测试 这一部分 R12和C15 我们是预留 用来调试天线的匹配的 好 射频口主要有三个端口 一个是RFP和RFN 就是叉分的RF端口 等一会儿可以给大家介绍 射频可以非常灵活地配置 不但支持叉分 还支持单端 另外还有RX-TX 这样的bias拐角 它主要是给内部的(听不清)做bias用的 会影响接收器灵敏度的一些指标 这张slice主要给大家介绍一下射频前端不同的选项 我们可以看到这里面有四个象限 横坐标我们可以看 这里面有差分的区别 和单端的射频前端的区别 纵坐标我们可以看一下 有internal bias和external bias的区别 internal bias和external bias的区别主要是看RX-TX拐角有没有用于 我们内部RNA的馈电 differential和single-ended设计主要是看我们射频前端 是用了差分的设计还是单端的设计 这样的一些区别 我们可以看到 差分的射频前端的设计 加上 external bias 它拥有最高的发射功率 和最好的接收机灵敏度的指标 但是它的器件也是非常多的 也是最多的一个 另外期间最少的 最大发射器和接收机灵敏度最差的设计 是在这里 它只需要四个器件 但是它最大的发射功率是2DBM 接收机的灵敏度大概在BLE模式下 会比我们的EXTERNAL BIAS 差分要低3DB 是这样的一个设计 但是它的尺寸和 器件数量都是最少的 所以大家如果对于cost 或者 设计尺寸要求非常非常苛刻的话 我是建议大家用差分的方式来做 另外大家可以看一下 在另外两个象限 我们提供了折中的方案 大家可以根据自己的设计进行选择 好 这个是总的参考表 我们可以看到 对于不同的 射频前端的选项 我们会得到不同地射频指标 比如说 我们想要最大的电路预算 我们可以选择差分的EXTERNAL BIAS的设计 如果我们要最小的尺寸 我们可以选择INTERNAL BIAS加SINGLE ENDED这样 的一个设计 好 谢谢大家 这个就是原理图部分的介绍

欢迎回来 我是张希伟

我们来继续介绍一下CC2640以及CC2640R2F

它的硬件射频方面的一些相关知识

首先在这个章节当中 会给大家介绍一下原理图方面的一些相关知识和

会介绍一些原理图的各个部分和功能

以及器械选型方面 需要注意的一些东西

以及射频前端 怎么样去选

好 首先我们看一下这张原理图

这张原理图 我是拿了一个TI的CC2640

5X5的一个设计

给大家大概介绍一下

首先对于TI的芯片4X4 5X5 7X7来说

对于IO口的数量是不同的

但是其他的一些设计 比如说电源

射频前端 晶振方面 还有debug接口

等等 这些方面都是一模一样的 所以大家在设计的时候

可以互相抄袭一下

就是IO口的数量不同而已

就这么一个变化 对于原理图来说

比方我们来看一下这张图 它是5X5的设计

5X5的设计 射频前端是叉分的 外部偏置的设计

比如说你在看4X4的时候

可能我们只提供了 4X4的单端这么一个设计

其实很简单 你可以直接把5X5的差分设计

拷贝到4X4的设计里面就可以了

就是这样的一些方法

接下来我会带大家 从各模块做一个剖析和介绍

首先我们来看电源部分的设计

这个就是最标准的(听不清)工作范围的设计

它的电压工作范围是从1.8-3.8伏

这个电压范围也非常好 非常适合两节五号电池

供电 它基本可以让两节5号电池把它的电池放到100% 放光

因为它最低支持的工作电压是1.8伏

外围电路是非常标准的 DC-DC外围电路

就是大电杆加电容的架构

包括输入部分也有大电容来支持DC-DC的正常工作

最后这个部分DC-DC电路会送出一个电压 叫

VDDR R应该是regulatory的意思

它再去送到我们芯片内部来工作

大家在做器械选型的时候 一定要记得 这个10(听不清)

对于电感和电容来说非常非常重要

它是整个电路中非常重要的器件 如果器件不满足

我们所要求的指标的话 就比如说电流

包括它在额定电流下的感量或电容量的话

这个芯片可能面临频繁进到掉电重启的状态

大家在选型的时候需要注意到这些点

然后我们看一下另外一种供电方式

叫external regulator mode

就是VDDR直接给它供电 相当于我们把DC-DC bypass掉了

直接给它供一个1.8伏的电压

它的范围是1.7到1.9伏

其实这个应用也非常广泛

比如说大家整个的系统电压

就是1.8伏 比如说你和你的modem做一个手表

这样的话 你可以直接用这种模式 它所有的IO口都是1.8伏

这样它可以让你节省一些电频转换的工作

如果大家用这种模式 TI有一些相关的电源推荐

这种高效的TPS62740 它可以支持不同模式

好我们看一下VDDR 其实整个电源链的架构就是这样

我们在系统里有一个DC-DC

包括跟它并行地我们还有一个global LDO

它们最后输出的电压叫VDDR 就是我们拐角上看到这个电压

然后再经过内部一系列电源链的分 分别分发给各个模块的系统来工作

我来介绍这张图主要的意思呢 这个VDDR是非常非常重要的

如果大家在debug的时候

可以测试一下VDDR 另外 系统是由global LDO 和DC-DC

来供电的 它俩是或者的关系 就说你可以选DC-DC模式

也可以选global LDO模式 当然 DC-DC 可以给你更好的效率

好我们来看一下设计里另一个重要的部分

就是clock部分

clock部分一般分为两种clock 第一部分是fast clock

fast clock主要是支持在芯片active模式下 以及射频电路上面的参考时钟

所以时钟对射频指标的影响 非常非常大

关于具体的crystal设计的guideline

和器件选型 大家可以参照这篇文档

这里面我给大家提一下的就是咱们的负载电容 和

等效串联电阻这些值 一定要满足咱们的设计需求

因为这些负载电容值和ESR 会直接影响到咱们

crystal的机身条件

如果机身条件不好的话 这个芯片有可能面临停 (听不清)

然后slow clock主要是在维持芯片在启动 或者在低功耗模式下

它的一些时钟的管理 比如我们可以外接一个32khz的crystal

另外最主要的 我们在最新地芯片上可以节省外部的RC电路

它可以达到一些响应的指标

具体地我们可以参考一下这篇文档

它在不同地状态下会省点或者会更费电

或者怎么样

好我们来看一下debug电路 debug电路这块芯片支持jtag

在我们TI主要提供几种这样的仿真器

一个是XDS100V3这个在我们的smart F001B上用的就是这

个仿真器 另外就是XDS110

这个是在我们的launchpad上面应用到的一个仿真器

同时也是支持其他一些市面上 比较流行的jtag仿真器

好 我们来看一下射频部分

射频在我们的参考设计里 一般都会设成两个射频的

端口 一个是SMA的connector 这种SMA的连接器

或者其他类型的连接器 它的主要作用就是

让我们来测试和评估

它的射频指标 另外就是还有一个板载天线

板载天线在我们的launchpad上面 就是那种倒F的天线

就是(听不清)天线

上面设计我们一般设计了一个(听不清)的流用电阻

当你朝这边焊接的时候 你是来测试它的射频指标

朝这边焊接的时候 你是来调软件

然后用一些板载天线做一些测试

这一部分 R12和C15

我们是预留 用来调试天线的匹配的

好 射频口主要有三个端口

一个是RFP和RFN 就是叉分的RF端口

等一会儿可以给大家介绍 射频可以非常灵活地配置

不但支持叉分 还支持单端

另外还有RX-TX 这样的bias拐角

它主要是给内部的(听不清)做bias用的

会影响接收器灵敏度的一些指标

这张slice主要给大家介绍一下射频前端不同的选项

我们可以看到这里面有四个象限

横坐标我们可以看 这里面有差分的区别

和单端的射频前端的区别

纵坐标我们可以看一下 有internal bias和external bias的区别

internal bias和external bias的区别主要是看RX-TX拐角有没有用于

我们内部RNA的馈电

differential和single-ended设计主要是看我们射频前端

是用了差分的设计还是单端的设计 这样的一些区别

我们可以看到 差分的射频前端的设计 加上 external bias

它拥有最高的发射功率

和最好的接收机灵敏度的指标

但是它的器件也是非常多的 也是最多的一个

另外期间最少的 最大发射器和接收机灵敏度最差的设计

是在这里 它只需要四个器件

但是它最大的发射功率是2DBM

接收机的灵敏度大概在BLE模式下 会比我们的EXTERNAL BIAS

差分要低3DB

是这样的一个设计 但是它的尺寸和

器件数量都是最少的 所以大家如果对于cost 或者

设计尺寸要求非常非常苛刻的话

我是建议大家用差分的方式来做

另外大家可以看一下 在另外两个象限 我们提供了折中的方案

大家可以根据自己的设计进行选择

好 这个是总的参考表 我们可以看到

对于不同的 射频前端的选项

我们会得到不同地射频指标

比如说 我们想要最大的电路预算

我们可以选择差分的EXTERNAL BIAS的设计

如果我们要最小的尺寸 我们可以选择INTERNAL BIAS加SINGLE ENDED这样

的一个设计

好 谢谢大家 这个就是原理图部分的介绍

欢迎回来 我是张希伟 我们来继续介绍一下CC2640以及CC2640R2F 它的硬件射频方面的一些相关知识 首先在这个章节当中 会给大家介绍一下原理图方面的一些相关知识和 会介绍一些原理图的各个部分和功能 以及器械选型方面 需要注意的一些东西 以及射频前端 怎么样去选 好 首先我们看一下这张原理图 这张原理图 我是拿了一个TI的CC2640 5X5的一个设计 给大家大概介绍一下 首先对于TI的芯片4X4 5X5 7X7来说 对于IO口的数量是不同的 但是其他的一些设计 比如说电源 射频前端 晶振方面 还有debug接口 等等 这些方面都是一模一样的 所以大家在设计的时候 可以互相抄袭一下 就是IO口的数量不同而已 就这么一个变化 对于原理图来说 比方我们来看一下这张图 它是5X5的设计 5X5的设计 射频前端是叉分的 外部偏置的设计 比如说你在看4X4的时候 可能我们只提供了 4X4的单端这么一个设计 其实很简单 你可以直接把5X5的差分设计 拷贝到4X4的设计里面就可以了 就是这样的一些方法 接下来我会带大家 从各模块做一个剖析和介绍 首先我们来看电源部分的设计 这个就是最标准的(听不清)工作范围的设计 它的电压工作范围是从1.8-3.8伏 这个电压范围也非常好 非常适合两节五号电池 供电 它基本可以让两节5号电池把它的电池放到100% 放光 因为它最低支持的工作电压是1.8伏 外围电路是非常标准的 DC-DC外围电路 就是大电杆加电容的架构 包括输入部分也有大电容来支持DC-DC的正常工作 最后这个部分DC-DC电路会送出一个电压 叫 VDDR R应该是regulatory的意思 它再去送到我们芯片内部来工作 大家在做器械选型的时候 一定要记得 这个10(听不清) 对于电感和电容来说非常非常重要 它是整个电路中非常重要的器件 如果器件不满足 我们所要求的指标的话 就比如说电流 包括它在额定电流下的感量或电容量的话 这个芯片可能面临频繁进到掉电重启的状态 大家在选型的时候需要注意到这些点 然后我们看一下另外一种供电方式 叫external regulator mode 就是VDDR直接给它供电 相当于我们把DC-DC bypass掉了 直接给它供一个1.8伏的电压 它的范围是1.7到1.9伏 其实这个应用也非常广泛 比如说大家整个的系统电压 就是1.8伏 比如说你和你的modem做一个手表 这样的话 你可以直接用这种模式 它所有的IO口都是1.8伏 这样它可以让你节省一些电频转换的工作 如果大家用这种模式 TI有一些相关的电源推荐 这种高效的TPS62740 它可以支持不同模式 好我们看一下VDDR 其实整个电源链的架构就是这样 我们在系统里有一个DC-DC 包括跟它并行地我们还有一个global LDO 它们最后输出的电压叫VDDR 就是我们拐角上看到这个电压 然后再经过内部一系列电源链的分 分别分发给各个模块的系统来工作 我来介绍这张图主要的意思呢 这个VDDR是非常非常重要的 如果大家在debug的时候 可以测试一下VDDR 另外 系统是由global LDO 和DC-DC 来供电的 它俩是或者的关系 就说你可以选DC-DC模式 也可以选global LDO模式 当然 DC-DC 可以给你更好的效率 好我们来看一下设计里另一个重要的部分 就是clock部分 clock部分一般分为两种clock 第一部分是fast clock fast clock主要是支持在芯片active模式下 以及射频电路上面的参考时钟 所以时钟对射频指标的影响 非常非常大 关于具体的crystal设计的guideline 和器件选型 大家可以参照这篇文档 这里面我给大家提一下的就是咱们的负载电容 和 等效串联电阻这些值 一定要满足咱们的设计需求 因为这些负载电容值和ESR 会直接影响到咱们 crystal的机身条件 如果机身条件不好的话 这个芯片有可能面临停 (听不清) 然后slow clock主要是在维持芯片在启动 或者在低功耗模式下 它的一些时钟的管理 比如我们可以外接一个32khz的crystal 另外最主要的 我们在最新地芯片上可以节省外部的RC电路 它可以达到一些响应的指标 具体地我们可以参考一下这篇文档 它在不同地状态下会省点或者会更费电 或者怎么样 好我们来看一下debug电路 debug电路这块芯片支持jtag 在我们TI主要提供几种这样的仿真器 一个是XDS100V3这个在我们的smart F001B上用的就是这 个仿真器 另外就是XDS110 这个是在我们的launchpad上面应用到的一个仿真器 同时也是支持其他一些市面上 比较流行的jtag仿真器 好 我们来看一下射频部分 射频在我们的参考设计里 一般都会设成两个射频的 端口 一个是SMA的connector 这种SMA的连接器 或者其他类型的连接器 它的主要作用就是 让我们来测试和评估 它的射频指标 另外就是还有一个板载天线 板载天线在我们的launchpad上面 就是那种倒F的天线 就是(听不清)天线 上面设计我们一般设计了一个(听不清)的流用电阻 当你朝这边焊接的时候 你是来测试它的射频指标 朝这边焊接的时候 你是来调软件 然后用一些板载天线做一些测试 这一部分 R12和C15 我们是预留 用来调试天线的匹配的 好 射频口主要有三个端口 一个是RFP和RFN 就是叉分的RF端口 等一会儿可以给大家介绍 射频可以非常灵活地配置 不但支持叉分 还支持单端 另外还有RX-TX 这样的bias拐角 它主要是给内部的(听不清)做bias用的 会影响接收器灵敏度的一些指标 这张slice主要给大家介绍一下射频前端不同的选项 我们可以看到这里面有四个象限 横坐标我们可以看 这里面有差分的区别 和单端的射频前端的区别 纵坐标我们可以看一下 有internal bias和external bias的区别 internal bias和external bias的区别主要是看RX-TX拐角有没有用于 我们内部RNA的馈电 differential和single-ended设计主要是看我们射频前端 是用了差分的设计还是单端的设计 这样的一些区别 我们可以看到 差分的射频前端的设计 加上 external bias 它拥有最高的发射功率 和最好的接收机灵敏度的指标 但是它的器件也是非常多的 也是最多的一个 另外期间最少的 最大发射器和接收机灵敏度最差的设计 是在这里 它只需要四个器件 但是它最大的发射功率是2DBM 接收机的灵敏度大概在BLE模式下 会比我们的EXTERNAL BIAS 差分要低3DB 是这样的一个设计 但是它的尺寸和 器件数量都是最少的 所以大家如果对于cost 或者 设计尺寸要求非常非常苛刻的话 我是建议大家用差分的方式来做 另外大家可以看一下 在另外两个象限 我们提供了折中的方案 大家可以根据自己的设计进行选择 好 这个是总的参考表 我们可以看到 对于不同的 射频前端的选项 我们会得到不同地射频指标 比如说 我们想要最大的电路预算 我们可以选择差分的EXTERNAL BIAS的设计 如果我们要最小的尺寸 我们可以选择INTERNAL BIAS加SINGLE ENDED这样 的一个设计 好 谢谢大家 这个就是原理图部分的介绍

欢迎回来 我是张希伟

我们来继续介绍一下CC2640以及CC2640R2F

它的硬件射频方面的一些相关知识

首先在这个章节当中 会给大家介绍一下原理图方面的一些相关知识和

会介绍一些原理图的各个部分和功能

以及器械选型方面 需要注意的一些东西

以及射频前端 怎么样去选

好 首先我们看一下这张原理图

这张原理图 我是拿了一个TI的CC2640

5X5的一个设计

给大家大概介绍一下

首先对于TI的芯片4X4 5X5 7X7来说

对于IO口的数量是不同的

但是其他的一些设计 比如说电源

射频前端 晶振方面 还有debug接口

等等 这些方面都是一模一样的 所以大家在设计的时候

可以互相抄袭一下

就是IO口的数量不同而已

就这么一个变化 对于原理图来说

比方我们来看一下这张图 它是5X5的设计

5X5的设计 射频前端是叉分的 外部偏置的设计

比如说你在看4X4的时候

可能我们只提供了 4X4的单端这么一个设计

其实很简单 你可以直接把5X5的差分设计

拷贝到4X4的设计里面就可以了

就是这样的一些方法

接下来我会带大家 从各模块做一个剖析和介绍

首先我们来看电源部分的设计

这个就是最标准的(听不清)工作范围的设计

它的电压工作范围是从1.8-3.8伏

这个电压范围也非常好 非常适合两节五号电池

供电 它基本可以让两节5号电池把它的电池放到100% 放光

因为它最低支持的工作电压是1.8伏

外围电路是非常标准的 DC-DC外围电路

就是大电杆加电容的架构

包括输入部分也有大电容来支持DC-DC的正常工作

最后这个部分DC-DC电路会送出一个电压 叫

VDDR R应该是regulatory的意思

它再去送到我们芯片内部来工作

大家在做器械选型的时候 一定要记得 这个10(听不清)

对于电感和电容来说非常非常重要

它是整个电路中非常重要的器件 如果器件不满足

我们所要求的指标的话 就比如说电流

包括它在额定电流下的感量或电容量的话

这个芯片可能面临频繁进到掉电重启的状态

大家在选型的时候需要注意到这些点

然后我们看一下另外一种供电方式

叫external regulator mode

就是VDDR直接给它供电 相当于我们把DC-DC bypass掉了

直接给它供一个1.8伏的电压

它的范围是1.7到1.9伏

其实这个应用也非常广泛

比如说大家整个的系统电压

就是1.8伏 比如说你和你的modem做一个手表

这样的话 你可以直接用这种模式 它所有的IO口都是1.8伏

这样它可以让你节省一些电频转换的工作

如果大家用这种模式 TI有一些相关的电源推荐

这种高效的TPS62740 它可以支持不同模式

好我们看一下VDDR 其实整个电源链的架构就是这样

我们在系统里有一个DC-DC

包括跟它并行地我们还有一个global LDO

它们最后输出的电压叫VDDR 就是我们拐角上看到这个电压

然后再经过内部一系列电源链的分 分别分发给各个模块的系统来工作

我来介绍这张图主要的意思呢 这个VDDR是非常非常重要的

如果大家在debug的时候

可以测试一下VDDR 另外 系统是由global LDO 和DC-DC

来供电的 它俩是或者的关系 就说你可以选DC-DC模式

也可以选global LDO模式 当然 DC-DC 可以给你更好的效率

好我们来看一下设计里另一个重要的部分

就是clock部分

clock部分一般分为两种clock 第一部分是fast clock

fast clock主要是支持在芯片active模式下 以及射频电路上面的参考时钟

所以时钟对射频指标的影响 非常非常大

关于具体的crystal设计的guideline

和器件选型 大家可以参照这篇文档

这里面我给大家提一下的就是咱们的负载电容 和

等效串联电阻这些值 一定要满足咱们的设计需求

因为这些负载电容值和ESR 会直接影响到咱们

crystal的机身条件

如果机身条件不好的话 这个芯片有可能面临停 (听不清)

然后slow clock主要是在维持芯片在启动 或者在低功耗模式下

它的一些时钟的管理 比如我们可以外接一个32khz的crystal

另外最主要的 我们在最新地芯片上可以节省外部的RC电路

它可以达到一些响应的指标

具体地我们可以参考一下这篇文档

它在不同地状态下会省点或者会更费电

或者怎么样

好我们来看一下debug电路 debug电路这块芯片支持jtag

在我们TI主要提供几种这样的仿真器

一个是XDS100V3这个在我们的smart F001B上用的就是这

个仿真器 另外就是XDS110

这个是在我们的launchpad上面应用到的一个仿真器

同时也是支持其他一些市面上 比较流行的jtag仿真器

好 我们来看一下射频部分

射频在我们的参考设计里 一般都会设成两个射频的

端口 一个是SMA的connector 这种SMA的连接器

或者其他类型的连接器 它的主要作用就是

让我们来测试和评估

它的射频指标 另外就是还有一个板载天线

板载天线在我们的launchpad上面 就是那种倒F的天线

就是(听不清)天线

上面设计我们一般设计了一个(听不清)的流用电阻

当你朝这边焊接的时候 你是来测试它的射频指标

朝这边焊接的时候 你是来调软件

然后用一些板载天线做一些测试

这一部分 R12和C15

我们是预留 用来调试天线的匹配的

好 射频口主要有三个端口

一个是RFP和RFN 就是叉分的RF端口

等一会儿可以给大家介绍 射频可以非常灵活地配置

不但支持叉分 还支持单端

另外还有RX-TX 这样的bias拐角

它主要是给内部的(听不清)做bias用的

会影响接收器灵敏度的一些指标

这张slice主要给大家介绍一下射频前端不同的选项

我们可以看到这里面有四个象限

横坐标我们可以看 这里面有差分的区别

和单端的射频前端的区别

纵坐标我们可以看一下 有internal bias和external bias的区别

internal bias和external bias的区别主要是看RX-TX拐角有没有用于

我们内部RNA的馈电

differential和single-ended设计主要是看我们射频前端

是用了差分的设计还是单端的设计 这样的一些区别

我们可以看到 差分的射频前端的设计 加上 external bias

它拥有最高的发射功率

和最好的接收机灵敏度的指标

但是它的器件也是非常多的 也是最多的一个

另外期间最少的 最大发射器和接收机灵敏度最差的设计

是在这里 它只需要四个器件

但是它最大的发射功率是2DBM

接收机的灵敏度大概在BLE模式下 会比我们的EXTERNAL BIAS

差分要低3DB

是这样的一个设计 但是它的尺寸和

器件数量都是最少的 所以大家如果对于cost 或者

设计尺寸要求非常非常苛刻的话

我是建议大家用差分的方式来做

另外大家可以看一下 在另外两个象限 我们提供了折中的方案

大家可以根据自己的设计进行选择

好 这个是总的参考表 我们可以看到

对于不同的 射频前端的选项

我们会得到不同地射频指标

比如说 我们想要最大的电路预算

我们可以选择差分的EXTERNAL BIAS的设计

如果我们要最小的尺寸 我们可以选择INTERNAL BIAS加SINGLE ENDED这样

的一个设计

好 谢谢大家 这个就是原理图部分的介绍

手机看

扫码用手机观看

视频简介

视频简介

CC2640R2F硬件射频从设计到成型之二-CC2640R2F原理图及器件选型

所属课程:CC2640R2F硬件射频从设计到成型

发布时间:2017.04.19

视频集数:8

本节视频时长:00:10:19

对TI的BLE产品CC2640R2F的硬件、射频、硬件测试等相关知识做了介绍。

内容包括: 产品一览;原理图;器件选型;参考设计,layout布板关键准则;CC2640到CC2640R2F的硬件移植; BT5.0PHY;天线套件介绍;硬件设计流程及认证简介;在线资源介绍和长通信距离测试。

未学习 CC2640R2F硬件射频从设计到成型之一-CC2640R2F产品一览

未学习 CC2640R2F硬件射频从设计到成型之一-CC2640R2F产品一览

未学习 CC2640R2F硬件射频从设计到成型之二-CC2640R2F原理图及器件选型

未学习 CC2640R2F硬件射频从设计到成型之二-CC2640R2F原理图及器件选型

未学习 CC2640R2F硬件射频从设计到成型之三-CC2640R2F布板关键准则

未学习 CC2640R2F硬件射频从设计到成型之三-CC2640R2F布板关键准则

未学习 CC2640R2F硬件射频从设计到成型之四-CC2640R2F从CC2640到CC2640R2F的硬件移植_BT5.0PHY

未学习 CC2640R2F硬件射频从设计到成型之四-CC2640R2F从CC2640到CC2640R2F的硬件移植_BT5.0PHY

未学习 CC2640R2F硬件射频从设计到成型之五-CC2640R2F天线套件介绍

未学习 CC2640R2F硬件射频从设计到成型之五-CC2640R2F天线套件介绍

未学习 CC2640R2F硬件射频从设计到成型之六-CC2640R2F硬件设计流程及认证简介

未学习 CC2640R2F硬件射频从设计到成型之六-CC2640R2F硬件设计流程及认证简介

未学习 CC2640R2F硬件射频从设计到成型之七-CC2640R2F在线资源介绍

未学习 CC2640R2F硬件射频从设计到成型之七-CC2640R2F在线资源介绍

未学习 CC2640R2F长通信距离测试

未学习 CC2640R2F长通信距离测试