UCD3138数字PWM(DPWM)模块:控制DPWM输出

Loading the player...

将在30s后自动为您播放下一课程

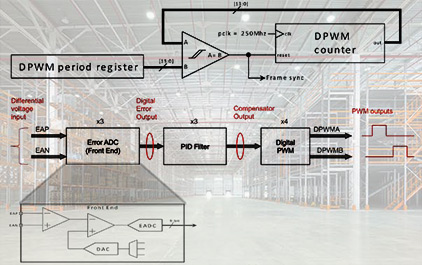

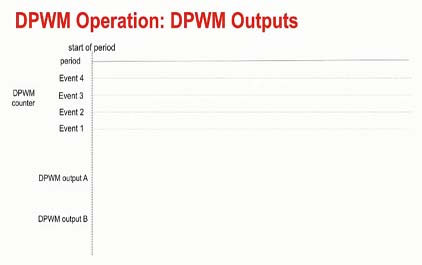

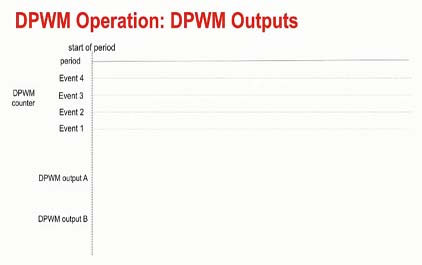

现在,我将演示 如何 在开环模式下控制 DPWM 的 A 和 B 两项输出。 开环模式意味着 DPWM 完全由其 而非滤波器 输出控制。 换句话说,电源 控制环路未闭合。 我们将在稍后的 实验练习中闭合环路。 在开环模式下,输出 A 的 上升沿和下降沿 由事件 1 和 事件 2 控制。 事件 1 和事件 2 是 两个寄存器的内容。 输出 B 的 上升沿和下降沿 由事件 3 和 事件 4 控制。 同样,这些值存储在两个 单独的寄存器中。 在此我们可以看到 DPWM 计数器 从 0 增大到事件 1。 当计数器值 等于事件 1 时, 被置为输出 DPWM A。 当计数器值等于事件 2 时, DPWM A 会被复位。 当计数器值 等于事件 3 时, 被置为输出 DPWM B。 当计数器值达到 事件 4 时,输出 B 会被复位。 当计数器值等于 周期寄存器中的值时, 计数器会复位 且另一开关周期 会启动。 事件 1 存储在 寄存器 DPWMEV1 中。 因此,每个 DPWM 模块将 具有一个独特的 DPWMEV1 寄存器与其相关联。 寄存器 从 PCLK 驱动, 因此具有与 周期寄存器 相同的 4 ns 时基。 它还具有与周期寄存器 相同的校准。 因此,事件 1 字段 与 DPWMEV1 寄存器的 位 4 对齐。 在上一示例中, 通过将 2,500 置于 PRD 字段中, 我们将周期 设为 10 ms。 为将输出 A 设为在 10% 周期时处于高位, 我们将事件 1 设为 250,即将 PRD 值除以 10。 事件 2 存储在 称作 DPWMEV2 的寄存器中。 每个 DPWM 模块都有 唯一的 DPWMEV2 寄存器。 事件 2 的周期 分辨率比事件 1 高 16 倍; 即,它具有 250 ps 的 时基。 通过提供 DPWM 模块 可取得额外的分辨率, 前提是该模块具有 16 个分别 为 250 MHz 的相移时钟信号。 我们已将周期 设为 10 ms, 并将输出 A 的 上升沿 设为在周期的 10% 时发生。 为将输出 A 在 25% 周期时复位, 我们将周期除以 4。 然后,我们将结果乘以 16 以计入 事件 2 对比该周期小 16 倍的时基。 值得注意的是, 即使事件 2 比事件 1 周期的分辨率 高 16 倍, 事件 1 以及 周期字段均会 在其相应 寄存器中抵消, 以计入 更小的时基。 因此,您在写入 整个寄存器时, 无需考虑事件 2 更小的时基。 这样,出于明确性 和简洁性考虑, 我们不建议在写入 这些寄存器时 使用 .bit 结构。 使用 .all 结构 并将事件寄存器 设为周期百分比。 在此代码示例中,我们使用 预处理程序 #define 指令 来定义 PCLK 周期 和开关周期, 单位为秒。 然后,我们使用 这两个值计算 要置于周期寄存器中的值。 通过将周期值简单乘以 0.1、0.25、 0.5 和 0.75, 事件 1、2、3 和 4 寄存器会设为等于周期的 25%、50% 和 75%。 如果我们决定更改 开关周期, 我们只需更改 指派给 #define 周期的秒数, 然后所有 事件寄存器 将自动扩展。 事件 3 和事件 4 将 分别存储在 DPWMEV3 和 EV4 中。 他们具有与事件 2 相同的 对齐和时基, 即,它们为 18 位宽且具有 250 ps 的时基。 这是 DPWM 模块的 简化逻辑图, 涵盖迄今为止 我们已讨论的问题。 我们已了解开环模式中的 DPWM 操作, 开环模式意味着 DPWM 输出完全由其 自身的寄存器控制,而非由滤波器 输出控制。 有多得多的逻辑 以及更多的寄存器 与 DPWM 操作关联,其中有些我们将在 这些实验中讨论。 现在,我们对事件 寄存器的输出 直接进行大量 可配置的时序逻辑计算。 我们将在稍后的实验中 回顾该逻辑的某些内容。 现在,对于其他 初始化, 您将需要 置于 C 代码中, 以在开环模式下 使用 DPWM 模块。 您应在初始化前 关闭 DPWM0, 具体方法是清除 DPWM 控制 寄存器 0 中的 PWM 启用位。 默认情况下, 该位实际上会被清除, 因此,严格意义上讲, 这不是必需的。 但是,尽管如此,这仍然是 好的做法。 由于我们在开环模式下 操作 DPWM 模块, 因此我们需要关闭 DPWM 的 滤波器输入, 从而 DPWM 操作 完全由 其自身的寄存器控制。 我们所采取的具体方法是清除 PWM 控制 寄存器 0 中的 CLA 启用位。 CLA 是控制律加速器的 缩写词。 这只是滤波器的 另一名称。 接下来,我们需要在本地 开启 DPWM 模块, 具体方法是在 DPWM 控制 寄存器 0 中设置 PWM 启用位。 最后,我们需要在全局 开启 DPWM 模块, 具体方法是在 GLB 启用模块中 设置相关全局启用位。 每个 DPWM 具有其 自身的全局启用位。 我们在此为 DPWM 模块 0 设置位。 如果您要查找有关 该实验目前为止 所涵盖主题的 更全面的信息, 请参阅 UCD3138 数字电源外设 程序员手册。 现在我们来看 C 源代码

现在,我将演示 如何 在开环模式下控制 DPWM 的 A 和 B 两项输出。 开环模式意味着 DPWM 完全由其 而非滤波器 输出控制。 换句话说,电源 控制环路未闭合。 我们将在稍后的 实验练习中闭合环路。 在开环模式下,输出 A 的 上升沿和下降沿 由事件 1 和 事件 2 控制。 事件 1 和事件 2 是 两个寄存器的内容。 输出 B 的 上升沿和下降沿 由事件 3 和 事件 4 控制。 同样,这些值存储在两个 单独的寄存器中。 在此我们可以看到 DPWM 计数器 从 0 增大到事件 1。 当计数器值 等于事件 1 时, 被置为输出 DPWM A。 当计数器值等于事件 2 时, DPWM A 会被复位。 当计数器值 等于事件 3 时, 被置为输出 DPWM B。 当计数器值达到 事件 4 时,输出 B 会被复位。 当计数器值等于 周期寄存器中的值时, 计数器会复位 且另一开关周期 会启动。 事件 1 存储在 寄存器 DPWMEV1 中。 因此,每个 DPWM 模块将 具有一个独特的 DPWMEV1 寄存器与其相关联。 寄存器 从 PCLK 驱动, 因此具有与 周期寄存器 相同的 4 ns 时基。 它还具有与周期寄存器 相同的校准。 因此,事件 1 字段 与 DPWMEV1 寄存器的 位 4 对齐。 在上一示例中, 通过将 2,500 置于 PRD 字段中, 我们将周期 设为 10 ms。 为将输出 A 设为在 10% 周期时处于高位, 我们将事件 1 设为 250,即将 PRD 值除以 10。 事件 2 存储在 称作 DPWMEV2 的寄存器中。 每个 DPWM 模块都有 唯一的 DPWMEV2 寄存器。 事件 2 的周期 分辨率比事件 1 高 16 倍; 即,它具有 250 ps 的 时基。 通过提供 DPWM 模块 可取得额外的分辨率, 前提是该模块具有 16 个分别 为 250 MHz 的相移时钟信号。 我们已将周期 设为 10 ms, 并将输出 A 的 上升沿 设为在周期的 10% 时发生。 为将输出 A 在 25% 周期时复位, 我们将周期除以 4。 然后,我们将结果乘以 16 以计入 事件 2 对比该周期小 16 倍的时基。 值得注意的是, 即使事件 2 比事件 1 周期的分辨率 高 16 倍, 事件 1 以及 周期字段均会 在其相应 寄存器中抵消, 以计入 更小的时基。 因此,您在写入 整个寄存器时, 无需考虑事件 2 更小的时基。 这样,出于明确性 和简洁性考虑, 我们不建议在写入 这些寄存器时 使用 .bit 结构。 使用 .all 结构 并将事件寄存器 设为周期百分比。 在此代码示例中,我们使用 预处理程序 #define 指令 来定义 PCLK 周期 和开关周期, 单位为秒。 然后,我们使用 这两个值计算 要置于周期寄存器中的值。 通过将周期值简单乘以 0.1、0.25、 0.5 和 0.75, 事件 1、2、3 和 4 寄存器会设为等于周期的 25%、50% 和 75%。 如果我们决定更改 开关周期, 我们只需更改 指派给 #define 周期的秒数, 然后所有 事件寄存器 将自动扩展。 事件 3 和事件 4 将 分别存储在 DPWMEV3 和 EV4 中。 他们具有与事件 2 相同的 对齐和时基, 即,它们为 18 位宽且具有 250 ps 的时基。 这是 DPWM 模块的 简化逻辑图, 涵盖迄今为止 我们已讨论的问题。 我们已了解开环模式中的 DPWM 操作, 开环模式意味着 DPWM 输出完全由其 自身的寄存器控制,而非由滤波器 输出控制。 有多得多的逻辑 以及更多的寄存器 与 DPWM 操作关联,其中有些我们将在 这些实验中讨论。 现在,我们对事件 寄存器的输出 直接进行大量 可配置的时序逻辑计算。 我们将在稍后的实验中 回顾该逻辑的某些内容。 现在,对于其他 初始化, 您将需要 置于 C 代码中, 以在开环模式下 使用 DPWM 模块。 您应在初始化前 关闭 DPWM0, 具体方法是清除 DPWM 控制 寄存器 0 中的 PWM 启用位。 默认情况下, 该位实际上会被清除, 因此,严格意义上讲, 这不是必需的。 但是,尽管如此,这仍然是 好的做法。 由于我们在开环模式下 操作 DPWM 模块, 因此我们需要关闭 DPWM 的 滤波器输入, 从而 DPWM 操作 完全由 其自身的寄存器控制。 我们所采取的具体方法是清除 PWM 控制 寄存器 0 中的 CLA 启用位。 CLA 是控制律加速器的 缩写词。 这只是滤波器的 另一名称。 接下来,我们需要在本地 开启 DPWM 模块, 具体方法是在 DPWM 控制 寄存器 0 中设置 PWM 启用位。 最后,我们需要在全局 开启 DPWM 模块, 具体方法是在 GLB 启用模块中 设置相关全局启用位。 每个 DPWM 具有其 自身的全局启用位。 我们在此为 DPWM 模块 0 设置位。 如果您要查找有关 该实验目前为止 所涵盖主题的 更全面的信息, 请参阅 UCD3138 数字电源外设 程序员手册。 现在我们来看 C 源代码

现在,我将演示 如何

在开环模式下控制 DPWM 的 A 和 B 两项输出。

开环模式意味着 DPWM 完全由其

而非滤波器 输出控制。

换句话说,电源 控制环路未闭合。

我们将在稍后的 实验练习中闭合环路。

在开环模式下,输出 A 的 上升沿和下降沿

由事件 1 和 事件 2 控制。

事件 1 和事件 2 是 两个寄存器的内容。

输出 B 的 上升沿和下降沿

由事件 3 和 事件 4 控制。

同样,这些值存储在两个 单独的寄存器中。

在此我们可以看到 DPWM 计数器 从 0 增大到事件 1。

当计数器值 等于事件 1 时,

被置为输出 DPWM A。

当计数器值等于事件 2 时, DPWM A 会被复位。

当计数器值 等于事件 3 时,

被置为输出 DPWM B。

当计数器值达到 事件 4 时,输出 B 会被复位。

当计数器值等于 周期寄存器中的值时,

计数器会复位 且另一开关周期

会启动。

事件 1 存储在 寄存器 DPWMEV1 中。

因此,每个 DPWM 模块将 具有一个独特的 DPWMEV1

寄存器与其相关联。

寄存器 从 PCLK 驱动,

因此具有与 周期寄存器

相同的 4 ns 时基。

它还具有与周期寄存器 相同的校准。

因此,事件 1 字段 与 DPWMEV1 寄存器的

位 4 对齐。

在上一示例中, 通过将 2,500 置于 PRD 字段中,

我们将周期 设为 10 ms。

为将输出 A 设为在 10% 周期时处于高位,

我们将事件 1 设为 250,即将 PRD 值除以 10。

事件 2 存储在 称作 DPWMEV2 的寄存器中。

每个 DPWM 模块都有 唯一的 DPWMEV2 寄存器。

事件 2 的周期 分辨率比事件 1

高 16 倍;

即,它具有 250 ps 的 时基。

通过提供 DPWM 模块 可取得额外的分辨率,

前提是该模块具有 16 个分别 为 250 MHz 的相移时钟信号。

我们已将周期 设为 10 ms,

并将输出 A 的 上升沿

设为在周期的 10% 时发生。

为将输出 A 在 25% 周期时复位,

我们将周期除以 4。

然后,我们将结果乘以 16 以计入

事件 2 对比该周期小 16 倍的时基。

值得注意的是, 即使事件 2 比事件 1

周期的分辨率 高 16 倍,

事件 1 以及 周期字段均会

在其相应 寄存器中抵消,

以计入 更小的时基。

因此,您在写入 整个寄存器时,

无需考虑事件 2 更小的时基。

这样,出于明确性 和简洁性考虑,

我们不建议在写入 这些寄存器时

使用 .bit 结构。

使用 .all 结构 并将事件寄存器

设为周期百分比。

在此代码示例中,我们使用 预处理程序 #define 指令

来定义 PCLK 周期 和开关周期,

单位为秒。

然后,我们使用 这两个值计算

要置于周期寄存器中的值。

通过将周期值简单乘以 0.1、0.25、

0.5 和 0.75, 事件 1、2、3 和 4

寄存器会设为等于周期的 25%、50% 和 75%。

如果我们决定更改 开关周期,

我们只需更改 指派给 #define 周期的秒数,

然后所有 事件寄存器

将自动扩展。

事件 3 和事件 4 将 分别存储在 DPWMEV3

和 EV4 中。

他们具有与事件 2 相同的 对齐和时基,

即,它们为 18 位宽且具有

250 ps 的时基。

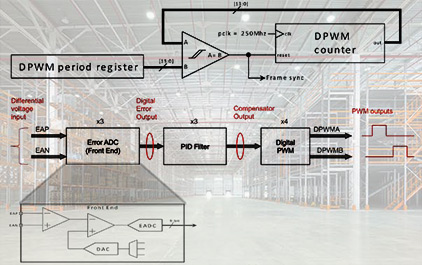

这是 DPWM 模块的 简化逻辑图,

涵盖迄今为止 我们已讨论的问题。

我们已了解开环模式中的 DPWM 操作,

开环模式意味着 DPWM 输出完全由其

自身的寄存器控制,而非由滤波器 输出控制。

有多得多的逻辑 以及更多的寄存器

与 DPWM 操作关联,其中有些我们将在

这些实验中讨论。

现在,我们对事件 寄存器的输出

直接进行大量 可配置的时序逻辑计算。

我们将在稍后的实验中 回顾该逻辑的某些内容。

现在,对于其他 初始化,

您将需要 置于 C 代码中,

以在开环模式下 使用 DPWM 模块。

您应在初始化前 关闭 DPWM0,

具体方法是清除 DPWM 控制 寄存器 0 中的 PWM 启用位。

默认情况下, 该位实际上会被清除,

因此,严格意义上讲, 这不是必需的。

但是,尽管如此,这仍然是 好的做法。

由于我们在开环模式下 操作 DPWM 模块,

因此我们需要关闭 DPWM 的 滤波器输入,

从而 DPWM 操作 完全由

其自身的寄存器控制。

我们所采取的具体方法是清除 PWM 控制 寄存器 0 中的 CLA

启用位。

CLA 是控制律加速器的 缩写词。

这只是滤波器的 另一名称。

接下来,我们需要在本地 开启 DPWM 模块,

具体方法是在 DPWM 控制 寄存器 0 中设置 PWM

启用位。

最后,我们需要在全局 开启 DPWM 模块,

具体方法是在 GLB 启用模块中

设置相关全局启用位。

每个 DPWM 具有其 自身的全局启用位。

我们在此为 DPWM 模块 0 设置位。

如果您要查找有关 该实验目前为止

所涵盖主题的 更全面的信息,

请参阅 UCD3138 数字电源外设

程序员手册。

现在我们来看 C 源代码

现在,我将演示 如何 在开环模式下控制 DPWM 的 A 和 B 两项输出。 开环模式意味着 DPWM 完全由其 而非滤波器 输出控制。 换句话说,电源 控制环路未闭合。 我们将在稍后的 实验练习中闭合环路。 在开环模式下,输出 A 的 上升沿和下降沿 由事件 1 和 事件 2 控制。 事件 1 和事件 2 是 两个寄存器的内容。 输出 B 的 上升沿和下降沿 由事件 3 和 事件 4 控制。 同样,这些值存储在两个 单独的寄存器中。 在此我们可以看到 DPWM 计数器 从 0 增大到事件 1。 当计数器值 等于事件 1 时, 被置为输出 DPWM A。 当计数器值等于事件 2 时, DPWM A 会被复位。 当计数器值 等于事件 3 时, 被置为输出 DPWM B。 当计数器值达到 事件 4 时,输出 B 会被复位。 当计数器值等于 周期寄存器中的值时, 计数器会复位 且另一开关周期 会启动。 事件 1 存储在 寄存器 DPWMEV1 中。 因此,每个 DPWM 模块将 具有一个独特的 DPWMEV1 寄存器与其相关联。 寄存器 从 PCLK 驱动, 因此具有与 周期寄存器 相同的 4 ns 时基。 它还具有与周期寄存器 相同的校准。 因此,事件 1 字段 与 DPWMEV1 寄存器的 位 4 对齐。 在上一示例中, 通过将 2,500 置于 PRD 字段中, 我们将周期 设为 10 ms。 为将输出 A 设为在 10% 周期时处于高位, 我们将事件 1 设为 250,即将 PRD 值除以 10。 事件 2 存储在 称作 DPWMEV2 的寄存器中。 每个 DPWM 模块都有 唯一的 DPWMEV2 寄存器。 事件 2 的周期 分辨率比事件 1 高 16 倍; 即,它具有 250 ps 的 时基。 通过提供 DPWM 模块 可取得额外的分辨率, 前提是该模块具有 16 个分别 为 250 MHz 的相移时钟信号。 我们已将周期 设为 10 ms, 并将输出 A 的 上升沿 设为在周期的 10% 时发生。 为将输出 A 在 25% 周期时复位, 我们将周期除以 4。 然后,我们将结果乘以 16 以计入 事件 2 对比该周期小 16 倍的时基。 值得注意的是, 即使事件 2 比事件 1 周期的分辨率 高 16 倍, 事件 1 以及 周期字段均会 在其相应 寄存器中抵消, 以计入 更小的时基。 因此,您在写入 整个寄存器时, 无需考虑事件 2 更小的时基。 这样,出于明确性 和简洁性考虑, 我们不建议在写入 这些寄存器时 使用 .bit 结构。 使用 .all 结构 并将事件寄存器 设为周期百分比。 在此代码示例中,我们使用 预处理程序 #define 指令 来定义 PCLK 周期 和开关周期, 单位为秒。 然后,我们使用 这两个值计算 要置于周期寄存器中的值。 通过将周期值简单乘以 0.1、0.25、 0.5 和 0.75, 事件 1、2、3 和 4 寄存器会设为等于周期的 25%、50% 和 75%。 如果我们决定更改 开关周期, 我们只需更改 指派给 #define 周期的秒数, 然后所有 事件寄存器 将自动扩展。 事件 3 和事件 4 将 分别存储在 DPWMEV3 和 EV4 中。 他们具有与事件 2 相同的 对齐和时基, 即,它们为 18 位宽且具有 250 ps 的时基。 这是 DPWM 模块的 简化逻辑图, 涵盖迄今为止 我们已讨论的问题。 我们已了解开环模式中的 DPWM 操作, 开环模式意味着 DPWM 输出完全由其 自身的寄存器控制,而非由滤波器 输出控制。 有多得多的逻辑 以及更多的寄存器 与 DPWM 操作关联,其中有些我们将在 这些实验中讨论。 现在,我们对事件 寄存器的输出 直接进行大量 可配置的时序逻辑计算。 我们将在稍后的实验中 回顾该逻辑的某些内容。 现在,对于其他 初始化, 您将需要 置于 C 代码中, 以在开环模式下 使用 DPWM 模块。 您应在初始化前 关闭 DPWM0, 具体方法是清除 DPWM 控制 寄存器 0 中的 PWM 启用位。 默认情况下, 该位实际上会被清除, 因此,严格意义上讲, 这不是必需的。 但是,尽管如此,这仍然是 好的做法。 由于我们在开环模式下 操作 DPWM 模块, 因此我们需要关闭 DPWM 的 滤波器输入, 从而 DPWM 操作 完全由 其自身的寄存器控制。 我们所采取的具体方法是清除 PWM 控制 寄存器 0 中的 CLA 启用位。 CLA 是控制律加速器的 缩写词。 这只是滤波器的 另一名称。 接下来,我们需要在本地 开启 DPWM 模块, 具体方法是在 DPWM 控制 寄存器 0 中设置 PWM 启用位。 最后,我们需要在全局 开启 DPWM 模块, 具体方法是在 GLB 启用模块中 设置相关全局启用位。 每个 DPWM 具有其 自身的全局启用位。 我们在此为 DPWM 模块 0 设置位。 如果您要查找有关 该实验目前为止 所涵盖主题的 更全面的信息, 请参阅 UCD3138 数字电源外设 程序员手册。 现在我们来看 C 源代码

现在,我将演示 如何

在开环模式下控制 DPWM 的 A 和 B 两项输出。

开环模式意味着 DPWM 完全由其

而非滤波器 输出控制。

换句话说,电源 控制环路未闭合。

我们将在稍后的 实验练习中闭合环路。

在开环模式下,输出 A 的 上升沿和下降沿

由事件 1 和 事件 2 控制。

事件 1 和事件 2 是 两个寄存器的内容。

输出 B 的 上升沿和下降沿

由事件 3 和 事件 4 控制。

同样,这些值存储在两个 单独的寄存器中。

在此我们可以看到 DPWM 计数器 从 0 增大到事件 1。

当计数器值 等于事件 1 时,

被置为输出 DPWM A。

当计数器值等于事件 2 时, DPWM A 会被复位。

当计数器值 等于事件 3 时,

被置为输出 DPWM B。

当计数器值达到 事件 4 时,输出 B 会被复位。

当计数器值等于 周期寄存器中的值时,

计数器会复位 且另一开关周期

会启动。

事件 1 存储在 寄存器 DPWMEV1 中。

因此,每个 DPWM 模块将 具有一个独特的 DPWMEV1

寄存器与其相关联。

寄存器 从 PCLK 驱动,

因此具有与 周期寄存器

相同的 4 ns 时基。

它还具有与周期寄存器 相同的校准。

因此,事件 1 字段 与 DPWMEV1 寄存器的

位 4 对齐。

在上一示例中, 通过将 2,500 置于 PRD 字段中,

我们将周期 设为 10 ms。

为将输出 A 设为在 10% 周期时处于高位,

我们将事件 1 设为 250,即将 PRD 值除以 10。

事件 2 存储在 称作 DPWMEV2 的寄存器中。

每个 DPWM 模块都有 唯一的 DPWMEV2 寄存器。

事件 2 的周期 分辨率比事件 1

高 16 倍;

即,它具有 250 ps 的 时基。

通过提供 DPWM 模块 可取得额外的分辨率,

前提是该模块具有 16 个分别 为 250 MHz 的相移时钟信号。

我们已将周期 设为 10 ms,

并将输出 A 的 上升沿

设为在周期的 10% 时发生。

为将输出 A 在 25% 周期时复位,

我们将周期除以 4。

然后,我们将结果乘以 16 以计入

事件 2 对比该周期小 16 倍的时基。

值得注意的是, 即使事件 2 比事件 1

周期的分辨率 高 16 倍,

事件 1 以及 周期字段均会

在其相应 寄存器中抵消,

以计入 更小的时基。

因此,您在写入 整个寄存器时,

无需考虑事件 2 更小的时基。

这样,出于明确性 和简洁性考虑,

我们不建议在写入 这些寄存器时

使用 .bit 结构。

使用 .all 结构 并将事件寄存器

设为周期百分比。

在此代码示例中,我们使用 预处理程序 #define 指令

来定义 PCLK 周期 和开关周期,

单位为秒。

然后,我们使用 这两个值计算

要置于周期寄存器中的值。

通过将周期值简单乘以 0.1、0.25、

0.5 和 0.75, 事件 1、2、3 和 4

寄存器会设为等于周期的 25%、50% 和 75%。

如果我们决定更改 开关周期,

我们只需更改 指派给 #define 周期的秒数,

然后所有 事件寄存器

将自动扩展。

事件 3 和事件 4 将 分别存储在 DPWMEV3

和 EV4 中。

他们具有与事件 2 相同的 对齐和时基,

即,它们为 18 位宽且具有

250 ps 的时基。

这是 DPWM 模块的 简化逻辑图,

涵盖迄今为止 我们已讨论的问题。

我们已了解开环模式中的 DPWM 操作,

开环模式意味着 DPWM 输出完全由其

自身的寄存器控制,而非由滤波器 输出控制。

有多得多的逻辑 以及更多的寄存器

与 DPWM 操作关联,其中有些我们将在

这些实验中讨论。

现在,我们对事件 寄存器的输出

直接进行大量 可配置的时序逻辑计算。

我们将在稍后的实验中 回顾该逻辑的某些内容。

现在,对于其他 初始化,

您将需要 置于 C 代码中,

以在开环模式下 使用 DPWM 模块。

您应在初始化前 关闭 DPWM0,

具体方法是清除 DPWM 控制 寄存器 0 中的 PWM 启用位。

默认情况下, 该位实际上会被清除,

因此,严格意义上讲, 这不是必需的。

但是,尽管如此,这仍然是 好的做法。

由于我们在开环模式下 操作 DPWM 模块,

因此我们需要关闭 DPWM 的 滤波器输入,

从而 DPWM 操作 完全由

其自身的寄存器控制。

我们所采取的具体方法是清除 PWM 控制 寄存器 0 中的 CLA

启用位。

CLA 是控制律加速器的 缩写词。

这只是滤波器的 另一名称。

接下来,我们需要在本地 开启 DPWM 模块,

具体方法是在 DPWM 控制 寄存器 0 中设置 PWM

启用位。

最后,我们需要在全局 开启 DPWM 模块,

具体方法是在 GLB 启用模块中

设置相关全局启用位。

每个 DPWM 具有其 自身的全局启用位。

我们在此为 DPWM 模块 0 设置位。

如果您要查找有关 该实验目前为止

所涵盖主题的 更全面的信息,

请参阅 UCD3138 数字电源外设

程序员手册。

现在我们来看 C 源代码

手机看

扫码用手机观看

视频简介

视频简介

UCD3138数字PWM(DPWM)模块:控制DPWM输出

所属课程:UCD3138数字PWM(DPWM)模块

发布时间:2019.03.11

视频集数:6

本节视频时长:00:08:29

本视频介绍了三种数字电源外设,重点介绍DPWM模块。

未学习 UCD3138数字PWM(DPWM)模块:数字PWM(DPWM)模块简介

未学习 UCD3138数字PWM(DPWM)模块:数字PWM(DPWM)模块简介

未学习 UCD3138数字PWM(DPWM)模块:设置PWM周期

未学习 UCD3138数字PWM(DPWM)模块:设置PWM周期

未学习 UCD3138数字PWM(DPWM)模块:控制DPWM输出

未学习 UCD3138数字PWM(DPWM)模块:控制DPWM输出

未学习 UCD3138数字PWM(DPWM)模块:固件概述和DPWM演示

未学习 UCD3138数字PWM(DPWM)模块:固件概述和DPWM演示

未学习 UCD3138数字PWM(DPWM)模块:内存调试器超级旋转演示

未学习 UCD3138数字PWM(DPWM)模块:内存调试器超级旋转演示

未学习 UCD3138数字PWM(DPWM)模块:固件任务解决方案

未学习 UCD3138数字PWM(DPWM)模块:固件任务解决方案