10.1 TI 高精度实验室 - USB:USB 设计的布局基础知识

Loading the player...

将在30s后自动为您播放下一课程

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论通用串行总线, 也称 USB 的布局 基础知识。 USB 是世界上最受欢迎和 使用最广泛的计算机 接口。 它应用于 各种简单和复杂的 消费性、工业 和汽车应用。 USB 设计的布局 并不复杂, 但为了保持信号 质量,需要考虑 多个因素。 在本课程中,我们将讨论 关于 USB 信号、阻抗、 布线长度和 匹配以及印刷 电路板 (PCB) 堆叠的最常见布局主题。 本课程中的示例重点 讨论 USB 2.0 高速设计, 但也适用于 USB 3.0 第 1 代和第 2 代设计。 在 USB 中,信号通过 差分信令传输。 USB 2.0 使用 单一差分 信号对、DP 和 DM。 USB 3.0 规格 增加了超高速信令, 此信令使用 SSTX 和 SSRX 这两组额外的差分信号对 来支持单独的 全双工连接。 请注意,USB 3.0 规格是累积的, 因此我们提到的 USB 3.2 规格也适用于传统 5G USB 3.0 类型的连接。 USB 2.0 规格 定义的差分 特性阻抗为 90 欧姆 ± 15%, 适用于 USB 2.0 差分对。 USB 3.0 规格定义的 差分特性阻抗 范围为 72 欧姆 到 120 欧姆。 为了优化信号质量, 应在从发送器到 PCB 布线再到 连接器和电缆 乃至下一个 连接器、PCB 布线 和接收器的 整个 USB 路径中 保持此差分阻抗。 阻抗不连续性 可能会导致信号反射 和信号质量下降。 由于我们回顾的 大多数 USB PCB 应用 都将差分信号 布置到外部 PCB 层中, 因此我们将重点 介绍微带阻抗 计算。 可以使用左侧 显示的公式来 计算差分和 单端阻抗。 如果差分信号布置 到内部 PCB 层中, 则必须使用 适用于带状线 应用的阻抗公式。 这些公式已使用 适用于 FR-4 PCB 材料的介电常数 4.4 进行简化。 4.1 到 4.5 是 用于 FR-4 材料的 典型介电 常数范围。 在这些公式中, w 是布线宽度, t 是布线厚度, d 是差分对之间的 布线距离, h 是介电 厚度。 差分阻抗 Z Diff 不到 单端阻抗 Z naught 的两倍。 差分阻抗在 很大程度上取决于 微带应用中的 布线间隔。 差分对 间隔越小, 差分阻抗越低。 阻抗会对信号质量 产生显著的影响。 我们可以 利用眼图来 分析信号质量。 请观看 TI 精密 实验室关于这些 图的视频, 以详细了解 眼图是如何生成的。 左侧是一个来自 90 欧姆差分源的 眼图,此差分源经过 90 欧姆差分布局, 终止于 90 欧姆 差分负载。 右侧是一个来自 90 欧姆差分阻抗源的 眼图,此差分阻抗源经过 100 欧姆差分布局, 终止于 90 欧姆 差分负载。 可以将反射 造成的影响视为 左侧眼图的 闭合。 较长的 不匹配布局 会影响 整个眼图。 和所有高速 信号一样,应最大限度 缩短 USB 布线长度, 以减小通道损耗和防止产生噪声。 一般情况下建议 将 USB 布线长度 保持在 8 英寸以内, 以防止连接器的 信号质量下降。 10G USB 布线长度 还要再短一些。 布置长 PCB 布线时 需要非常小心, 通常建议使用 USB 转接驱动器。 有关转接驱动器 和信号调节器的 更多信息,可以在 TI 精密 实验室的“接口”部分中找到。 除了要最大限度 缩短布线长度以外, 每个差分对的 各条布线的长度 也要保持 一致,对于 USB 2.0 和 USB 3.0,此长度 不能超过 150 密耳和 5 密耳, 以防止产生噪声 并保持差分信令。 不匹配 越少越好。 SSTX 对和 SSRX 对的 布线长度 无需互相一致。 此外,超高速 信号对可以是 极性 f, 以便于路由。 当匹配 USB 信号的 路由链路时, 可以增加蛇形 路由以匹配链路, 如此处所示。 在布线中或在连接器上, 应将蛇形路由与 任何其他 不连续性 结合使用。 由于传播延迟, 不匹配的信号会导致 时序发生细微的变化。 根据经验,PCB 中的 传播延迟为 每英寸 165 皮秒。 此处显示了 微带传播延迟的 具体计算公式, 此公式得出的值略低, 约为每英寸 140 皮秒。 对于 150 密耳的 不匹配,此值 大约相当于 20 到 25 皮秒, 对于 USB 2.0 信号来说 可以忽略不计; 单位间隔为 2.08 纳秒,对于 USB 3.0 信号的 5 密耳不匹配, 此值为 8 皮秒, 对于第 1 代, UI 为 200 皮秒。 对于更快的信号, 也需要考虑 内部接合线 不匹配情况。 在所示的表中, 对于 USB 3.0 5G 信号, 必须考虑 不匹配情况, 但对于 USB 2.0 信号, 不匹配情况无关紧要。 看一看布线 长度的影响,左侧 是一个来自仅仅 两英寸的短布线布局的 眼图。 右侧是一个来自 10 英寸的长布线 布局的眼图。 大家可以看到, 眼图张开度 减小,并对眼图的高度产生了一定影响。 这展示了布线长度 如何影响高速 信号的张开。 布线长度匹配 也可能影响 信号质量。 左侧是一个 来自匹配长度 布局的眼图,具有 小于 50 密耳的不匹配。 右侧是一个 具有 1.5 英寸 布线长度不匹配的 布局的眼图。 眼宽受到了影响。 在 USB 2.0 眼图中, 很难看出布线长度 匹配对信号 质量的影响, 因此我们创建了 一个夸张的不匹配。 左侧是一个来自 具有 50 密耳不匹配的 匹配长度布局的眼图。 右侧是一个 具有 7 英寸 布线长度不匹配的 布局的眼图。 从中可以看出 噪声明显更大的信号 对宽度产生的影响。 PCB 堆叠也会 影响 USB 信号质量。 由于 USB 具有高频率, 因此建议使用 至少四层的 PCB 堆叠在不同的 差分对中提供 实心的接地面。 左侧显示了一个 通常用在 EVM 上的 理想堆叠,具有 由一个接地层 和一个电源层 隔开的两个信号层。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 如果电路非常复杂, 而且必须将信号 作为带状线布线 布置在内层上, 则应特别注意 使用接地层或电源层 将信号层隔开。 右侧显示了一个 主板堆叠示例, 所有信号层 都被接地层隔离。 如果需要在层间走线, 则应最大限度减少 通路数量。 差分对通路 应当对称并 具有配套的接地 通路,以保持接地回路 路径。 这里是一个 非理想 PCB 堆叠 以及它如何影响 信号质量的示例。 左侧是一个 来自 PCB 堆叠的眼图, 差分对布置在 实心接地面的 上方。 右侧是一个 两层 PCB 的眼图, 其中未显示实心 接地面,只使用 差分对附近的 接地填充。 总之要注意, 阻抗、布线长度和 PCB 堆叠有助于 保持信号质量、 降低误码率 以及防止 由于 USB 丢包而 影响系统吞吐量。 为了回顾我们讨论的内容, 我们来做一个小测验。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 对还是错? 对。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 尤其是在 微带应用中。 只要差分对的 布线长度一致, 总长度就 不会影响 信号质量,对还是错? 错。 布线越长,信号 衰减得越多。 这样会导致 眼图中的眼睛 垂直张开度减小。 差分对的 布线长度必须 完全一致, 对还是错? 错。 符合 USB 规格的 容差允许高速 信号的差分对中 存在不匹配 情况。 在可能的情况下, 应将高速差分对 布置在实心 接地面上,对还是错? 对。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 关于 USB 布局基础知识的 讨论到此结束。 大家可以在我们的 TI E2E 社区中获得 有关德州仪器 TI 最新 USB 技术和解决方案的更多信息。 请访问 TI.com/e2e 获取 许多有用问题的答案 以及其他信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论通用串行总线, 也称 USB 的布局 基础知识。 USB 是世界上最受欢迎和 使用最广泛的计算机 接口。 它应用于 各种简单和复杂的 消费性、工业 和汽车应用。 USB 设计的布局 并不复杂, 但为了保持信号 质量,需要考虑 多个因素。 在本课程中,我们将讨论 关于 USB 信号、阻抗、 布线长度和 匹配以及印刷 电路板 (PCB) 堆叠的最常见布局主题。 本课程中的示例重点 讨论 USB 2.0 高速设计, 但也适用于 USB 3.0 第 1 代和第 2 代设计。 在 USB 中,信号通过 差分信令传输。 USB 2.0 使用 单一差分 信号对、DP 和 DM。 USB 3.0 规格 增加了超高速信令, 此信令使用 SSTX 和 SSRX 这两组额外的差分信号对 来支持单独的 全双工连接。 请注意,USB 3.0 规格是累积的, 因此我们提到的 USB 3.2 规格也适用于传统 5G USB 3.0 类型的连接。 USB 2.0 规格 定义的差分 特性阻抗为 90 欧姆 ± 15%, 适用于 USB 2.0 差分对。 USB 3.0 规格定义的 差分特性阻抗 范围为 72 欧姆 到 120 欧姆。 为了优化信号质量, 应在从发送器到 PCB 布线再到 连接器和电缆 乃至下一个 连接器、PCB 布线 和接收器的 整个 USB 路径中 保持此差分阻抗。 阻抗不连续性 可能会导致信号反射 和信号质量下降。 由于我们回顾的 大多数 USB PCB 应用 都将差分信号 布置到外部 PCB 层中, 因此我们将重点 介绍微带阻抗 计算。 可以使用左侧 显示的公式来 计算差分和 单端阻抗。 如果差分信号布置 到内部 PCB 层中, 则必须使用 适用于带状线 应用的阻抗公式。 这些公式已使用 适用于 FR-4 PCB 材料的介电常数 4.4 进行简化。 4.1 到 4.5 是 用于 FR-4 材料的 典型介电 常数范围。 在这些公式中, w 是布线宽度, t 是布线厚度, d 是差分对之间的 布线距离, h 是介电 厚度。 差分阻抗 Z Diff 不到 单端阻抗 Z naught 的两倍。 差分阻抗在 很大程度上取决于 微带应用中的 布线间隔。 差分对 间隔越小, 差分阻抗越低。 阻抗会对信号质量 产生显著的影响。 我们可以 利用眼图来 分析信号质量。 请观看 TI 精密 实验室关于这些 图的视频, 以详细了解 眼图是如何生成的。 左侧是一个来自 90 欧姆差分源的 眼图,此差分源经过 90 欧姆差分布局, 终止于 90 欧姆 差分负载。 右侧是一个来自 90 欧姆差分阻抗源的 眼图,此差分阻抗源经过 100 欧姆差分布局, 终止于 90 欧姆 差分负载。 可以将反射 造成的影响视为 左侧眼图的 闭合。 较长的 不匹配布局 会影响 整个眼图。 和所有高速 信号一样,应最大限度 缩短 USB 布线长度, 以减小通道损耗和防止产生噪声。 一般情况下建议 将 USB 布线长度 保持在 8 英寸以内, 以防止连接器的 信号质量下降。 10G USB 布线长度 还要再短一些。 布置长 PCB 布线时 需要非常小心, 通常建议使用 USB 转接驱动器。 有关转接驱动器 和信号调节器的 更多信息,可以在 TI 精密 实验室的“接口”部分中找到。 除了要最大限度 缩短布线长度以外, 每个差分对的 各条布线的长度 也要保持 一致,对于 USB 2.0 和 USB 3.0,此长度 不能超过 150 密耳和 5 密耳, 以防止产生噪声 并保持差分信令。 不匹配 越少越好。 SSTX 对和 SSRX 对的 布线长度 无需互相一致。 此外,超高速 信号对可以是 极性 f, 以便于路由。 当匹配 USB 信号的 路由链路时, 可以增加蛇形 路由以匹配链路, 如此处所示。 在布线中或在连接器上, 应将蛇形路由与 任何其他 不连续性 结合使用。 由于传播延迟, 不匹配的信号会导致 时序发生细微的变化。 根据经验,PCB 中的 传播延迟为 每英寸 165 皮秒。 此处显示了 微带传播延迟的 具体计算公式, 此公式得出的值略低, 约为每英寸 140 皮秒。 对于 150 密耳的 不匹配,此值 大约相当于 20 到 25 皮秒, 对于 USB 2.0 信号来说 可以忽略不计; 单位间隔为 2.08 纳秒,对于 USB 3.0 信号的 5 密耳不匹配, 此值为 8 皮秒, 对于第 1 代, UI 为 200 皮秒。 对于更快的信号, 也需要考虑 内部接合线 不匹配情况。 在所示的表中, 对于 USB 3.0 5G 信号, 必须考虑 不匹配情况, 但对于 USB 2.0 信号, 不匹配情况无关紧要。 看一看布线 长度的影响,左侧 是一个来自仅仅 两英寸的短布线布局的 眼图。 右侧是一个来自 10 英寸的长布线 布局的眼图。 大家可以看到, 眼图张开度 减小,并对眼图的高度产生了一定影响。 这展示了布线长度 如何影响高速 信号的张开。 布线长度匹配 也可能影响 信号质量。 左侧是一个 来自匹配长度 布局的眼图,具有 小于 50 密耳的不匹配。 右侧是一个 具有 1.5 英寸 布线长度不匹配的 布局的眼图。 眼宽受到了影响。 在 USB 2.0 眼图中, 很难看出布线长度 匹配对信号 质量的影响, 因此我们创建了 一个夸张的不匹配。 左侧是一个来自 具有 50 密耳不匹配的 匹配长度布局的眼图。 右侧是一个 具有 7 英寸 布线长度不匹配的 布局的眼图。 从中可以看出 噪声明显更大的信号 对宽度产生的影响。 PCB 堆叠也会 影响 USB 信号质量。 由于 USB 具有高频率, 因此建议使用 至少四层的 PCB 堆叠在不同的 差分对中提供 实心的接地面。 左侧显示了一个 通常用在 EVM 上的 理想堆叠,具有 由一个接地层 和一个电源层 隔开的两个信号层。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 如果电路非常复杂, 而且必须将信号 作为带状线布线 布置在内层上, 则应特别注意 使用接地层或电源层 将信号层隔开。 右侧显示了一个 主板堆叠示例, 所有信号层 都被接地层隔离。 如果需要在层间走线, 则应最大限度减少 通路数量。 差分对通路 应当对称并 具有配套的接地 通路,以保持接地回路 路径。 这里是一个 非理想 PCB 堆叠 以及它如何影响 信号质量的示例。 左侧是一个 来自 PCB 堆叠的眼图, 差分对布置在 实心接地面的 上方。 右侧是一个 两层 PCB 的眼图, 其中未显示实心 接地面,只使用 差分对附近的 接地填充。 总之要注意, 阻抗、布线长度和 PCB 堆叠有助于 保持信号质量、 降低误码率 以及防止 由于 USB 丢包而 影响系统吞吐量。 为了回顾我们讨论的内容, 我们来做一个小测验。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 对还是错? 对。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 尤其是在 微带应用中。 只要差分对的 布线长度一致, 总长度就 不会影响 信号质量,对还是错? 错。 布线越长,信号 衰减得越多。 这样会导致 眼图中的眼睛 垂直张开度减小。 差分对的 布线长度必须 完全一致, 对还是错? 错。 符合 USB 规格的 容差允许高速 信号的差分对中 存在不匹配 情况。 在可能的情况下, 应将高速差分对 布置在实心 接地面上,对还是错? 对。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 关于 USB 布局基础知识的 讨论到此结束。 大家可以在我们的 TI E2E 社区中获得 有关德州仪器 TI 最新 USB 技术和解决方案的更多信息。 请访问 TI.com/e2e 获取 许多有用问题的答案 以及其他信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。

在本系列中,我们将 讨论通用串行总线,

也称 USB 的布局 基础知识。

USB 是世界上最受欢迎和 使用最广泛的计算机

接口。

它应用于 各种简单和复杂的

消费性、工业 和汽车应用。

USB 设计的布局 并不复杂,

但为了保持信号 质量,需要考虑

多个因素。

在本课程中,我们将讨论 关于 USB 信号、阻抗、

布线长度和 匹配以及印刷

电路板 (PCB) 堆叠的最常见布局主题。

本课程中的示例重点 讨论 USB 2.0 高速设计,

但也适用于 USB 3.0 第 1 代和第 2 代设计。

在 USB 中,信号通过 差分信令传输。

USB 2.0 使用 单一差分

信号对、DP 和 DM。

USB 3.0 规格 增加了超高速信令,

此信令使用 SSTX 和 SSRX 这两组额外的差分信号对

来支持单独的 全双工连接。

请注意,USB 3.0 规格是累积的,

因此我们提到的 USB 3.2 规格也适用于传统

5G USB 3.0 类型的连接。

USB 2.0 规格 定义的差分

特性阻抗为 90 欧姆 ± 15%,

适用于 USB 2.0 差分对。

USB 3.0 规格定义的

差分特性阻抗 范围为 72 欧姆

到 120 欧姆。

为了优化信号质量, 应在从发送器到

PCB 布线再到 连接器和电缆

乃至下一个 连接器、PCB 布线

和接收器的 整个 USB 路径中

保持此差分阻抗。

阻抗不连续性 可能会导致信号反射

和信号质量下降。

由于我们回顾的 大多数 USB PCB 应用

都将差分信号 布置到外部 PCB 层中,

因此我们将重点 介绍微带阻抗

计算。

可以使用左侧 显示的公式来

计算差分和 单端阻抗。

如果差分信号布置 到内部 PCB 层中,

则必须使用 适用于带状线

应用的阻抗公式。

这些公式已使用 适用于 FR-4 PCB

材料的介电常数 4.4 进行简化。

4.1 到 4.5 是 用于 FR-4 材料的

典型介电 常数范围。

在这些公式中, w 是布线宽度,

t 是布线厚度, d 是差分对之间的

布线距离, h 是介电

厚度。

差分阻抗 Z Diff 不到

单端阻抗 Z naught 的两倍。

差分阻抗在 很大程度上取决于

微带应用中的 布线间隔。

差分对 间隔越小,

差分阻抗越低。

阻抗会对信号质量 产生显著的影响。

我们可以 利用眼图来

分析信号质量。

请观看 TI 精密 实验室关于这些

图的视频, 以详细了解

眼图是如何生成的。

左侧是一个来自 90 欧姆差分源的

眼图,此差分源经过 90 欧姆差分布局,

终止于 90 欧姆 差分负载。

右侧是一个来自 90 欧姆差分阻抗源的

眼图,此差分阻抗源经过 100 欧姆差分布局,

终止于 90 欧姆 差分负载。

可以将反射 造成的影响视为

左侧眼图的 闭合。

较长的 不匹配布局

会影响 整个眼图。

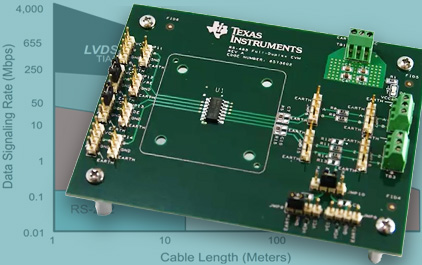

和所有高速 信号一样,应最大限度

缩短 USB 布线长度, 以减小通道损耗和防止产生噪声。

一般情况下建议 将 USB 布线长度

保持在 8 英寸以内, 以防止连接器的

信号质量下降。

10G USB 布线长度 还要再短一些。

布置长 PCB 布线时 需要非常小心,

通常建议使用 USB 转接驱动器。

有关转接驱动器 和信号调节器的

更多信息,可以在 TI 精密 实验室的“接口”部分中找到。

除了要最大限度 缩短布线长度以外,

每个差分对的 各条布线的长度

也要保持 一致,对于

USB 2.0 和 USB 3.0,此长度 不能超过 150 密耳和 5 密耳,

以防止产生噪声 并保持差分信令。

不匹配 越少越好。

SSTX 对和 SSRX 对的 布线长度

无需互相一致。

此外,超高速 信号对可以是

极性 f, 以便于路由。

当匹配 USB 信号的 路由链路时,

可以增加蛇形 路由以匹配链路,

如此处所示。

在布线中或在连接器上, 应将蛇形路由与

任何其他 不连续性

结合使用。

由于传播延迟, 不匹配的信号会导致

时序发生细微的变化。

根据经验,PCB 中的 传播延迟为

每英寸 165 皮秒。

此处显示了 微带传播延迟的

具体计算公式, 此公式得出的值略低,

约为每英寸 140 皮秒。

对于 150 密耳的 不匹配,此值

大约相当于 20 到 25 皮秒, 对于 USB 2.0

信号来说 可以忽略不计;

单位间隔为 2.08 纳秒,对于

USB 3.0 信号的 5 密耳不匹配,

此值为 8 皮秒, 对于第 1 代,

UI 为 200 皮秒。

对于更快的信号, 也需要考虑

内部接合线 不匹配情况。

在所示的表中, 对于 USB 3.0 5G 信号,

必须考虑 不匹配情况,

但对于 USB 2.0 信号, 不匹配情况无关紧要。

看一看布线 长度的影响,左侧

是一个来自仅仅 两英寸的短布线布局的

眼图。

右侧是一个来自 10 英寸的长布线

布局的眼图。

大家可以看到, 眼图张开度

减小,并对眼图的高度产生了一定影响。

这展示了布线长度 如何影响高速

信号的张开。

布线长度匹配 也可能影响

信号质量。

左侧是一个 来自匹配长度

布局的眼图,具有 小于 50 密耳的不匹配。

右侧是一个 具有 1.5 英寸

布线长度不匹配的 布局的眼图。

眼宽受到了影响。

在 USB 2.0 眼图中, 很难看出布线长度

匹配对信号 质量的影响,

因此我们创建了 一个夸张的不匹配。

左侧是一个来自 具有 50 密耳不匹配的

匹配长度布局的眼图。

右侧是一个 具有 7 英寸

布线长度不匹配的 布局的眼图。

从中可以看出 噪声明显更大的信号

对宽度产生的影响。

PCB 堆叠也会 影响 USB 信号质量。

由于 USB 具有高频率,

因此建议使用 至少四层的 PCB

堆叠在不同的 差分对中提供

实心的接地面。

左侧显示了一个 通常用在 EVM 上的

理想堆叠,具有 由一个接地层

和一个电源层 隔开的两个信号层。

应当优先布置 高速信号布线,

并将它们放在 实心接地面的顶层,

必要时也可以 放在底层,

但注意不要让它们 在电源平面分离处的上方

成直角。

如果电路非常复杂, 而且必须将信号

作为带状线布线 布置在内层上,

则应特别注意 使用接地层或电源层

将信号层隔开。

右侧显示了一个 主板堆叠示例,

所有信号层 都被接地层隔离。

如果需要在层间走线, 则应最大限度减少

通路数量。

差分对通路 应当对称并

具有配套的接地 通路,以保持接地回路

路径。

这里是一个 非理想 PCB 堆叠

以及它如何影响 信号质量的示例。

左侧是一个 来自 PCB 堆叠的眼图,

差分对布置在 实心接地面的

上方。

右侧是一个 两层 PCB 的眼图,

其中未显示实心 接地面,只使用

差分对附近的 接地填充。

总之要注意, 阻抗、布线长度和

PCB 堆叠有助于 保持信号质量、

降低误码率 以及防止

由于 USB 丢包而 影响系统吞吐量。

为了回顾我们讨论的内容, 我们来做一个小测验。

差分对的两个 信号之间的间隔

会影响差分 特性阻抗,

对还是错?

对。

差分对的两个 信号之间的间隔

会影响差分 特性阻抗,

尤其是在 微带应用中。

只要差分对的 布线长度一致,

总长度就 不会影响

信号质量,对还是错?

错。

布线越长,信号 衰减得越多。

这样会导致 眼图中的眼睛

垂直张开度减小。

差分对的 布线长度必须

完全一致, 对还是错?

错。

符合 USB 规格的 容差允许高速

信号的差分对中 存在不匹配

情况。

在可能的情况下, 应将高速差分对

布置在实心 接地面上,对还是错?

对。

应当优先布置 高速信号布线,

并将它们放在 实心接地面的顶层,

必要时也可以 放在底层,

但注意不要让它们 在电源平面分离处的上方

成直角。

关于 USB 布局基础知识的 讨论到此结束。

大家可以在我们的 TI E2E 社区中获得

有关德州仪器 TI 最新 USB 技术和解决方案的更多信息。

请访问 TI.com/e2e 获取 许多有用问题的答案

以及其他信息。

谢谢。

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论通用串行总线, 也称 USB 的布局 基础知识。 USB 是世界上最受欢迎和 使用最广泛的计算机 接口。 它应用于 各种简单和复杂的 消费性、工业 和汽车应用。 USB 设计的布局 并不复杂, 但为了保持信号 质量,需要考虑 多个因素。 在本课程中,我们将讨论 关于 USB 信号、阻抗、 布线长度和 匹配以及印刷 电路板 (PCB) 堆叠的最常见布局主题。 本课程中的示例重点 讨论 USB 2.0 高速设计, 但也适用于 USB 3.0 第 1 代和第 2 代设计。 在 USB 中,信号通过 差分信令传输。 USB 2.0 使用 单一差分 信号对、DP 和 DM。 USB 3.0 规格 增加了超高速信令, 此信令使用 SSTX 和 SSRX 这两组额外的差分信号对 来支持单独的 全双工连接。 请注意,USB 3.0 规格是累积的, 因此我们提到的 USB 3.2 规格也适用于传统 5G USB 3.0 类型的连接。 USB 2.0 规格 定义的差分 特性阻抗为 90 欧姆 ± 15%, 适用于 USB 2.0 差分对。 USB 3.0 规格定义的 差分特性阻抗 范围为 72 欧姆 到 120 欧姆。 为了优化信号质量, 应在从发送器到 PCB 布线再到 连接器和电缆 乃至下一个 连接器、PCB 布线 和接收器的 整个 USB 路径中 保持此差分阻抗。 阻抗不连续性 可能会导致信号反射 和信号质量下降。 由于我们回顾的 大多数 USB PCB 应用 都将差分信号 布置到外部 PCB 层中, 因此我们将重点 介绍微带阻抗 计算。 可以使用左侧 显示的公式来 计算差分和 单端阻抗。 如果差分信号布置 到内部 PCB 层中, 则必须使用 适用于带状线 应用的阻抗公式。 这些公式已使用 适用于 FR-4 PCB 材料的介电常数 4.4 进行简化。 4.1 到 4.5 是 用于 FR-4 材料的 典型介电 常数范围。 在这些公式中, w 是布线宽度, t 是布线厚度, d 是差分对之间的 布线距离, h 是介电 厚度。 差分阻抗 Z Diff 不到 单端阻抗 Z naught 的两倍。 差分阻抗在 很大程度上取决于 微带应用中的 布线间隔。 差分对 间隔越小, 差分阻抗越低。 阻抗会对信号质量 产生显著的影响。 我们可以 利用眼图来 分析信号质量。 请观看 TI 精密 实验室关于这些 图的视频, 以详细了解 眼图是如何生成的。 左侧是一个来自 90 欧姆差分源的 眼图,此差分源经过 90 欧姆差分布局, 终止于 90 欧姆 差分负载。 右侧是一个来自 90 欧姆差分阻抗源的 眼图,此差分阻抗源经过 100 欧姆差分布局, 终止于 90 欧姆 差分负载。 可以将反射 造成的影响视为 左侧眼图的 闭合。 较长的 不匹配布局 会影响 整个眼图。 和所有高速 信号一样,应最大限度 缩短 USB 布线长度, 以减小通道损耗和防止产生噪声。 一般情况下建议 将 USB 布线长度 保持在 8 英寸以内, 以防止连接器的 信号质量下降。 10G USB 布线长度 还要再短一些。 布置长 PCB 布线时 需要非常小心, 通常建议使用 USB 转接驱动器。 有关转接驱动器 和信号调节器的 更多信息,可以在 TI 精密 实验室的“接口”部分中找到。 除了要最大限度 缩短布线长度以外, 每个差分对的 各条布线的长度 也要保持 一致,对于 USB 2.0 和 USB 3.0,此长度 不能超过 150 密耳和 5 密耳, 以防止产生噪声 并保持差分信令。 不匹配 越少越好。 SSTX 对和 SSRX 对的 布线长度 无需互相一致。 此外,超高速 信号对可以是 极性 f, 以便于路由。 当匹配 USB 信号的 路由链路时, 可以增加蛇形 路由以匹配链路, 如此处所示。 在布线中或在连接器上, 应将蛇形路由与 任何其他 不连续性 结合使用。 由于传播延迟, 不匹配的信号会导致 时序发生细微的变化。 根据经验,PCB 中的 传播延迟为 每英寸 165 皮秒。 此处显示了 微带传播延迟的 具体计算公式, 此公式得出的值略低, 约为每英寸 140 皮秒。 对于 150 密耳的 不匹配,此值 大约相当于 20 到 25 皮秒, 对于 USB 2.0 信号来说 可以忽略不计; 单位间隔为 2.08 纳秒,对于 USB 3.0 信号的 5 密耳不匹配, 此值为 8 皮秒, 对于第 1 代, UI 为 200 皮秒。 对于更快的信号, 也需要考虑 内部接合线 不匹配情况。 在所示的表中, 对于 USB 3.0 5G 信号, 必须考虑 不匹配情况, 但对于 USB 2.0 信号, 不匹配情况无关紧要。 看一看布线 长度的影响,左侧 是一个来自仅仅 两英寸的短布线布局的 眼图。 右侧是一个来自 10 英寸的长布线 布局的眼图。 大家可以看到, 眼图张开度 减小,并对眼图的高度产生了一定影响。 这展示了布线长度 如何影响高速 信号的张开。 布线长度匹配 也可能影响 信号质量。 左侧是一个 来自匹配长度 布局的眼图,具有 小于 50 密耳的不匹配。 右侧是一个 具有 1.5 英寸 布线长度不匹配的 布局的眼图。 眼宽受到了影响。 在 USB 2.0 眼图中, 很难看出布线长度 匹配对信号 质量的影响, 因此我们创建了 一个夸张的不匹配。 左侧是一个来自 具有 50 密耳不匹配的 匹配长度布局的眼图。 右侧是一个 具有 7 英寸 布线长度不匹配的 布局的眼图。 从中可以看出 噪声明显更大的信号 对宽度产生的影响。 PCB 堆叠也会 影响 USB 信号质量。 由于 USB 具有高频率, 因此建议使用 至少四层的 PCB 堆叠在不同的 差分对中提供 实心的接地面。 左侧显示了一个 通常用在 EVM 上的 理想堆叠,具有 由一个接地层 和一个电源层 隔开的两个信号层。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 如果电路非常复杂, 而且必须将信号 作为带状线布线 布置在内层上, 则应特别注意 使用接地层或电源层 将信号层隔开。 右侧显示了一个 主板堆叠示例, 所有信号层 都被接地层隔离。 如果需要在层间走线, 则应最大限度减少 通路数量。 差分对通路 应当对称并 具有配套的接地 通路,以保持接地回路 路径。 这里是一个 非理想 PCB 堆叠 以及它如何影响 信号质量的示例。 左侧是一个 来自 PCB 堆叠的眼图, 差分对布置在 实心接地面的 上方。 右侧是一个 两层 PCB 的眼图, 其中未显示实心 接地面,只使用 差分对附近的 接地填充。 总之要注意, 阻抗、布线长度和 PCB 堆叠有助于 保持信号质量、 降低误码率 以及防止 由于 USB 丢包而 影响系统吞吐量。 为了回顾我们讨论的内容, 我们来做一个小测验。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 对还是错? 对。 差分对的两个 信号之间的间隔 会影响差分 特性阻抗, 尤其是在 微带应用中。 只要差分对的 布线长度一致, 总长度就 不会影响 信号质量,对还是错? 错。 布线越长,信号 衰减得越多。 这样会导致 眼图中的眼睛 垂直张开度减小。 差分对的 布线长度必须 完全一致, 对还是错? 错。 符合 USB 规格的 容差允许高速 信号的差分对中 存在不匹配 情况。 在可能的情况下, 应将高速差分对 布置在实心 接地面上,对还是错? 对。 应当优先布置 高速信号布线, 并将它们放在 实心接地面的顶层, 必要时也可以 放在底层, 但注意不要让它们 在电源平面分离处的上方 成直角。 关于 USB 布局基础知识的 讨论到此结束。 大家可以在我们的 TI E2E 社区中获得 有关德州仪器 TI 最新 USB 技术和解决方案的更多信息。 请访问 TI.com/e2e 获取 许多有用问题的答案 以及其他信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。

在本系列中,我们将 讨论通用串行总线,

也称 USB 的布局 基础知识。

USB 是世界上最受欢迎和 使用最广泛的计算机

接口。

它应用于 各种简单和复杂的

消费性、工业 和汽车应用。

USB 设计的布局 并不复杂,

但为了保持信号 质量,需要考虑

多个因素。

在本课程中,我们将讨论 关于 USB 信号、阻抗、

布线长度和 匹配以及印刷

电路板 (PCB) 堆叠的最常见布局主题。

本课程中的示例重点 讨论 USB 2.0 高速设计,

但也适用于 USB 3.0 第 1 代和第 2 代设计。

在 USB 中,信号通过 差分信令传输。

USB 2.0 使用 单一差分

信号对、DP 和 DM。

USB 3.0 规格 增加了超高速信令,

此信令使用 SSTX 和 SSRX 这两组额外的差分信号对

来支持单独的 全双工连接。

请注意,USB 3.0 规格是累积的,

因此我们提到的 USB 3.2 规格也适用于传统

5G USB 3.0 类型的连接。

USB 2.0 规格 定义的差分

特性阻抗为 90 欧姆 ± 15%,

适用于 USB 2.0 差分对。

USB 3.0 规格定义的

差分特性阻抗 范围为 72 欧姆

到 120 欧姆。

为了优化信号质量, 应在从发送器到

PCB 布线再到 连接器和电缆

乃至下一个 连接器、PCB 布线

和接收器的 整个 USB 路径中

保持此差分阻抗。

阻抗不连续性 可能会导致信号反射

和信号质量下降。

由于我们回顾的 大多数 USB PCB 应用

都将差分信号 布置到外部 PCB 层中,

因此我们将重点 介绍微带阻抗

计算。

可以使用左侧 显示的公式来

计算差分和 单端阻抗。

如果差分信号布置 到内部 PCB 层中,

则必须使用 适用于带状线

应用的阻抗公式。

这些公式已使用 适用于 FR-4 PCB

材料的介电常数 4.4 进行简化。

4.1 到 4.5 是 用于 FR-4 材料的

典型介电 常数范围。

在这些公式中, w 是布线宽度,

t 是布线厚度, d 是差分对之间的

布线距离, h 是介电

厚度。

差分阻抗 Z Diff 不到

单端阻抗 Z naught 的两倍。

差分阻抗在 很大程度上取决于

微带应用中的 布线间隔。

差分对 间隔越小,

差分阻抗越低。

阻抗会对信号质量 产生显著的影响。

我们可以 利用眼图来

分析信号质量。

请观看 TI 精密 实验室关于这些

图的视频, 以详细了解

眼图是如何生成的。

左侧是一个来自 90 欧姆差分源的

眼图,此差分源经过 90 欧姆差分布局,

终止于 90 欧姆 差分负载。

右侧是一个来自 90 欧姆差分阻抗源的

眼图,此差分阻抗源经过 100 欧姆差分布局,

终止于 90 欧姆 差分负载。

可以将反射 造成的影响视为

左侧眼图的 闭合。

较长的 不匹配布局

会影响 整个眼图。

和所有高速 信号一样,应最大限度

缩短 USB 布线长度, 以减小通道损耗和防止产生噪声。

一般情况下建议 将 USB 布线长度

保持在 8 英寸以内, 以防止连接器的

信号质量下降。

10G USB 布线长度 还要再短一些。

布置长 PCB 布线时 需要非常小心,

通常建议使用 USB 转接驱动器。

有关转接驱动器 和信号调节器的

更多信息,可以在 TI 精密 实验室的“接口”部分中找到。

除了要最大限度 缩短布线长度以外,

每个差分对的 各条布线的长度

也要保持 一致,对于

USB 2.0 和 USB 3.0,此长度 不能超过 150 密耳和 5 密耳,

以防止产生噪声 并保持差分信令。

不匹配 越少越好。

SSTX 对和 SSRX 对的 布线长度

无需互相一致。

此外,超高速 信号对可以是

极性 f, 以便于路由。

当匹配 USB 信号的 路由链路时,

可以增加蛇形 路由以匹配链路,

如此处所示。

在布线中或在连接器上, 应将蛇形路由与

任何其他 不连续性

结合使用。

由于传播延迟, 不匹配的信号会导致

时序发生细微的变化。

根据经验,PCB 中的 传播延迟为

每英寸 165 皮秒。

此处显示了 微带传播延迟的

具体计算公式, 此公式得出的值略低,

约为每英寸 140 皮秒。

对于 150 密耳的 不匹配,此值

大约相当于 20 到 25 皮秒, 对于 USB 2.0

信号来说 可以忽略不计;

单位间隔为 2.08 纳秒,对于

USB 3.0 信号的 5 密耳不匹配,

此值为 8 皮秒, 对于第 1 代,

UI 为 200 皮秒。

对于更快的信号, 也需要考虑

内部接合线 不匹配情况。

在所示的表中, 对于 USB 3.0 5G 信号,

必须考虑 不匹配情况,

但对于 USB 2.0 信号, 不匹配情况无关紧要。

看一看布线 长度的影响,左侧

是一个来自仅仅 两英寸的短布线布局的

眼图。

右侧是一个来自 10 英寸的长布线

布局的眼图。

大家可以看到, 眼图张开度

减小,并对眼图的高度产生了一定影响。

这展示了布线长度 如何影响高速

信号的张开。

布线长度匹配 也可能影响

信号质量。

左侧是一个 来自匹配长度

布局的眼图,具有 小于 50 密耳的不匹配。

右侧是一个 具有 1.5 英寸

布线长度不匹配的 布局的眼图。

眼宽受到了影响。

在 USB 2.0 眼图中, 很难看出布线长度

匹配对信号 质量的影响,

因此我们创建了 一个夸张的不匹配。

左侧是一个来自 具有 50 密耳不匹配的

匹配长度布局的眼图。

右侧是一个 具有 7 英寸

布线长度不匹配的 布局的眼图。

从中可以看出 噪声明显更大的信号

对宽度产生的影响。

PCB 堆叠也会 影响 USB 信号质量。

由于 USB 具有高频率,

因此建议使用 至少四层的 PCB

堆叠在不同的 差分对中提供

实心的接地面。

左侧显示了一个 通常用在 EVM 上的

理想堆叠,具有 由一个接地层

和一个电源层 隔开的两个信号层。

应当优先布置 高速信号布线,

并将它们放在 实心接地面的顶层,

必要时也可以 放在底层,

但注意不要让它们 在电源平面分离处的上方

成直角。

如果电路非常复杂, 而且必须将信号

作为带状线布线 布置在内层上,

则应特别注意 使用接地层或电源层

将信号层隔开。

右侧显示了一个 主板堆叠示例,

所有信号层 都被接地层隔离。

如果需要在层间走线, 则应最大限度减少

通路数量。

差分对通路 应当对称并

具有配套的接地 通路,以保持接地回路

路径。

这里是一个 非理想 PCB 堆叠

以及它如何影响 信号质量的示例。

左侧是一个 来自 PCB 堆叠的眼图,

差分对布置在 实心接地面的

上方。

右侧是一个 两层 PCB 的眼图,

其中未显示实心 接地面,只使用

差分对附近的 接地填充。

总之要注意, 阻抗、布线长度和

PCB 堆叠有助于 保持信号质量、

降低误码率 以及防止

由于 USB 丢包而 影响系统吞吐量。

为了回顾我们讨论的内容, 我们来做一个小测验。

差分对的两个 信号之间的间隔

会影响差分 特性阻抗,

对还是错?

对。

差分对的两个 信号之间的间隔

会影响差分 特性阻抗,

尤其是在 微带应用中。

只要差分对的 布线长度一致,

总长度就 不会影响

信号质量,对还是错?

错。

布线越长,信号 衰减得越多。

这样会导致 眼图中的眼睛

垂直张开度减小。

差分对的 布线长度必须

完全一致, 对还是错?

错。

符合 USB 规格的 容差允许高速

信号的差分对中 存在不匹配

情况。

在可能的情况下, 应将高速差分对

布置在实心 接地面上,对还是错?

对。

应当优先布置 高速信号布线,

并将它们放在 实心接地面的顶层,

必要时也可以 放在底层,

但注意不要让它们 在电源平面分离处的上方

成直角。

关于 USB 布局基础知识的 讨论到此结束。

大家可以在我们的 TI E2E 社区中获得

有关德州仪器 TI 最新 USB 技术和解决方案的更多信息。

请访问 TI.com/e2e 获取 许多有用问题的答案

以及其他信息。

谢谢。

手机看

扫码用手机观看

视频简介

视频简介

10.1 TI 高精度实验室 - USB:USB 设计的布局基础知识

所属课程:TI 高精度实验室 - USB

发布时间:2020.02.13

视频集数:3

本节视频时长:00:11:15

该视频介绍了USB信号最常见的布局主题:阻抗,走线长度和匹配以及印刷电路板(PCB)堆叠。

未学习 10.1 TI 高精度实验室 - USB:USB 设计的布局基础知识

未学习 10.1 TI 高精度实验室 - USB:USB 设计的布局基础知识

未学习 10.2 TI 高精度实验室 - USB:什么是USB转接驱动器

未学习 10.2 TI 高精度实验室 - USB:什么是USB转接驱动器

未学习 10.3 TI 高精度实验室 - USB:什么是嵌入式 USB2.0 (eUSB2)?

未学习 10.3 TI 高精度实验室 - USB:什么是嵌入式 USB2.0 (eUSB2)?

视频简介

视频简介