9.2 TI 高精度实验室 - 视频接口:什么是显示端口(DP)?

Loading the player...

将在30s后自动为您播放下一课程

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论 DisplayPort 接口, 也称为 DP。 DP 是一种 数字显示接口, 是在 2008 年作为 新一代显示接口推出的。 这种接口旨在取代 旧的显示标准,例如 VGA 和 DVI,并为 个人计算、数字 显示和消费类 电子产品打开 一扇新的大门。 DisplayPort 2.0 支持两个具有 120 赫兹 刷新率、30bpp 和 HDR 的 8K 显示屏或者两个 具有 144 赫兹刷新率和 24bpp、无压缩的 4K 显示屏。 DisplayPort 还兼容 传统的显示屏 连接。 添加了一个 简单的适配器之后, DP 电缆可以 将 DP 拉电流 连接到传统 VGA、单链路 DVI 或 HDMI 显示屏。 任何 DisplayPort的 源端和目的端 都由 3 个 主要部分组成: 主链路、 辅助通道和 热插拔检测,简称 HPD。 主链路用于 传输视频。 主链路包含单向 串行数据通道, 这些通道被称为信道。 辅助通道 是 1 兆位/秒的 半双工、 双向数据 通道,用于传输 控制和状态信息。 HPD 是由灌电流 为拉电流提供的 3.3 伏信号。 HPD 有两个用途, 这两个用途对于启动 拉电流发送器与灌电流 接收器之间的 DisplayPort 通信 链路至关重要。 首先,HPD 可 通知是否存在 灌电流。 当 HPD 较高或者 为 3.3 伏时, 表明存在 灌电流。 当 HPD 较低或者为 0 并 持续 2 毫秒以上时, 表明灌电流 不存在或已消除。 其次,HPD 可用作 从灌电流到 拉电流的中断。 当 HPD 较低或者在 0.5 到 1 毫秒内为 0 时, 表明发生了 中断事件。 灌电流请求拉电流 使用辅助接口读取 灌电流的 DPCD 寄存器 并采取适当的行动。 辅助接口是一个 数据速率为 1 兆位/秒的 双向、半双工 差分接口。 当灌电流被接通 并使用 VESA、EDID 和 VESA MCCS 标准 为主链路传送 管理和器件控制数据时, 即开始进行辅助通信。 在标准 DP 连接中,每个信道 都有一组专用的 双绞线,并利用 差分信令通过这些 双绞线传输数据。 对于 DP 连接,没有 专用的时钟通道, 因为时钟 嵌入到数据中。 DisplayPort 只以 特定的数据速率运行。 DisplayPort 2.0 标准 为主链路定义了 7 种数据速率-- 1.62 千兆位/秒 ,简称 RBR;2.7 千兆位/秒, 简称 HBR; 5.4 千兆位/秒,简称 HBR2; 8.1 千兆位/秒, 简称 HBR3;10 千兆位/秒, 简称 UHBR10; 13.5 千兆位/秒,简称 UHBR13.5; 以及 20 千兆位/秒, ,简称 UHBR20。 当数据速率从 1.62 千兆位/秒提高到 8.1 千兆位/秒时, DP 主链路将 开始出现 信号失真, 这是由封装和 PCB 的 铜损和介电损耗造成的。 结果是, 随着数据速率提高, 主链路长度会缩短。 为了支持更长的 主链路长度, 需要在系统设计 期间考虑以转接 驱动器或 重定时器 形式添加 一个 DP 信号 调节器。 DP 使用 LVDS 信号协议。 它是一个交流耦合、 100 欧姆的差分 信号接口。 在拉电流侧, 发送器 既提供振幅控制, 也提供预加重的 控制。 发送器必须 支持电平 0、电平 1 和电平 2 振幅控制以及 预加重的控制, 电平 3 是可选的。 拉电流处的默认 信号振幅为 400 毫伏峰间值。 默认的 预加重电平为 0dB。 链路协商 用于补偿 DP 拉电流与 DP 灌电流 之间的信号完整性。 补偿通过在 初始灌电流连接 期间按照灌电流的 请求更改 DP 拉电流 振幅和预加重 电平来完成。 如果在初始 灌电流连接之后 发生数据错误,也可以 对补偿进行重新初始化。 当数据速率从 1.62 千兆位/秒 提高到 8.1 千兆位/秒之后,主链路 开始出现 信号失真, 这是由 PCB 和封装的 铜损和介电损耗造成的。 由于主链路中的 阻抗不连续性, 其他组件也可能出现失真, 例如封装、通道和连接器。 数据速率的 提高速度比 目前的接收器设计 发展速度更快,而 PCB 或封装技术能够 与其齐头并进。 虽然使用昂贵的 PCB 材料可以减小 这一损耗, 但 PCB 材料 会很快达到 介电限值 而且成本高昂。 第二种解决方案是 缩短主链路长度, 从而减小 总损耗。 但在需要更长主链路 长度的 DP 系统设计中, 这种解决方案 不切实际,而且 需要以更高的 数据速率运行。 位于主链路上的 拉电流与连接器之间, 或者连接器 与灌电流之间的转接 驱动器或重定时器 有助于克服这一设计挑战。 转接驱动器可 通过均衡和增益 调节来恢复 衰减的输入信号, 因此有助于提高 主链路的信号质量。 重定时器可使用 时钟恢复电路来 恢复衰减的 输入信号、 补偿随机抖动 以及基于纯净的时钟来 重新传输信号。 有关信号调节器的 更多信息, 建议大家观看 TI 高精度实验室推出的 名为“什么是信号调节器”的视频。 在系统设计中,确定 转接驱动器的位置 至关重要。 如果将转接驱动器 放在过于靠近或远离拉电流 发送器或灌电流 接收器的位置, 会对转接驱动器的 有效性产生负面影响, 从而导致系统 性能欠佳。 转接驱动器的 位置取决于 转接驱动器接收器均衡器 之前的系统总计插入损耗。 插入损耗 来自于 PCB 迹线、通道、连接器、 器件封装等等。 如果能够估算出 PCB 迹线的 奈奎斯特区域中的 插入损耗,就可以 计算出 PCB 迹线 长度是否处于 转接驱动器接收器 设计限制内, 并获得初步的转接 驱动器均衡器设置 估算值。 假设皮肤深度限制了 微带或带状线中的 电流、回路中使用 串联电阻、 表面粗糙度 导致电阻系数 增大 2 而且 传输线路的阻抗 为 100 欧姆,那么我们 就可以利用模型 公式合理地估算 奈奎斯特频率的 插入损耗。 在此模型公式中,w 是 以密耳为单位的迹线宽度。 f 是奈奎斯特频率。 Df 是 PCB 损耗系数。 Dk 是 PCB 介电常数。 现在来执行 实际计算。 假设 DP 以 HBR2 或 5.4 千兆位/秒的 速率运行。 奈奎斯特频率 f 为数据速率的 1/2 或 2.7GHz。 对于 12 英寸、6 密耳迹线, 损耗系数为 0.02, 介电常数 为 4.3。 这样,我们就可以 估算出在频率为 2.7GHz 时的损耗 大约为 0.53dB。 将 12 英寸 乘以每英寸 0.53dB, 即可得出频率为 2.7GHz 时, 插入损耗约为 6.36 dB。 此值非常接近于 VNA 在频率为 2.7GHz 时 在 12 英寸、6 密耳的 实际迹线中测得的 6.54dB。 假设转接驱动器 在频率为 2.7GHz 时 支持最多 12dB 的损耗, 那么使用估算出的 每英寸 0.53dB 损耗, 就可以得出 HBR2 支持的 最长距离 约为 22 英寸。 此估算值也可以 用来配置转接驱动器 均衡设置。 假设将转接驱动器放在 与同一块电路板上的 信号源相距 10 英寸的位置, 我们就可以利用 这个估算出的损耗 将初始转接驱动器 均衡器设置为 5dB。 可以通过 DisplayPort 合规性测试 完成进一步的 调优。 在拉电流 发送器侧,可以通过 发送器电气 合规性测试来 完成此操作。 而在接收器 灌电流侧,可以通过 接收器抖动容差 测试来完成此操作。 现在,我们来 看一个实际示例。 在观察此 眼图之前, 请观看 TI 高精度 实验室的“什么是眼图?” 演示,以便对 眼图有一个基本的 了解。 第一张图片是 拉电流发送器 输出端的 HBR2 5.4 千兆位/秒 眼图。 眼睛是张开的,因此 通过了 DisplayPort 眼罩 要求。 将迹线 延长 12 英寸, 现在可以看到眼睛 闭上了,因此未通过 DisplayPort 眼罩要求。 从刚刚执行的 计算可知, 每英寸的插入 损耗约为 0.53dB。 对于 12 英寸迹线, 在频率为 2.7GHz 时的 损耗为 6.36dB。 如果在 12 英寸 迹线的输出端 添加一个转接驱动器,并将 转接驱动器均衡器设置为 6dB, 以匹配 12 英寸 迹线的插入损耗, 我们就会发现眼睛 再次张开,并通过了 DisplayPort 眼罩要求。 为了回顾我们讨论的内容, 我们来做一个小测验。 问题 1,判断对错 DP 是一个直流耦合接口。 错。 问题 2 ,判断对错 对于 8.1 千兆位/秒的 数据速率和双通道 配置, 总带宽为 16.2 千兆位/秒。 对。 问题 3 ,判断对错 热插拔检测功能 用于配置 DP 通道。 错。 问题 4 ,判断对错 插入损耗 与 DP 数据速率无关。 错。 问题 5 ,判断对错 DP 转接驱动器有助于 提高 DP 主链路信号 质量。 对。 问题 6 ,判断对错 将 DP 转接驱动器 放在正确的位置 对系统设计 非常重要。 对。 最后,很高兴 为大家介绍 关于 DisplayPort 的这部分信息。 敬请关注以后的课程。 我们将详细介绍 德州仪器 (TI) 推出的 标准和信号 调节器件。 请务必访问我们的 TI E2E 社区 TI.com, 以获得问题解答 和更多信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论 DisplayPort 接口, 也称为 DP。 DP 是一种 数字显示接口, 是在 2008 年作为 新一代显示接口推出的。 这种接口旨在取代 旧的显示标准,例如 VGA 和 DVI,并为 个人计算、数字 显示和消费类 电子产品打开 一扇新的大门。 DisplayPort 2.0 支持两个具有 120 赫兹 刷新率、30bpp 和 HDR 的 8K 显示屏或者两个 具有 144 赫兹刷新率和 24bpp、无压缩的 4K 显示屏。 DisplayPort 还兼容 传统的显示屏 连接。 添加了一个 简单的适配器之后, DP 电缆可以 将 DP 拉电流 连接到传统 VGA、单链路 DVI 或 HDMI 显示屏。 任何 DisplayPort的 源端和目的端 都由 3 个 主要部分组成: 主链路、 辅助通道和 热插拔检测,简称 HPD。 主链路用于 传输视频。 主链路包含单向 串行数据通道, 这些通道被称为信道。 辅助通道 是 1 兆位/秒的 半双工、 双向数据 通道,用于传输 控制和状态信息。 HPD 是由灌电流 为拉电流提供的 3.3 伏信号。 HPD 有两个用途, 这两个用途对于启动 拉电流发送器与灌电流 接收器之间的 DisplayPort 通信 链路至关重要。 首先,HPD 可 通知是否存在 灌电流。 当 HPD 较高或者 为 3.3 伏时, 表明存在 灌电流。 当 HPD 较低或者为 0 并 持续 2 毫秒以上时, 表明灌电流 不存在或已消除。 其次,HPD 可用作 从灌电流到 拉电流的中断。 当 HPD 较低或者在 0.5 到 1 毫秒内为 0 时, 表明发生了 中断事件。 灌电流请求拉电流 使用辅助接口读取 灌电流的 DPCD 寄存器 并采取适当的行动。 辅助接口是一个 数据速率为 1 兆位/秒的 双向、半双工 差分接口。 当灌电流被接通 并使用 VESA、EDID 和 VESA MCCS 标准 为主链路传送 管理和器件控制数据时, 即开始进行辅助通信。 在标准 DP 连接中,每个信道 都有一组专用的 双绞线,并利用 差分信令通过这些 双绞线传输数据。 对于 DP 连接,没有 专用的时钟通道, 因为时钟 嵌入到数据中。 DisplayPort 只以 特定的数据速率运行。 DisplayPort 2.0 标准 为主链路定义了 7 种数据速率-- 1.62 千兆位/秒 ,简称 RBR;2.7 千兆位/秒, 简称 HBR; 5.4 千兆位/秒,简称 HBR2; 8.1 千兆位/秒, 简称 HBR3;10 千兆位/秒, 简称 UHBR10; 13.5 千兆位/秒,简称 UHBR13.5; 以及 20 千兆位/秒, ,简称 UHBR20。 当数据速率从 1.62 千兆位/秒提高到 8.1 千兆位/秒时, DP 主链路将 开始出现 信号失真, 这是由封装和 PCB 的 铜损和介电损耗造成的。 结果是, 随着数据速率提高, 主链路长度会缩短。 为了支持更长的 主链路长度, 需要在系统设计 期间考虑以转接 驱动器或 重定时器 形式添加 一个 DP 信号 调节器。 DP 使用 LVDS 信号协议。 它是一个交流耦合、 100 欧姆的差分 信号接口。 在拉电流侧, 发送器 既提供振幅控制, 也提供预加重的 控制。 发送器必须 支持电平 0、电平 1 和电平 2 振幅控制以及 预加重的控制, 电平 3 是可选的。 拉电流处的默认 信号振幅为 400 毫伏峰间值。 默认的 预加重电平为 0dB。 链路协商 用于补偿 DP 拉电流与 DP 灌电流 之间的信号完整性。 补偿通过在 初始灌电流连接 期间按照灌电流的 请求更改 DP 拉电流 振幅和预加重 电平来完成。 如果在初始 灌电流连接之后 发生数据错误,也可以 对补偿进行重新初始化。 当数据速率从 1.62 千兆位/秒 提高到 8.1 千兆位/秒之后,主链路 开始出现 信号失真, 这是由 PCB 和封装的 铜损和介电损耗造成的。 由于主链路中的 阻抗不连续性, 其他组件也可能出现失真, 例如封装、通道和连接器。 数据速率的 提高速度比 目前的接收器设计 发展速度更快,而 PCB 或封装技术能够 与其齐头并进。 虽然使用昂贵的 PCB 材料可以减小 这一损耗, 但 PCB 材料 会很快达到 介电限值 而且成本高昂。 第二种解决方案是 缩短主链路长度, 从而减小 总损耗。 但在需要更长主链路 长度的 DP 系统设计中, 这种解决方案 不切实际,而且 需要以更高的 数据速率运行。 位于主链路上的 拉电流与连接器之间, 或者连接器 与灌电流之间的转接 驱动器或重定时器 有助于克服这一设计挑战。 转接驱动器可 通过均衡和增益 调节来恢复 衰减的输入信号, 因此有助于提高 主链路的信号质量。 重定时器可使用 时钟恢复电路来 恢复衰减的 输入信号、 补偿随机抖动 以及基于纯净的时钟来 重新传输信号。 有关信号调节器的 更多信息, 建议大家观看 TI 高精度实验室推出的 名为“什么是信号调节器”的视频。 在系统设计中,确定 转接驱动器的位置 至关重要。 如果将转接驱动器 放在过于靠近或远离拉电流 发送器或灌电流 接收器的位置, 会对转接驱动器的 有效性产生负面影响, 从而导致系统 性能欠佳。 转接驱动器的 位置取决于 转接驱动器接收器均衡器 之前的系统总计插入损耗。 插入损耗 来自于 PCB 迹线、通道、连接器、 器件封装等等。 如果能够估算出 PCB 迹线的 奈奎斯特区域中的 插入损耗,就可以 计算出 PCB 迹线 长度是否处于 转接驱动器接收器 设计限制内, 并获得初步的转接 驱动器均衡器设置 估算值。 假设皮肤深度限制了 微带或带状线中的 电流、回路中使用 串联电阻、 表面粗糙度 导致电阻系数 增大 2 而且 传输线路的阻抗 为 100 欧姆,那么我们 就可以利用模型 公式合理地估算 奈奎斯特频率的 插入损耗。 在此模型公式中,w 是 以密耳为单位的迹线宽度。 f 是奈奎斯特频率。 Df 是 PCB 损耗系数。 Dk 是 PCB 介电常数。 现在来执行 实际计算。 假设 DP 以 HBR2 或 5.4 千兆位/秒的 速率运行。 奈奎斯特频率 f 为数据速率的 1/2 或 2.7GHz。 对于 12 英寸、6 密耳迹线, 损耗系数为 0.02, 介电常数 为 4.3。 这样,我们就可以 估算出在频率为 2.7GHz 时的损耗 大约为 0.53dB。 将 12 英寸 乘以每英寸 0.53dB, 即可得出频率为 2.7GHz 时, 插入损耗约为 6.36 dB。 此值非常接近于 VNA 在频率为 2.7GHz 时 在 12 英寸、6 密耳的 实际迹线中测得的 6.54dB。 假设转接驱动器 在频率为 2.7GHz 时 支持最多 12dB 的损耗, 那么使用估算出的 每英寸 0.53dB 损耗, 就可以得出 HBR2 支持的 最长距离 约为 22 英寸。 此估算值也可以 用来配置转接驱动器 均衡设置。 假设将转接驱动器放在 与同一块电路板上的 信号源相距 10 英寸的位置, 我们就可以利用 这个估算出的损耗 将初始转接驱动器 均衡器设置为 5dB。 可以通过 DisplayPort 合规性测试 完成进一步的 调优。 在拉电流 发送器侧,可以通过 发送器电气 合规性测试来 完成此操作。 而在接收器 灌电流侧,可以通过 接收器抖动容差 测试来完成此操作。 现在,我们来 看一个实际示例。 在观察此 眼图之前, 请观看 TI 高精度 实验室的“什么是眼图?” 演示,以便对 眼图有一个基本的 了解。 第一张图片是 拉电流发送器 输出端的 HBR2 5.4 千兆位/秒 眼图。 眼睛是张开的,因此 通过了 DisplayPort 眼罩 要求。 将迹线 延长 12 英寸, 现在可以看到眼睛 闭上了,因此未通过 DisplayPort 眼罩要求。 从刚刚执行的 计算可知, 每英寸的插入 损耗约为 0.53dB。 对于 12 英寸迹线, 在频率为 2.7GHz 时的 损耗为 6.36dB。 如果在 12 英寸 迹线的输出端 添加一个转接驱动器,并将 转接驱动器均衡器设置为 6dB, 以匹配 12 英寸 迹线的插入损耗, 我们就会发现眼睛 再次张开,并通过了 DisplayPort 眼罩要求。 为了回顾我们讨论的内容, 我们来做一个小测验。 问题 1,判断对错 DP 是一个直流耦合接口。 错。 问题 2 ,判断对错 对于 8.1 千兆位/秒的 数据速率和双通道 配置, 总带宽为 16.2 千兆位/秒。 对。 问题 3 ,判断对错 热插拔检测功能 用于配置 DP 通道。 错。 问题 4 ,判断对错 插入损耗 与 DP 数据速率无关。 错。 问题 5 ,判断对错 DP 转接驱动器有助于 提高 DP 主链路信号 质量。 对。 问题 6 ,判断对错 将 DP 转接驱动器 放在正确的位置 对系统设计 非常重要。 对。 最后,很高兴 为大家介绍 关于 DisplayPort 的这部分信息。 敬请关注以后的课程。 我们将详细介绍 德州仪器 (TI) 推出的 标准和信号 调节器件。 请务必访问我们的 TI E2E 社区 TI.com, 以获得问题解答 和更多信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。

在本系列中,我们将 讨论 DisplayPort 接口,

也称为 DP。

DP 是一种 数字显示接口,

是在 2008 年作为 新一代显示接口推出的。

这种接口旨在取代 旧的显示标准,例如 VGA

和 DVI,并为 个人计算、数字

显示和消费类 电子产品打开

一扇新的大门。

DisplayPort 2.0 支持两个具有 120 赫兹

刷新率、30bpp 和 HDR 的 8K 显示屏或者两个

具有 144 赫兹刷新率和 24bpp、无压缩的 4K 显示屏。

DisplayPort 还兼容 传统的显示屏

连接。

添加了一个 简单的适配器之后,

DP 电缆可以 将 DP 拉电流

连接到传统 VGA、单链路 DVI 或 HDMI 显示屏。

任何 DisplayPort的 源端和目的端

都由 3 个 主要部分组成:

主链路、 辅助通道和

热插拔检测,简称 HPD。

主链路用于 传输视频。

主链路包含单向 串行数据通道,

这些通道被称为信道。

辅助通道 是 1 兆位/秒的

半双工、 双向数据

通道,用于传输 控制和状态信息。

HPD 是由灌电流 为拉电流提供的

3.3 伏信号。

HPD 有两个用途, 这两个用途对于启动

拉电流发送器与灌电流 接收器之间的 DisplayPort 通信

链路至关重要。

首先,HPD 可 通知是否存在

灌电流。

当 HPD 较高或者 为 3.3 伏时,

表明存在 灌电流。

当 HPD 较低或者为 0 并 持续 2 毫秒以上时,

表明灌电流 不存在或已消除。

其次,HPD 可用作 从灌电流到

拉电流的中断。

当 HPD 较低或者在 0.5 到 1 毫秒内为 0 时,

表明发生了 中断事件。

灌电流请求拉电流 使用辅助接口读取

灌电流的 DPCD 寄存器 并采取适当的行动。

辅助接口是一个 数据速率为 1 兆位/秒的

双向、半双工 差分接口。

当灌电流被接通 并使用 VESA、EDID 和

VESA MCCS 标准 为主链路传送

管理和器件控制数据时, 即开始进行辅助通信。

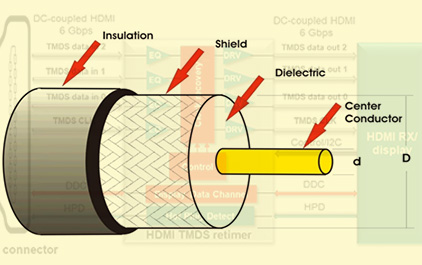

在标准 DP 连接中,每个信道

都有一组专用的 双绞线,并利用

差分信令通过这些 双绞线传输数据。

对于 DP 连接,没有 专用的时钟通道,

因为时钟 嵌入到数据中。

DisplayPort 只以 特定的数据速率运行。

DisplayPort 2.0 标准 为主链路定义了

7 种数据速率--

1.62 千兆位/秒 ,简称 RBR;2.7 千兆位/秒,

简称 HBR; 5.4 千兆位/秒,简称 HBR2;

8.1 千兆位/秒, 简称 HBR3;10 千兆位/秒,

简称 UHBR10; 13.5 千兆位/秒,简称 UHBR13.5;

以及 20 千兆位/秒, ,简称 UHBR20。

当数据速率从 1.62 千兆位/秒提高到

8.1 千兆位/秒时, DP 主链路将

开始出现 信号失真,

这是由封装和 PCB 的 铜损和介电损耗造成的。

结果是, 随着数据速率提高,

主链路长度会缩短。

为了支持更长的 主链路长度,

需要在系统设计 期间考虑以转接

驱动器或 重定时器

形式添加 一个 DP 信号

调节器。

DP 使用 LVDS 信号协议。

它是一个交流耦合、 100 欧姆的差分

信号接口。

在拉电流侧, 发送器

既提供振幅控制, 也提供预加重的

控制。

发送器必须 支持电平 0、电平 1

和电平 2 振幅控制以及 预加重的控制,

电平 3 是可选的。

拉电流处的默认 信号振幅为

400 毫伏峰间值。

默认的 预加重电平为 0dB。

链路协商 用于补偿

DP 拉电流与 DP 灌电流 之间的信号完整性。

补偿通过在 初始灌电流连接

期间按照灌电流的 请求更改 DP 拉电流

振幅和预加重 电平来完成。

如果在初始 灌电流连接之后

发生数据错误,也可以 对补偿进行重新初始化。

当数据速率从 1.62 千兆位/秒

提高到 8.1 千兆位/秒之后,主链路

开始出现 信号失真,

这是由 PCB 和封装的

铜损和介电损耗造成的。

由于主链路中的 阻抗不连续性,

其他组件也可能出现失真, 例如封装、通道和连接器。

数据速率的 提高速度比

目前的接收器设计 发展速度更快,而 PCB

或封装技术能够 与其齐头并进。

虽然使用昂贵的 PCB 材料可以减小

这一损耗, 但 PCB 材料

会很快达到 介电限值

而且成本高昂。

第二种解决方案是 缩短主链路长度,

从而减小 总损耗。

但在需要更长主链路 长度的 DP 系统设计中,

这种解决方案 不切实际,而且

需要以更高的 数据速率运行。

位于主链路上的

拉电流与连接器之间,

或者连接器 与灌电流之间的转接

驱动器或重定时器 有助于克服这一设计挑战。

转接驱动器可 通过均衡和增益

调节来恢复 衰减的输入信号,

因此有助于提高 主链路的信号质量。

重定时器可使用 时钟恢复电路来

恢复衰减的 输入信号、

补偿随机抖动 以及基于纯净的时钟来

重新传输信号。

有关信号调节器的 更多信息,

建议大家观看 TI 高精度实验室推出的

名为“什么是信号调节器”的视频。

在系统设计中,确定 转接驱动器的位置

至关重要。

如果将转接驱动器 放在过于靠近或远离拉电流

发送器或灌电流 接收器的位置,

会对转接驱动器的 有效性产生负面影响,

从而导致系统 性能欠佳。

转接驱动器的 位置取决于

转接驱动器接收器均衡器 之前的系统总计插入损耗。

插入损耗 来自于 PCB

迹线、通道、连接器、 器件封装等等。

如果能够估算出 PCB 迹线的

奈奎斯特区域中的 插入损耗,就可以

计算出 PCB 迹线 长度是否处于

转接驱动器接收器 设计限制内,

并获得初步的转接 驱动器均衡器设置

估算值。

假设皮肤深度限制了 微带或带状线中的

电流、回路中使用 串联电阻、

表面粗糙度 导致电阻系数

增大 2 而且 传输线路的阻抗

为 100 欧姆,那么我们 就可以利用模型

公式合理地估算 奈奎斯特频率的

插入损耗。

在此模型公式中,w 是 以密耳为单位的迹线宽度。

f 是奈奎斯特频率。

Df 是 PCB 损耗系数。

Dk 是 PCB 介电常数。

现在来执行 实际计算。

假设 DP 以 HBR2 或 5.4 千兆位/秒的

速率运行。

奈奎斯特频率 f 为数据速率的 1/2 或

2.7GHz。

对于 12 英寸、6 密耳迹线, 损耗系数为 0.02,

介电常数 为 4.3。

这样,我们就可以 估算出在频率为

2.7GHz 时的损耗 大约为 0.53dB。

将 12 英寸 乘以每英寸 0.53dB,

即可得出频率为 2.7GHz 时, 插入损耗约为

6.36 dB。

此值非常接近于 VNA 在频率为 2.7GHz 时

在 12 英寸、6 密耳的 实际迹线中测得的

6.54dB。

假设转接驱动器 在频率为 2.7GHz 时

支持最多 12dB 的损耗, 那么使用估算出的

每英寸 0.53dB 损耗, 就可以得出

HBR2 支持的 最长距离

约为 22 英寸。

此估算值也可以 用来配置转接驱动器

均衡设置。

假设将转接驱动器放在 与同一块电路板上的

信号源相距 10 英寸的位置,

我们就可以利用 这个估算出的损耗

将初始转接驱动器 均衡器设置为 5dB。

可以通过 DisplayPort 合规性测试

完成进一步的 调优。

在拉电流 发送器侧,可以通过

发送器电气 合规性测试来

完成此操作。

而在接收器 灌电流侧,可以通过

接收器抖动容差 测试来完成此操作。

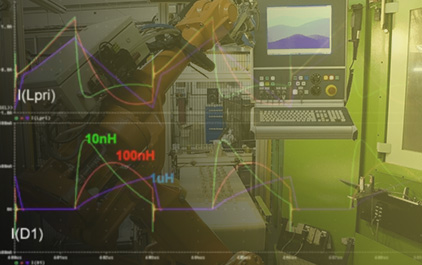

现在,我们来 看一个实际示例。

在观察此 眼图之前,

请观看 TI 高精度 实验室的“什么是眼图?”

演示,以便对 眼图有一个基本的

了解。

第一张图片是 拉电流发送器

输出端的 HBR2 5.4 千兆位/秒

眼图。

眼睛是张开的,因此 通过了 DisplayPort 眼罩

要求。

将迹线 延长 12 英寸,

现在可以看到眼睛 闭上了,因此未通过 DisplayPort

眼罩要求。

从刚刚执行的 计算可知,

每英寸的插入 损耗约为

0.53dB。

对于 12 英寸迹线, 在频率为 2.7GHz 时的

损耗为 6.36dB。

如果在 12 英寸 迹线的输出端

添加一个转接驱动器,并将 转接驱动器均衡器设置为 6dB,

以匹配 12 英寸 迹线的插入损耗,

我们就会发现眼睛 再次张开,并通过了 DisplayPort

眼罩要求。

为了回顾我们讨论的内容, 我们来做一个小测验。

问题 1,判断对错

DP 是一个直流耦合接口。

错。

问题 2 ,判断对错

对于 8.1 千兆位/秒的 数据速率和双通道

配置, 总带宽为

16.2 千兆位/秒。

对。

问题 3 ,判断对错

热插拔检测功能 用于配置 DP 通道。

错。

问题 4 ,判断对错

插入损耗 与 DP 数据速率无关。

错。

问题 5 ,判断对错

DP 转接驱动器有助于 提高 DP 主链路信号

质量。

对。

问题 6 ,判断对错

将 DP 转接驱动器 放在正确的位置

对系统设计 非常重要。

对。

最后,很高兴 为大家介绍

关于 DisplayPort 的这部分信息。

敬请关注以后的课程。

我们将详细介绍 德州仪器 (TI) 推出的

标准和信号 调节器件。

请务必访问我们的 TI E2E 社区 TI.com,

以获得问题解答 和更多信息。

谢谢。

大家好,欢迎观看 TI 高精度实验室视频。 在本系列中,我们将 讨论 DisplayPort 接口, 也称为 DP。 DP 是一种 数字显示接口, 是在 2008 年作为 新一代显示接口推出的。 这种接口旨在取代 旧的显示标准,例如 VGA 和 DVI,并为 个人计算、数字 显示和消费类 电子产品打开 一扇新的大门。 DisplayPort 2.0 支持两个具有 120 赫兹 刷新率、30bpp 和 HDR 的 8K 显示屏或者两个 具有 144 赫兹刷新率和 24bpp、无压缩的 4K 显示屏。 DisplayPort 还兼容 传统的显示屏 连接。 添加了一个 简单的适配器之后, DP 电缆可以 将 DP 拉电流 连接到传统 VGA、单链路 DVI 或 HDMI 显示屏。 任何 DisplayPort的 源端和目的端 都由 3 个 主要部分组成: 主链路、 辅助通道和 热插拔检测,简称 HPD。 主链路用于 传输视频。 主链路包含单向 串行数据通道, 这些通道被称为信道。 辅助通道 是 1 兆位/秒的 半双工、 双向数据 通道,用于传输 控制和状态信息。 HPD 是由灌电流 为拉电流提供的 3.3 伏信号。 HPD 有两个用途, 这两个用途对于启动 拉电流发送器与灌电流 接收器之间的 DisplayPort 通信 链路至关重要。 首先,HPD 可 通知是否存在 灌电流。 当 HPD 较高或者 为 3.3 伏时, 表明存在 灌电流。 当 HPD 较低或者为 0 并 持续 2 毫秒以上时, 表明灌电流 不存在或已消除。 其次,HPD 可用作 从灌电流到 拉电流的中断。 当 HPD 较低或者在 0.5 到 1 毫秒内为 0 时, 表明发生了 中断事件。 灌电流请求拉电流 使用辅助接口读取 灌电流的 DPCD 寄存器 并采取适当的行动。 辅助接口是一个 数据速率为 1 兆位/秒的 双向、半双工 差分接口。 当灌电流被接通 并使用 VESA、EDID 和 VESA MCCS 标准 为主链路传送 管理和器件控制数据时, 即开始进行辅助通信。 在标准 DP 连接中,每个信道 都有一组专用的 双绞线,并利用 差分信令通过这些 双绞线传输数据。 对于 DP 连接,没有 专用的时钟通道, 因为时钟 嵌入到数据中。 DisplayPort 只以 特定的数据速率运行。 DisplayPort 2.0 标准 为主链路定义了 7 种数据速率-- 1.62 千兆位/秒 ,简称 RBR;2.7 千兆位/秒, 简称 HBR; 5.4 千兆位/秒,简称 HBR2; 8.1 千兆位/秒, 简称 HBR3;10 千兆位/秒, 简称 UHBR10; 13.5 千兆位/秒,简称 UHBR13.5; 以及 20 千兆位/秒, ,简称 UHBR20。 当数据速率从 1.62 千兆位/秒提高到 8.1 千兆位/秒时, DP 主链路将 开始出现 信号失真, 这是由封装和 PCB 的 铜损和介电损耗造成的。 结果是, 随着数据速率提高, 主链路长度会缩短。 为了支持更长的 主链路长度, 需要在系统设计 期间考虑以转接 驱动器或 重定时器 形式添加 一个 DP 信号 调节器。 DP 使用 LVDS 信号协议。 它是一个交流耦合、 100 欧姆的差分 信号接口。 在拉电流侧, 发送器 既提供振幅控制, 也提供预加重的 控制。 发送器必须 支持电平 0、电平 1 和电平 2 振幅控制以及 预加重的控制, 电平 3 是可选的。 拉电流处的默认 信号振幅为 400 毫伏峰间值。 默认的 预加重电平为 0dB。 链路协商 用于补偿 DP 拉电流与 DP 灌电流 之间的信号完整性。 补偿通过在 初始灌电流连接 期间按照灌电流的 请求更改 DP 拉电流 振幅和预加重 电平来完成。 如果在初始 灌电流连接之后 发生数据错误,也可以 对补偿进行重新初始化。 当数据速率从 1.62 千兆位/秒 提高到 8.1 千兆位/秒之后,主链路 开始出现 信号失真, 这是由 PCB 和封装的 铜损和介电损耗造成的。 由于主链路中的 阻抗不连续性, 其他组件也可能出现失真, 例如封装、通道和连接器。 数据速率的 提高速度比 目前的接收器设计 发展速度更快,而 PCB 或封装技术能够 与其齐头并进。 虽然使用昂贵的 PCB 材料可以减小 这一损耗, 但 PCB 材料 会很快达到 介电限值 而且成本高昂。 第二种解决方案是 缩短主链路长度, 从而减小 总损耗。 但在需要更长主链路 长度的 DP 系统设计中, 这种解决方案 不切实际,而且 需要以更高的 数据速率运行。 位于主链路上的 拉电流与连接器之间, 或者连接器 与灌电流之间的转接 驱动器或重定时器 有助于克服这一设计挑战。 转接驱动器可 通过均衡和增益 调节来恢复 衰减的输入信号, 因此有助于提高 主链路的信号质量。 重定时器可使用 时钟恢复电路来 恢复衰减的 输入信号、 补偿随机抖动 以及基于纯净的时钟来 重新传输信号。 有关信号调节器的 更多信息, 建议大家观看 TI 高精度实验室推出的 名为“什么是信号调节器”的视频。 在系统设计中,确定 转接驱动器的位置 至关重要。 如果将转接驱动器 放在过于靠近或远离拉电流 发送器或灌电流 接收器的位置, 会对转接驱动器的 有效性产生负面影响, 从而导致系统 性能欠佳。 转接驱动器的 位置取决于 转接驱动器接收器均衡器 之前的系统总计插入损耗。 插入损耗 来自于 PCB 迹线、通道、连接器、 器件封装等等。 如果能够估算出 PCB 迹线的 奈奎斯特区域中的 插入损耗,就可以 计算出 PCB 迹线 长度是否处于 转接驱动器接收器 设计限制内, 并获得初步的转接 驱动器均衡器设置 估算值。 假设皮肤深度限制了 微带或带状线中的 电流、回路中使用 串联电阻、 表面粗糙度 导致电阻系数 增大 2 而且 传输线路的阻抗 为 100 欧姆,那么我们 就可以利用模型 公式合理地估算 奈奎斯特频率的 插入损耗。 在此模型公式中,w 是 以密耳为单位的迹线宽度。 f 是奈奎斯特频率。 Df 是 PCB 损耗系数。 Dk 是 PCB 介电常数。 现在来执行 实际计算。 假设 DP 以 HBR2 或 5.4 千兆位/秒的 速率运行。 奈奎斯特频率 f 为数据速率的 1/2 或 2.7GHz。 对于 12 英寸、6 密耳迹线, 损耗系数为 0.02, 介电常数 为 4.3。 这样,我们就可以 估算出在频率为 2.7GHz 时的损耗 大约为 0.53dB。 将 12 英寸 乘以每英寸 0.53dB, 即可得出频率为 2.7GHz 时, 插入损耗约为 6.36 dB。 此值非常接近于 VNA 在频率为 2.7GHz 时 在 12 英寸、6 密耳的 实际迹线中测得的 6.54dB。 假设转接驱动器 在频率为 2.7GHz 时 支持最多 12dB 的损耗, 那么使用估算出的 每英寸 0.53dB 损耗, 就可以得出 HBR2 支持的 最长距离 约为 22 英寸。 此估算值也可以 用来配置转接驱动器 均衡设置。 假设将转接驱动器放在 与同一块电路板上的 信号源相距 10 英寸的位置, 我们就可以利用 这个估算出的损耗 将初始转接驱动器 均衡器设置为 5dB。 可以通过 DisplayPort 合规性测试 完成进一步的 调优。 在拉电流 发送器侧,可以通过 发送器电气 合规性测试来 完成此操作。 而在接收器 灌电流侧,可以通过 接收器抖动容差 测试来完成此操作。 现在,我们来 看一个实际示例。 在观察此 眼图之前, 请观看 TI 高精度 实验室的“什么是眼图?” 演示,以便对 眼图有一个基本的 了解。 第一张图片是 拉电流发送器 输出端的 HBR2 5.4 千兆位/秒 眼图。 眼睛是张开的,因此 通过了 DisplayPort 眼罩 要求。 将迹线 延长 12 英寸, 现在可以看到眼睛 闭上了,因此未通过 DisplayPort 眼罩要求。 从刚刚执行的 计算可知, 每英寸的插入 损耗约为 0.53dB。 对于 12 英寸迹线, 在频率为 2.7GHz 时的 损耗为 6.36dB。 如果在 12 英寸 迹线的输出端 添加一个转接驱动器,并将 转接驱动器均衡器设置为 6dB, 以匹配 12 英寸 迹线的插入损耗, 我们就会发现眼睛 再次张开,并通过了 DisplayPort 眼罩要求。 为了回顾我们讨论的内容, 我们来做一个小测验。 问题 1,判断对错 DP 是一个直流耦合接口。 错。 问题 2 ,判断对错 对于 8.1 千兆位/秒的 数据速率和双通道 配置, 总带宽为 16.2 千兆位/秒。 对。 问题 3 ,判断对错 热插拔检测功能 用于配置 DP 通道。 错。 问题 4 ,判断对错 插入损耗 与 DP 数据速率无关。 错。 问题 5 ,判断对错 DP 转接驱动器有助于 提高 DP 主链路信号 质量。 对。 问题 6 ,判断对错 将 DP 转接驱动器 放在正确的位置 对系统设计 非常重要。 对。 最后,很高兴 为大家介绍 关于 DisplayPort 的这部分信息。 敬请关注以后的课程。 我们将详细介绍 德州仪器 (TI) 推出的 标准和信号 调节器件。 请务必访问我们的 TI E2E 社区 TI.com, 以获得问题解答 和更多信息。 谢谢。

大家好,欢迎观看 TI 高精度实验室视频。

在本系列中,我们将 讨论 DisplayPort 接口,

也称为 DP。

DP 是一种 数字显示接口,

是在 2008 年作为 新一代显示接口推出的。

这种接口旨在取代 旧的显示标准,例如 VGA

和 DVI,并为 个人计算、数字

显示和消费类 电子产品打开

一扇新的大门。

DisplayPort 2.0 支持两个具有 120 赫兹

刷新率、30bpp 和 HDR 的 8K 显示屏或者两个

具有 144 赫兹刷新率和 24bpp、无压缩的 4K 显示屏。

DisplayPort 还兼容 传统的显示屏

连接。

添加了一个 简单的适配器之后,

DP 电缆可以 将 DP 拉电流

连接到传统 VGA、单链路 DVI 或 HDMI 显示屏。

任何 DisplayPort的 源端和目的端

都由 3 个 主要部分组成:

主链路、 辅助通道和

热插拔检测,简称 HPD。

主链路用于 传输视频。

主链路包含单向 串行数据通道,

这些通道被称为信道。

辅助通道 是 1 兆位/秒的

半双工、 双向数据

通道,用于传输 控制和状态信息。

HPD 是由灌电流 为拉电流提供的

3.3 伏信号。

HPD 有两个用途, 这两个用途对于启动

拉电流发送器与灌电流 接收器之间的 DisplayPort 通信

链路至关重要。

首先,HPD 可 通知是否存在

灌电流。

当 HPD 较高或者 为 3.3 伏时,

表明存在 灌电流。

当 HPD 较低或者为 0 并 持续 2 毫秒以上时,

表明灌电流 不存在或已消除。

其次,HPD 可用作 从灌电流到

拉电流的中断。

当 HPD 较低或者在 0.5 到 1 毫秒内为 0 时,

表明发生了 中断事件。

灌电流请求拉电流 使用辅助接口读取

灌电流的 DPCD 寄存器 并采取适当的行动。

辅助接口是一个 数据速率为 1 兆位/秒的

双向、半双工 差分接口。

当灌电流被接通 并使用 VESA、EDID 和

VESA MCCS 标准 为主链路传送

管理和器件控制数据时, 即开始进行辅助通信。

在标准 DP 连接中,每个信道

都有一组专用的 双绞线,并利用

差分信令通过这些 双绞线传输数据。

对于 DP 连接,没有 专用的时钟通道,

因为时钟 嵌入到数据中。

DisplayPort 只以 特定的数据速率运行。

DisplayPort 2.0 标准 为主链路定义了

7 种数据速率--

1.62 千兆位/秒 ,简称 RBR;2.7 千兆位/秒,

简称 HBR; 5.4 千兆位/秒,简称 HBR2;

8.1 千兆位/秒, 简称 HBR3;10 千兆位/秒,

简称 UHBR10; 13.5 千兆位/秒,简称 UHBR13.5;

以及 20 千兆位/秒, ,简称 UHBR20。

当数据速率从 1.62 千兆位/秒提高到

8.1 千兆位/秒时, DP 主链路将

开始出现 信号失真,

这是由封装和 PCB 的 铜损和介电损耗造成的。

结果是, 随着数据速率提高,

主链路长度会缩短。

为了支持更长的 主链路长度,

需要在系统设计 期间考虑以转接

驱动器或 重定时器

形式添加 一个 DP 信号

调节器。

DP 使用 LVDS 信号协议。

它是一个交流耦合、 100 欧姆的差分

信号接口。

在拉电流侧, 发送器

既提供振幅控制, 也提供预加重的

控制。

发送器必须 支持电平 0、电平 1

和电平 2 振幅控制以及 预加重的控制,

电平 3 是可选的。

拉电流处的默认 信号振幅为

400 毫伏峰间值。

默认的 预加重电平为 0dB。

链路协商 用于补偿

DP 拉电流与 DP 灌电流 之间的信号完整性。

补偿通过在 初始灌电流连接

期间按照灌电流的 请求更改 DP 拉电流

振幅和预加重 电平来完成。

如果在初始 灌电流连接之后

发生数据错误,也可以 对补偿进行重新初始化。

当数据速率从 1.62 千兆位/秒

提高到 8.1 千兆位/秒之后,主链路

开始出现 信号失真,

这是由 PCB 和封装的

铜损和介电损耗造成的。

由于主链路中的 阻抗不连续性,

其他组件也可能出现失真, 例如封装、通道和连接器。

数据速率的 提高速度比

目前的接收器设计 发展速度更快,而 PCB

或封装技术能够 与其齐头并进。

虽然使用昂贵的 PCB 材料可以减小

这一损耗, 但 PCB 材料

会很快达到 介电限值

而且成本高昂。

第二种解决方案是 缩短主链路长度,

从而减小 总损耗。

但在需要更长主链路 长度的 DP 系统设计中,

这种解决方案 不切实际,而且

需要以更高的 数据速率运行。

位于主链路上的

拉电流与连接器之间,

或者连接器 与灌电流之间的转接

驱动器或重定时器 有助于克服这一设计挑战。

转接驱动器可 通过均衡和增益

调节来恢复 衰减的输入信号,

因此有助于提高 主链路的信号质量。

重定时器可使用 时钟恢复电路来

恢复衰减的 输入信号、

补偿随机抖动 以及基于纯净的时钟来

重新传输信号。

有关信号调节器的 更多信息,

建议大家观看 TI 高精度实验室推出的

名为“什么是信号调节器”的视频。

在系统设计中,确定 转接驱动器的位置

至关重要。

如果将转接驱动器 放在过于靠近或远离拉电流

发送器或灌电流 接收器的位置,

会对转接驱动器的 有效性产生负面影响,

从而导致系统 性能欠佳。

转接驱动器的 位置取决于

转接驱动器接收器均衡器 之前的系统总计插入损耗。

插入损耗 来自于 PCB

迹线、通道、连接器、 器件封装等等。

如果能够估算出 PCB 迹线的

奈奎斯特区域中的 插入损耗,就可以

计算出 PCB 迹线 长度是否处于

转接驱动器接收器 设计限制内,

并获得初步的转接 驱动器均衡器设置

估算值。

假设皮肤深度限制了 微带或带状线中的

电流、回路中使用 串联电阻、

表面粗糙度 导致电阻系数

增大 2 而且 传输线路的阻抗

为 100 欧姆,那么我们 就可以利用模型

公式合理地估算 奈奎斯特频率的

插入损耗。

在此模型公式中,w 是 以密耳为单位的迹线宽度。

f 是奈奎斯特频率。

Df 是 PCB 损耗系数。

Dk 是 PCB 介电常数。

现在来执行 实际计算。

假设 DP 以 HBR2 或 5.4 千兆位/秒的

速率运行。

奈奎斯特频率 f 为数据速率的 1/2 或

2.7GHz。

对于 12 英寸、6 密耳迹线, 损耗系数为 0.02,

介电常数 为 4.3。

这样,我们就可以 估算出在频率为

2.7GHz 时的损耗 大约为 0.53dB。

将 12 英寸 乘以每英寸 0.53dB,

即可得出频率为 2.7GHz 时, 插入损耗约为

6.36 dB。

此值非常接近于 VNA 在频率为 2.7GHz 时

在 12 英寸、6 密耳的 实际迹线中测得的

6.54dB。

假设转接驱动器 在频率为 2.7GHz 时

支持最多 12dB 的损耗, 那么使用估算出的

每英寸 0.53dB 损耗, 就可以得出

HBR2 支持的 最长距离

约为 22 英寸。

此估算值也可以 用来配置转接驱动器

均衡设置。

假设将转接驱动器放在 与同一块电路板上的

信号源相距 10 英寸的位置,

我们就可以利用 这个估算出的损耗

将初始转接驱动器 均衡器设置为 5dB。

可以通过 DisplayPort 合规性测试

完成进一步的 调优。

在拉电流 发送器侧,可以通过

发送器电气 合规性测试来

完成此操作。

而在接收器 灌电流侧,可以通过

接收器抖动容差 测试来完成此操作。

现在,我们来 看一个实际示例。

在观察此 眼图之前,

请观看 TI 高精度 实验室的“什么是眼图?”

演示,以便对 眼图有一个基本的

了解。

第一张图片是 拉电流发送器

输出端的 HBR2 5.4 千兆位/秒

眼图。

眼睛是张开的,因此 通过了 DisplayPort 眼罩

要求。

将迹线 延长 12 英寸,

现在可以看到眼睛 闭上了,因此未通过 DisplayPort

眼罩要求。

从刚刚执行的 计算可知,

每英寸的插入 损耗约为

0.53dB。

对于 12 英寸迹线, 在频率为 2.7GHz 时的

损耗为 6.36dB。

如果在 12 英寸 迹线的输出端

添加一个转接驱动器,并将 转接驱动器均衡器设置为 6dB,

以匹配 12 英寸 迹线的插入损耗,

我们就会发现眼睛 再次张开,并通过了 DisplayPort

眼罩要求。

为了回顾我们讨论的内容, 我们来做一个小测验。

问题 1,判断对错

DP 是一个直流耦合接口。

错。

问题 2 ,判断对错

对于 8.1 千兆位/秒的 数据速率和双通道

配置, 总带宽为

16.2 千兆位/秒。

对。

问题 3 ,判断对错

热插拔检测功能 用于配置 DP 通道。

错。

问题 4 ,判断对错

插入损耗 与 DP 数据速率无关。

错。

问题 5 ,判断对错

DP 转接驱动器有助于 提高 DP 主链路信号

质量。

对。

问题 6 ,判断对错

将 DP 转接驱动器 放在正确的位置

对系统设计 非常重要。

对。

最后,很高兴 为大家介绍

关于 DisplayPort 的这部分信息。

敬请关注以后的课程。

我们将详细介绍 德州仪器 (TI) 推出的

标准和信号 调节器件。

请务必访问我们的 TI E2E 社区 TI.com,

以获得问题解答 和更多信息。

谢谢。

手机看

扫码用手机观看

视频简介

视频简介

9.2 TI 高精度实验室 - 视频接口:什么是显示端口(DP)?

所属课程:TI 高精度实验室 - 视频接口

发布时间:2020.02.13

视频集数:3

本节视频时长:00:12:43

该视频讨论了显示端口(DP)接口。 它涵盖了三个主要的信令组件:主链路,辅助通道和热插拔检测。

未学习 9.1 TI 高精度实验室 - 视频接口:什么是串行数字接口(SDI)?

未学习 9.1 TI 高精度实验室 - 视频接口:什么是串行数字接口(SDI)?

未学习 9.2 TI 高精度实验室 - 视频接口:什么是显示端口(DP)?

未学习 9.2 TI 高精度实验室 - 视频接口:什么是显示端口(DP)?

未学习 9.3 TI 高精度实验室 - 视频接口:什么是 HDMI 和双模 DisplayPort ?

未学习 9.3 TI 高精度实验室 - 视频接口:什么是 HDMI 和双模 DisplayPort ?

视频简介

视频简介