### **MSPM0 CPU module introduction** — MSPM0 peripheral training series

**Presented by Gary Gao**

### **MCU level overview ——MSPM0Lxx series**

### **——MSPM0Gxx series**

| CPU<br>ARM Cortex-M0+<br>32 MHz   Power & Clocking<br>POR / BOR / SVS   Precision<br>12-bit 3   Instruction<br>Set<br>Architecture   Armv6-M   Armv6-M   Armv7-M   Armv7-M   Armv8-M   Armv8-M   Armv8.1-M   Armv8.1-M<                                                       | MSPM0L13x3/4/5/6                                             |                           |  | Feature                    | Cortex-<br>M0 | <u>Cortex-</u><br><u>M0+</u> | <u>Cortex-</u><br><u>M1</u> | Cortex-<br>M23 | Cortex-<br>M3 | Cortex-<br>M4 | Cortex-<br>M33 | Cortex-<br>M35P | <u>Cortex-</u><br>M55 | Cortex-<br>M7 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|--|----------------------------|---------------|------------------------------|-----------------------------|----------------|---------------|---------------|----------------|-----------------|-----------------------|---------------|

| Internal LP 32KH2 (3%)   OLP/FNS   Index2one<br>for Armv8-M   No   No   No   Yes (option)   No   Yes (option)   < | CPU                                                          | Power & Clocking          |  | Set                        | Armv6-M       | Armv6-M                      | Armv6-M                     |                | Armv7-M       | Armv7-M       |                |                 |                       | Armv7-M       |

| NNO / Soci DMA   Communication   Zero-drif   Digital Signal   No   No   No   No   No   Yes   Yes <th></th> <th></th> <td></td> <td></td> <td>No</td> <td>No</td> <td>No</td> <td>Yes (option)</td> <td>No</td> <td>No</td> <td>Yes (option)</td> <td>Yes (option)</td> <td>Yes (option)</td> <td>No</td>                                                                                                                                                                                                                      |                                                              |                           |  |                            | No            | No                           | No                          | Yes (option)   | No            | No            | Yes (option)   | Yes (option)    | Yes (option)          | No            |

| Internal Internal Hardware No No Yes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | On-chip Memory                                               | Communication             |  | Processing                 | No            | No                           | No                          | No             | No            | Yes           | Yes            | Yes             | Yes                   | Yes           |

| IZC (2) W/ FastWode+ Timers No No No No No No Yes No Yes No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                              |                           |  |                            | No            | No                           | No                          | Yes            | Yes           | Yes           | Yes            | Yes             | Yes                   | Yes           |

| CRC accelerator (16 and 32 bit)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Data Integrity & Security<br>CRC accelerator (16 and 32 bit) |                           |  | Arm Custom<br>Instructions | No            | No                           | No                          | No             | No            | No            | Yes            | No              | Yes                   | No            |

| IO General Coprocessor   Programming & Debug Up to 28 GPIO Window Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Programming & Debug                                          |                           |  |                            | No            | No                           | No                          | No             | No            | No            | Yes            | Yes             | Yes                   | No            |

| ARM SWD interface   Up to 2 low lb OPA inputs   DMIPS/MHz*   0.87   0.95   0.98   1.25   1.25   1.5   1.6   2.14     ROM UART & I2C BSL           0.95   0.98   1.25   1.5   1.6   2.14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                              | Up to 2 low Ib OPA inputs |  |                            |               | 0.95                         | 0.8                         | 0.98           | 1.25          | 1.25          | 1.5            | 1.5             | 1.6                   | 2.14          |

| Leaded packages: SOT-16, VSSOP-20/28<br>No-lead packages: WQFN-16, VQFN-24/32 A.02 4.02 4.02 4.02 4.02 5.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                              |                           |  | MHz*                       | 2.33          | 2.46                         | 1.85                        | 2.64           | 3.34          | 3.42          | 4.02           | 4.02            | 4.2                   | 5.01          |

| 32 MHz MCU with up to 64kB flash, 32 <b>Maximum</b><br>#External 32 32 32 240 240 240 480 480 480 480 240<br>ADC, dual zero-drift OPA/PGA, COMP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | -                                                            |                           |  | # External                 | 32            | 32                           | 32                          | 240            | 240           | 240           | 480            | 480             | 480                   | 240           |

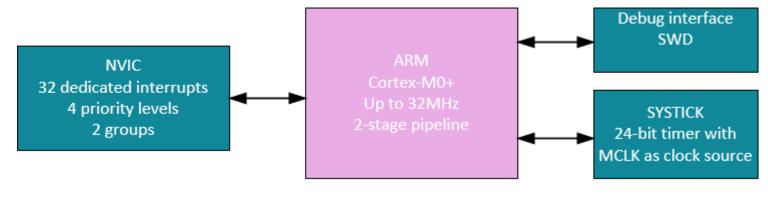

# **MSPM0 CPU module introduction**

#### Key features

- Arm Cortex-M0+ 32-bit CPU based on ARMv6-M architecture

- 2-stage pipeline

- Internal peripherals(NVIC / SYSTICK / MPU / MTB / Debug interface)

- The smallest footprint and lowest power requirements of all the Cortex-M processors

- The exceptional code density that significantly reduces memory requirements, which maximizes the use of on-chip Flash memory to save memory cost, reduce memory power

Fig1: MSPM0L CPU Block Diagram

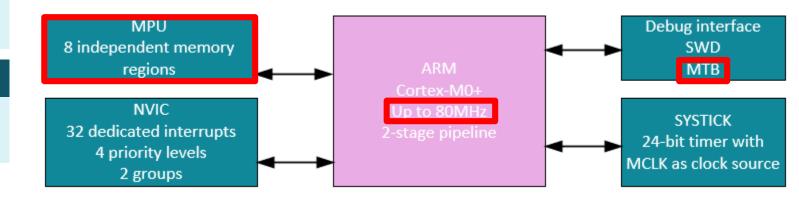

### **Differences between M0 and M0+**

M0+ has 30% less power dissipation, MPU, MTB and fast IO control

Key differences between G and L MCUs

MSPM0Gxx MCUs have MPU and MTB

Fig2: MSPM0G CPU Block Diagram

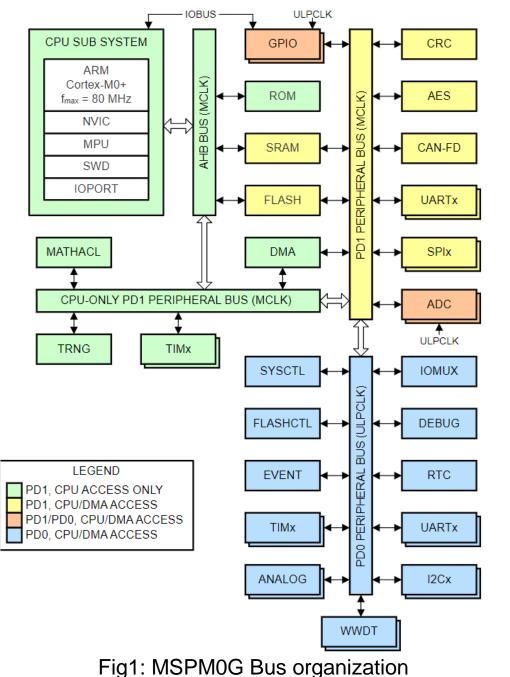

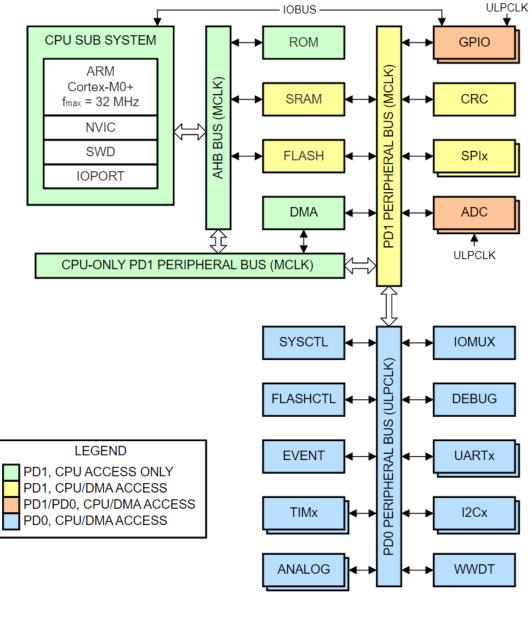

## **MSPM0 CPU module in bus organization**

Fig2: MSPM0L Bus organization

# To find more MSPM0 training series, please visit:

- TI.com.cn

- <u>WeChat (德州仪器公众号)</u>

- Bilibili  $\bullet$

- 21IC