总电离剂量对MOSFET的影响

Loading the player...

将在30s后自动为您播放下一课程

[音乐播放] 大家好。 我叫 Rob Baumann, 是高可靠性方面的 首席技术专家。 如果在观看本视频之后, 您想了解有关 TI 航天 产品的更多信息, 请访问 ti.com/space。 感谢您的观看。 在本次讲座中,我们 将讨论电离辐射 总剂量及其对 MOSFET 的影响。 好的,基本而言, 电离辐射总剂量 机制与氧化层中的 空穴捕获有关。 这是影响 MOSFET 的 主要模式。 还会创建 界面态。 那么,为了方便 每个人理解, 这是金属氧化物 半导体结构的能带图。 那么,左侧是 栅极电极, 中间是栅极 氧化层,然后 右侧是 硅界面 和硅基片。 那么,很显然, 在水平维度, 我们将讨论器件在 垂直方向的深度或 线性程度。 在垂直方向, 当我们在垂直 方向上行时, 我们具有能量, 这是电子能,因此 我们施加正栅极 电压,该电压 将栅极向下拉, 我们具有该跨越 氧化层的斜坡或 跨越氧化层的电场。 这意味着传导 带中的任何电子 都将跑下该斜坡, 并被栅极收集。 电子再次被吸引到 正栅极电压。 空穴或带正电的 缺陷将以互补 方式朝相反 方向运动, 就像气泡一样朝斜坡上方 漂浮,如果您愿意的话。 现在,当这些器件 接触到辐射时, 所吸收的任何辐射 都会制造电子空穴对。 因此空穴态 和电子会分离, 当然,它们 沿着相反的 方向 加速。 现在,栅极氧化层的 一个特性使它们 对总剂量效应 尤其敏感, 这就是电子 移动性或其 移动效率 远高于空穴。 因此,在存在 电场的情况下, 传导带中的 电子很快地 移动,从而 在整个栅极 氧化层中 分布多个空穴。 现在,它们并不是 完全固定的,但 它们以跳跃机制 缓慢地移动,如这些 绿色箭头所示。 因此它们实际上将陷入 低能级陷阱中 -- 低能级 意味着低能量陷阱 -- 刚好沿着价带边缘, 它们以跳跃的移动 方式,从一个陷阱 移动到另一个 陷阱,移向界面。 我们再次得到 正栅极电压。 因此,如果您愿意的话, 这会将这些空穴向上推。 现在,因为这些 陷阱中通常 束缚有氢或质子, 因此当空穴移动 到陷阱中时, 它会释放一些氢。 因此,实际上, 我们具有双重 空穴向右移动的 效应,当它们释放 质子或氢离子时,这些 氢离子也会由电场 进行加速,向右移动。 现在,这两个粒子 具有两种不同的 行为,从而以不同的 方式影响器件。 一旦空穴 接近界面, 就会有大量所谓的 深能级陷阱。 这些是 处于带隙 中间的陷阱。 因此,栅极氧化层 中的带隙是价带 和传导带 之间的距离, 这些深能级 陷阱,所谓的 深能级陷阱恰好 位于带隙中间。 因此空穴向下 移向界面,然后 被捕获在 栅极氧化层中。 因此,这是准 静止种类的 捕获状态, 因此空穴 被不捕获在 栅极氧化层中, 不再自由移动。 按照类似的方式, 质子输送会继续, 直到质子到达 界面,此时它们 实际上生成 所谓的界面态 缺陷,它们可能会 带正电、带负电 或为中性,具体 取决于缺陷的类型。 现在,这些对于 双极结型晶体管 尤其重要,而对 MOSFET 不那么重要。 正如我们将看到的, 它实际上是正电荷 捕获,会支配 大多数 MOSFET 行为。 好的,在 图的左侧, 我基本上显示了一个 NMO 或 n 沟道器件。 因此,请记住, 这基本上是 我们针对源级和漏级 使用 n 型材料的情况。 n 型材料是 负极或富电子 材料的简称, 因为我们记得, 电子带负电。 沟道区 -- 在该状态下, 它是关闭的 -- 是 P 型或正极, 因此我们有一些空穴。 现在,直到我们在 沟道中获得一些电子, 我们才会实现任何导通。 在典型的 NMOS 操作中, 我们施加正栅极电压, 然后,正如您看到的, 我们反转 表面层, 由于栅极下的 场效应,我们 获得高 浓度电子。 现在,这些 高浓度电子 有效地将源极 连接到漏极, 我们获得很大的 导通,晶体管打开, 好的,沟道导通。 现在,当器件发生 总剂量类型接触时, 我们将得到很多辐射粒子, 在这里用黄色箭头进行了指示。 您将注意到每次 黄色箭头横切 氧化层时, 我们就会 生成正电荷。 再说一次,这是界面附近的 孔穴陷阱,被捕获在深能级 陷阱中。 您可以看到, 孔穴效应 将吸引 更多电子。 或者您可以 考虑它,它就像 您已经稍微施 加了正栅极电压。 实际上,在非常 糟糕的情况下, 您生成了数量 巨大的电荷, 您可以关闭 栅极电压。 因此我们只需 关闭栅极电压, 保留沟道。 因此,这是一个泄漏 电流很大的晶体管。 因此终端沟道仍是打开的, 即使我们已关闭栅极 也是如此。 与此相关的海报 基本是位于右侧的 图片,其中显示了 一个漏水的水龙头。 因此,实际上,电离辐射 总电荷会生成一个泄漏的 NMOS 晶体管。 基本而言,该晶体管 会变得越来越难以关闭, 随着您继续 增加剂量接触, 您会得到越来 越多的电荷, 最终,该晶体管 不再工作。 现在,CMOS 组合了互补的 NMOS 和 PMOS 器件。 因此,如你所想, 由于 PMOS 是对 NMOS 器件的补充或 与其相反,因此, 正如我们说过的, 总剂量效应是相反的。 因此,我不打算讨论 整个系列的幻灯片, 因为我们以前已经讨论过, 但我想展示,在这种情况下, 漏级和源极是正极 或空穴类型的材料, N 基片当然 带负电或 具有大量电子。 如果我们想创建 沟道,换句话说, 如果我们想 打开该器件, 我们基本上必须 施加负栅极电压, 吸引一些空穴,从而 连接源区和漏区。 不幸的是,这里 存在的正电荷 将有效地关闭 我们的 PMOS。 因此我们的 PMOS 晶体管或 P 沟道 实际上会保持关闭, 即使栅极电压接地 也是如此,这对于 PMOS 是打开状态。 因此,这会受到辐射, 我们无法打开晶体管。 因此您可以将 PMOS 晶体管上的 电离辐射总剂量 电荷效应比作一个 生锈的水龙头。 基本而言,它会 变得越来越难以 使任何电流流动, 直到晶体管最终 不再工作。 好的。 因此,在 CMOS 中,正如我说过的, 我们有一个 n 沟道器件和 一个 p 沟道器件。 再说一次,p 沟道器件 会变得更加难以打开, 因此它将变得 泄漏更少的剂量, 而 n 沟道变得 越来越泄漏。 嗯,我没有具体 讲过泄漏是 从哪儿来的。 在我在之前的幻灯片中 讲过的示例中,我们 讨论了源区 和漏区 之间的中间 沟道导通。 但是,正如您可以 在该图中看到的, 电荷可以通过其他 两个路径泄漏。 实际上,如果 绝缘层变得 带电,那么 在这里,两个 晶体管之间的隔离层 或绝缘层是所谓的浅沟 隔离。 这是两种类型之一,我将 在后面的幻灯片中讨论 这两种类型。 但该红色区域 具有很大的量, 您可以捕获大量的 电荷,然后它们在电场下 可以在沟道的 边缘或刚好在 沟道的旁边积累。 因此您得到潜在的 沿着 3 的泄漏路径, 以及隔离层下 通向 n 阱的泄漏 路径,如泄漏 路径 2 中所示。 那么 IV 看起来是什么样子的? 嗯,这是一个 n 沟道 IV。 蓝色的曲线 表示 n 沟道本身, 假设不存在 隔离泄漏。 因此这里的第一条 曲线 PRERAD,蓝色曲线, 是典型的 NMOS 特征。 我们将栅极-源极 电压调为正电压, 我们在沟道中 吸引电子,然后 我们连接源极 和漏极并获得 高导通状态。 现在,一旦我们 对器件进行辐照, 我们会再次 生成正电荷, 因此阈值电压下降。 您可以看到 曲线移向左侧。 这是预期行为, 它意味着晶体管 开始泄漏或 其更容易打开。 对于较小的栅极 电压,您会获得 相同量的导通。 在现代晶体管中 -- 现代指低于 100 纳米、100 埃或 200 埃 厚度的栅极 氧化层 -- 该效应 是最低的。 因此,对于大多数应用, VT 漂移几乎可以忽略。 现在机制 2 和 3 中泄漏变得很重要, 这些机制由绿色 曲线进行定义。 这是隔离泄漏, 因此它是由 隔离上的 该重叠栅极 导致的寄生晶体管, 可以打开隔离泄漏。 在存在辐射的情况下, 该曲线会向左移动。 因此该绿色曲线, 在没有辐射的情况下, 只有达到 8 伏 才会打开,对于 该特定的技术, 将是很好的隔离。 不过,一旦我们 使其接触辐射, 正电荷就会 被捕获,在 NMOS 区域,您将获得 极大量的泄漏。 您将注意到,该隔离 泄漏,假设处于 0 伏, 在正常情况下 -- 我们再次看看 这里的蓝色 曲线 -- 该 NMOS 晶体管的泄漏 大约为 5 或 6 皮安。 不过,由于辐射 之后的隔离泄漏, 我们处于微安范围内。 因此几乎是六个 数量级的泄漏。 这实际上可能会 为器件带来灾难, 因为 IDDQ 会 增加到超标, 而您将失去功能。 因此,总剂量 实际损坏 CMOS 器件,至少是 现代器件的 主要途径是通过 机制 3 或 2,此时 隔离泄漏起主导 作用,由于电流规格 或实际电流功能, 我们基本上会失败。 请注意,我提到过 浅沟隔离,但我 没有提到 另一种类型。 有两种类型的隔离。 第一种比较 成熟,是局部 场氧化或 针对局域 场氧化的 LOCOS。 这基本上是已生长的 氧化层,它具有非常 独特的形状。 因为硅在氧化层 生长时会被消耗, 因此您会对氧化层 进行一定深度的渗透, 但氧化层还会 升高到硅层以上。 问题就在这里, 在氧化层的边缘, 存在一个所谓的 鸟嘴区域,该区域 集中了电场, 实际上会在 该区域 捕获大量 电荷或积累 大量正电荷。 猜猜会怎么样? 由于您在这里 积累了大量正电荷, 您将影响 下面的硅 基片并导致 在隔离的边缘 产生泄漏沟道。 事实上,这是 局部场氧化 或 LOCOS,所谓的 LOCOS 的最大故障模式。 现在,我提到过的 另一种类型的隔离, 它在现代 技术中更常见。 这是浅沟 隔离。 基本而言, 这是不同的。 它不是已生长的氧化层。 基本而言,我们在 晶体管之间挖一个 条,以隔离 它们,然后 我们使用氧化层和 其他电介质回填沟。 现在,这还可能 在边缘存在问题。 如果电场线 过于集中或 依赖于层, 所使用的 不同层,您可能 会积累电荷。 因此,使用 STI 不能保证性能。 但正如您将在 右侧的图中看到的 -- 这是一篇来自 Sandia 的论文 -- 他们 采用了一些 或多种商业 技术并对其 进行了总剂量测试。 他们按照 LOCOS、该局部 氧化类型和浅沟 隔离对这些技术 进行了划分。 很显然,浅沟 隔离对总剂量 性能具有 很大的帮助。 因此黄色的线向 我们展示了大约 100 k -- 或者黄色 区域低于 100 krad。 正如这里所说的,100 krad 对于大多数航天应用而言 是很好的,甚至是 50 krad。 但在某些情况下,LOCOS 很难达到 10 krad 以上, 正如您从这些 较低的点中看到的。 一旦您转向 浅沟隔离, 您通常会 达到几百 krad。 现在,我应该提到, 这些也是较低的 电压技术。 您可以从 原始的能带 图和有关电离辐射 总剂量的讨论中回想起, 电场对于定义 该效应而言 很重要。 因此,如果我们具有 更高的电压部分, 它将对总剂量 更加敏感,因为 它可以移动 其中的更多电荷。 好的。 最后,正如我们提到过的, 在行为与正栅极电压相似的 氧化层中, 该效应的 主要推动因素是 空穴、正电荷捕获。 NMOS 变得 更加泄漏 -- 换句话说,打开它 所需的栅极电压更小 -- 而 PMOS 变得 更难以打开, 打开它所需的 栅极电压更大。 从根本上讲, 之所以产生 功能故障,是因为 NMOS 开始越来越泄露,最终, 您的电流规格 失败,或者在极端 情况下,您的 功能不起作用。 正如我们看到的, 泄漏来自栅极氧化层, 直接栅极氧化层, 因此源极和栅极 之间的沟道区变得 泄漏,以及隔离泄漏。 正如我说过的, 在高级 CMOS 技术中, 氧化层厚度 不超过 200 埃, 在如此小的 厚度中不会 积累足够的电荷。 因此,基本而言, 隔离泄漏起主导作用。 因此,再说一次, 我们曾讨论的 浅沟隔离或 LOCOS 隔离会收集 更多的电荷,然后 将其集中在某些 高电场区, 基本而言, 隔离泄漏是 主要故障机制。 根据经验, 对于总剂量, 浅沟隔离通常比 LOCOS 更加可靠,至少在低 Vdd 下 是这样。 感谢您的关注。

[音乐播放] 大家好。 我叫 Rob Baumann, 是高可靠性方面的 首席技术专家。 如果在观看本视频之后, 您想了解有关 TI 航天 产品的更多信息, 请访问 ti.com/space。 感谢您的观看。 在本次讲座中,我们 将讨论电离辐射 总剂量及其对 MOSFET 的影响。 好的,基本而言, 电离辐射总剂量 机制与氧化层中的 空穴捕获有关。 这是影响 MOSFET 的 主要模式。 还会创建 界面态。 那么,为了方便 每个人理解, 这是金属氧化物 半导体结构的能带图。 那么,左侧是 栅极电极, 中间是栅极 氧化层,然后 右侧是 硅界面 和硅基片。 那么,很显然, 在水平维度, 我们将讨论器件在 垂直方向的深度或 线性程度。 在垂直方向, 当我们在垂直 方向上行时, 我们具有能量, 这是电子能,因此 我们施加正栅极 电压,该电压 将栅极向下拉, 我们具有该跨越 氧化层的斜坡或 跨越氧化层的电场。 这意味着传导 带中的任何电子 都将跑下该斜坡, 并被栅极收集。 电子再次被吸引到 正栅极电压。 空穴或带正电的 缺陷将以互补 方式朝相反 方向运动, 就像气泡一样朝斜坡上方 漂浮,如果您愿意的话。 现在,当这些器件 接触到辐射时, 所吸收的任何辐射 都会制造电子空穴对。 因此空穴态 和电子会分离, 当然,它们 沿着相反的 方向 加速。 现在,栅极氧化层的 一个特性使它们 对总剂量效应 尤其敏感, 这就是电子 移动性或其 移动效率 远高于空穴。 因此,在存在 电场的情况下, 传导带中的 电子很快地 移动,从而 在整个栅极 氧化层中 分布多个空穴。 现在,它们并不是 完全固定的,但 它们以跳跃机制 缓慢地移动,如这些 绿色箭头所示。 因此它们实际上将陷入 低能级陷阱中 -- 低能级 意味着低能量陷阱 -- 刚好沿着价带边缘, 它们以跳跃的移动 方式,从一个陷阱 移动到另一个 陷阱,移向界面。 我们再次得到 正栅极电压。 因此,如果您愿意的话, 这会将这些空穴向上推。 现在,因为这些 陷阱中通常 束缚有氢或质子, 因此当空穴移动 到陷阱中时, 它会释放一些氢。 因此,实际上, 我们具有双重 空穴向右移动的 效应,当它们释放 质子或氢离子时,这些 氢离子也会由电场 进行加速,向右移动。 现在,这两个粒子 具有两种不同的 行为,从而以不同的 方式影响器件。 一旦空穴 接近界面, 就会有大量所谓的 深能级陷阱。 这些是 处于带隙 中间的陷阱。 因此,栅极氧化层 中的带隙是价带 和传导带 之间的距离, 这些深能级 陷阱,所谓的 深能级陷阱恰好 位于带隙中间。 因此空穴向下 移向界面,然后 被捕获在 栅极氧化层中。 因此,这是准 静止种类的 捕获状态, 因此空穴 被不捕获在 栅极氧化层中, 不再自由移动。 按照类似的方式, 质子输送会继续, 直到质子到达 界面,此时它们 实际上生成 所谓的界面态 缺陷,它们可能会 带正电、带负电 或为中性,具体 取决于缺陷的类型。 现在,这些对于 双极结型晶体管 尤其重要,而对 MOSFET 不那么重要。 正如我们将看到的, 它实际上是正电荷 捕获,会支配 大多数 MOSFET 行为。 好的,在 图的左侧, 我基本上显示了一个 NMO 或 n 沟道器件。 因此,请记住, 这基本上是 我们针对源级和漏级 使用 n 型材料的情况。 n 型材料是 负极或富电子 材料的简称, 因为我们记得, 电子带负电。 沟道区 -- 在该状态下, 它是关闭的 -- 是 P 型或正极, 因此我们有一些空穴。 现在,直到我们在 沟道中获得一些电子, 我们才会实现任何导通。 在典型的 NMOS 操作中, 我们施加正栅极电压, 然后,正如您看到的, 我们反转 表面层, 由于栅极下的 场效应,我们 获得高 浓度电子。 现在,这些 高浓度电子 有效地将源极 连接到漏极, 我们获得很大的 导通,晶体管打开, 好的,沟道导通。 现在,当器件发生 总剂量类型接触时, 我们将得到很多辐射粒子, 在这里用黄色箭头进行了指示。 您将注意到每次 黄色箭头横切 氧化层时, 我们就会 生成正电荷。 再说一次,这是界面附近的 孔穴陷阱,被捕获在深能级 陷阱中。 您可以看到, 孔穴效应 将吸引 更多电子。 或者您可以 考虑它,它就像 您已经稍微施 加了正栅极电压。 实际上,在非常 糟糕的情况下, 您生成了数量 巨大的电荷, 您可以关闭 栅极电压。 因此我们只需 关闭栅极电压, 保留沟道。 因此,这是一个泄漏 电流很大的晶体管。 因此终端沟道仍是打开的, 即使我们已关闭栅极 也是如此。 与此相关的海报 基本是位于右侧的 图片,其中显示了 一个漏水的水龙头。 因此,实际上,电离辐射 总电荷会生成一个泄漏的 NMOS 晶体管。 基本而言,该晶体管 会变得越来越难以关闭, 随着您继续 增加剂量接触, 您会得到越来 越多的电荷, 最终,该晶体管 不再工作。 现在,CMOS 组合了互补的 NMOS 和 PMOS 器件。 因此,如你所想, 由于 PMOS 是对 NMOS 器件的补充或 与其相反,因此, 正如我们说过的, 总剂量效应是相反的。 因此,我不打算讨论 整个系列的幻灯片, 因为我们以前已经讨论过, 但我想展示,在这种情况下, 漏级和源极是正极 或空穴类型的材料, N 基片当然 带负电或 具有大量电子。 如果我们想创建 沟道,换句话说, 如果我们想 打开该器件, 我们基本上必须 施加负栅极电压, 吸引一些空穴,从而 连接源区和漏区。 不幸的是,这里 存在的正电荷 将有效地关闭 我们的 PMOS。 因此我们的 PMOS 晶体管或 P 沟道 实际上会保持关闭, 即使栅极电压接地 也是如此,这对于 PMOS 是打开状态。 因此,这会受到辐射, 我们无法打开晶体管。 因此您可以将 PMOS 晶体管上的 电离辐射总剂量 电荷效应比作一个 生锈的水龙头。 基本而言,它会 变得越来越难以 使任何电流流动, 直到晶体管最终 不再工作。 好的。 因此,在 CMOS 中,正如我说过的, 我们有一个 n 沟道器件和 一个 p 沟道器件。 再说一次,p 沟道器件 会变得更加难以打开, 因此它将变得 泄漏更少的剂量, 而 n 沟道变得 越来越泄漏。 嗯,我没有具体 讲过泄漏是 从哪儿来的。 在我在之前的幻灯片中 讲过的示例中,我们 讨论了源区 和漏区 之间的中间 沟道导通。 但是,正如您可以 在该图中看到的, 电荷可以通过其他 两个路径泄漏。 实际上,如果 绝缘层变得 带电,那么 在这里,两个 晶体管之间的隔离层 或绝缘层是所谓的浅沟 隔离。 这是两种类型之一,我将 在后面的幻灯片中讨论 这两种类型。 但该红色区域 具有很大的量, 您可以捕获大量的 电荷,然后它们在电场下 可以在沟道的 边缘或刚好在 沟道的旁边积累。 因此您得到潜在的 沿着 3 的泄漏路径, 以及隔离层下 通向 n 阱的泄漏 路径,如泄漏 路径 2 中所示。 那么 IV 看起来是什么样子的? 嗯,这是一个 n 沟道 IV。 蓝色的曲线 表示 n 沟道本身, 假设不存在 隔离泄漏。 因此这里的第一条 曲线 PRERAD,蓝色曲线, 是典型的 NMOS 特征。 我们将栅极-源极 电压调为正电压, 我们在沟道中 吸引电子,然后 我们连接源极 和漏极并获得 高导通状态。 现在,一旦我们 对器件进行辐照, 我们会再次 生成正电荷, 因此阈值电压下降。 您可以看到 曲线移向左侧。 这是预期行为, 它意味着晶体管 开始泄漏或 其更容易打开。 对于较小的栅极 电压,您会获得 相同量的导通。 在现代晶体管中 -- 现代指低于 100 纳米、100 埃或 200 埃 厚度的栅极 氧化层 -- 该效应 是最低的。 因此,对于大多数应用, VT 漂移几乎可以忽略。 现在机制 2 和 3 中泄漏变得很重要, 这些机制由绿色 曲线进行定义。 这是隔离泄漏, 因此它是由 隔离上的 该重叠栅极 导致的寄生晶体管, 可以打开隔离泄漏。 在存在辐射的情况下, 该曲线会向左移动。 因此该绿色曲线, 在没有辐射的情况下, 只有达到 8 伏 才会打开,对于 该特定的技术, 将是很好的隔离。 不过,一旦我们 使其接触辐射, 正电荷就会 被捕获,在 NMOS 区域,您将获得 极大量的泄漏。 您将注意到,该隔离 泄漏,假设处于 0 伏, 在正常情况下 -- 我们再次看看 这里的蓝色 曲线 -- 该 NMOS 晶体管的泄漏 大约为 5 或 6 皮安。 不过,由于辐射 之后的隔离泄漏, 我们处于微安范围内。 因此几乎是六个 数量级的泄漏。 这实际上可能会 为器件带来灾难, 因为 IDDQ 会 增加到超标, 而您将失去功能。 因此,总剂量 实际损坏 CMOS 器件,至少是 现代器件的 主要途径是通过 机制 3 或 2,此时 隔离泄漏起主导 作用,由于电流规格 或实际电流功能, 我们基本上会失败。 请注意,我提到过 浅沟隔离,但我 没有提到 另一种类型。 有两种类型的隔离。 第一种比较 成熟,是局部 场氧化或 针对局域 场氧化的 LOCOS。 这基本上是已生长的 氧化层,它具有非常 独特的形状。 因为硅在氧化层 生长时会被消耗, 因此您会对氧化层 进行一定深度的渗透, 但氧化层还会 升高到硅层以上。 问题就在这里, 在氧化层的边缘, 存在一个所谓的 鸟嘴区域,该区域 集中了电场, 实际上会在 该区域 捕获大量 电荷或积累 大量正电荷。 猜猜会怎么样? 由于您在这里 积累了大量正电荷, 您将影响 下面的硅 基片并导致 在隔离的边缘 产生泄漏沟道。 事实上,这是 局部场氧化 或 LOCOS,所谓的 LOCOS 的最大故障模式。 现在,我提到过的 另一种类型的隔离, 它在现代 技术中更常见。 这是浅沟 隔离。 基本而言, 这是不同的。 它不是已生长的氧化层。 基本而言,我们在 晶体管之间挖一个 条,以隔离 它们,然后 我们使用氧化层和 其他电介质回填沟。 现在,这还可能 在边缘存在问题。 如果电场线 过于集中或 依赖于层, 所使用的 不同层,您可能 会积累电荷。 因此,使用 STI 不能保证性能。 但正如您将在 右侧的图中看到的 -- 这是一篇来自 Sandia 的论文 -- 他们 采用了一些 或多种商业 技术并对其 进行了总剂量测试。 他们按照 LOCOS、该局部 氧化类型和浅沟 隔离对这些技术 进行了划分。 很显然,浅沟 隔离对总剂量 性能具有 很大的帮助。 因此黄色的线向 我们展示了大约 100 k -- 或者黄色 区域低于 100 krad。 正如这里所说的,100 krad 对于大多数航天应用而言 是很好的,甚至是 50 krad。 但在某些情况下,LOCOS 很难达到 10 krad 以上, 正如您从这些 较低的点中看到的。 一旦您转向 浅沟隔离, 您通常会 达到几百 krad。 现在,我应该提到, 这些也是较低的 电压技术。 您可以从 原始的能带 图和有关电离辐射 总剂量的讨论中回想起, 电场对于定义 该效应而言 很重要。 因此,如果我们具有 更高的电压部分, 它将对总剂量 更加敏感,因为 它可以移动 其中的更多电荷。 好的。 最后,正如我们提到过的, 在行为与正栅极电压相似的 氧化层中, 该效应的 主要推动因素是 空穴、正电荷捕获。 NMOS 变得 更加泄漏 -- 换句话说,打开它 所需的栅极电压更小 -- 而 PMOS 变得 更难以打开, 打开它所需的 栅极电压更大。 从根本上讲, 之所以产生 功能故障,是因为 NMOS 开始越来越泄露,最终, 您的电流规格 失败,或者在极端 情况下,您的 功能不起作用。 正如我们看到的, 泄漏来自栅极氧化层, 直接栅极氧化层, 因此源极和栅极 之间的沟道区变得 泄漏,以及隔离泄漏。 正如我说过的, 在高级 CMOS 技术中, 氧化层厚度 不超过 200 埃, 在如此小的 厚度中不会 积累足够的电荷。 因此,基本而言, 隔离泄漏起主导作用。 因此,再说一次, 我们曾讨论的 浅沟隔离或 LOCOS 隔离会收集 更多的电荷,然后 将其集中在某些 高电场区, 基本而言, 隔离泄漏是 主要故障机制。 根据经验, 对于总剂量, 浅沟隔离通常比 LOCOS 更加可靠,至少在低 Vdd 下 是这样。 感谢您的关注。

[音乐播放]

大家好。

我叫 Rob Baumann, 是高可靠性方面的

首席技术专家。

如果在观看本视频之后, 您想了解有关 TI 航天

产品的更多信息, 请访问 ti.com/space。

感谢您的观看。

在本次讲座中,我们 将讨论电离辐射

总剂量及其对 MOSFET 的影响。

好的,基本而言, 电离辐射总剂量

机制与氧化层中的 空穴捕获有关。

这是影响 MOSFET 的 主要模式。

还会创建 界面态。

那么,为了方便 每个人理解,

这是金属氧化物 半导体结构的能带图。

那么,左侧是 栅极电极,

中间是栅极 氧化层,然后

右侧是 硅界面

和硅基片。

那么,很显然, 在水平维度,

我们将讨论器件在 垂直方向的深度或

线性程度。

在垂直方向, 当我们在垂直

方向上行时, 我们具有能量,

这是电子能,因此 我们施加正栅极

电压,该电压 将栅极向下拉,

我们具有该跨越 氧化层的斜坡或

跨越氧化层的电场。

这意味着传导 带中的任何电子

都将跑下该斜坡, 并被栅极收集。

电子再次被吸引到 正栅极电压。

空穴或带正电的 缺陷将以互补

方式朝相反 方向运动,

就像气泡一样朝斜坡上方 漂浮,如果您愿意的话。

现在,当这些器件 接触到辐射时,

所吸收的任何辐射 都会制造电子空穴对。

因此空穴态 和电子会分离,

当然,它们 沿着相反的

方向 加速。

现在,栅极氧化层的 一个特性使它们

对总剂量效应 尤其敏感,

这就是电子 移动性或其

移动效率 远高于空穴。

因此,在存在 电场的情况下,

传导带中的 电子很快地

移动,从而 在整个栅极

氧化层中 分布多个空穴。

现在,它们并不是 完全固定的,但

它们以跳跃机制 缓慢地移动,如这些

绿色箭头所示。

因此它们实际上将陷入 低能级陷阱中 -- 低能级

意味着低能量陷阱 -- 刚好沿着价带边缘,

它们以跳跃的移动 方式,从一个陷阱

移动到另一个 陷阱,移向界面。

我们再次得到 正栅极电压。

因此,如果您愿意的话, 这会将这些空穴向上推。

现在,因为这些 陷阱中通常

束缚有氢或质子, 因此当空穴移动

到陷阱中时, 它会释放一些氢。

因此,实际上, 我们具有双重

空穴向右移动的 效应,当它们释放

质子或氢离子时,这些 氢离子也会由电场

进行加速,向右移动。

现在,这两个粒子 具有两种不同的

行为,从而以不同的 方式影响器件。

一旦空穴 接近界面,

就会有大量所谓的 深能级陷阱。

这些是 处于带隙

中间的陷阱。

因此,栅极氧化层 中的带隙是价带

和传导带 之间的距离,

这些深能级 陷阱,所谓的

深能级陷阱恰好 位于带隙中间。

因此空穴向下 移向界面,然后

被捕获在 栅极氧化层中。

因此,这是准 静止种类的

捕获状态, 因此空穴

被不捕获在 栅极氧化层中,

不再自由移动。

按照类似的方式, 质子输送会继续,

直到质子到达 界面,此时它们

实际上生成 所谓的界面态

缺陷,它们可能会 带正电、带负电

或为中性,具体 取决于缺陷的类型。

现在,这些对于 双极结型晶体管

尤其重要,而对 MOSFET 不那么重要。

正如我们将看到的, 它实际上是正电荷

捕获,会支配 大多数 MOSFET 行为。

好的,在 图的左侧,

我基本上显示了一个 NMO 或 n 沟道器件。

因此,请记住, 这基本上是

我们针对源级和漏级 使用 n 型材料的情况。

n 型材料是 负极或富电子

材料的简称, 因为我们记得,

电子带负电。

沟道区 -- 在该状态下,

它是关闭的 -- 是 P 型或正极,

因此我们有一些空穴。

现在,直到我们在 沟道中获得一些电子,

我们才会实现任何导通。

在典型的 NMOS 操作中,

我们施加正栅极电压, 然后,正如您看到的,

我们反转 表面层,

由于栅极下的 场效应,我们

获得高 浓度电子。

现在,这些 高浓度电子

有效地将源极 连接到漏极,

我们获得很大的 导通,晶体管打开,

好的,沟道导通。

现在,当器件发生 总剂量类型接触时,

我们将得到很多辐射粒子, 在这里用黄色箭头进行了指示。

您将注意到每次 黄色箭头横切

氧化层时, 我们就会

生成正电荷。

再说一次,这是界面附近的 孔穴陷阱,被捕获在深能级

陷阱中。

您可以看到, 孔穴效应

将吸引 更多电子。

或者您可以 考虑它,它就像

您已经稍微施 加了正栅极电压。

实际上,在非常 糟糕的情况下,

您生成了数量 巨大的电荷,

您可以关闭 栅极电压。

因此我们只需 关闭栅极电压,

保留沟道。

因此,这是一个泄漏 电流很大的晶体管。

因此终端沟道仍是打开的, 即使我们已关闭栅极

也是如此。

与此相关的海报 基本是位于右侧的

图片,其中显示了 一个漏水的水龙头。

因此,实际上,电离辐射 总电荷会生成一个泄漏的

NMOS 晶体管。

基本而言,该晶体管 会变得越来越难以关闭,

随着您继续 增加剂量接触,

您会得到越来 越多的电荷,

最终,该晶体管 不再工作。

现在,CMOS 组合了互补的 NMOS 和 PMOS 器件。

因此,如你所想, 由于 PMOS 是对

NMOS 器件的补充或 与其相反,因此,

正如我们说过的, 总剂量效应是相反的。

因此,我不打算讨论 整个系列的幻灯片,

因为我们以前已经讨论过, 但我想展示,在这种情况下,

漏级和源极是正极 或空穴类型的材料,

N 基片当然 带负电或

具有大量电子。

如果我们想创建 沟道,换句话说,

如果我们想 打开该器件,

我们基本上必须 施加负栅极电压,

吸引一些空穴,从而 连接源区和漏区。

不幸的是,这里 存在的正电荷

将有效地关闭 我们的 PMOS。

因此我们的 PMOS 晶体管或 P 沟道

实际上会保持关闭, 即使栅极电压接地

也是如此,这对于 PMOS 是打开状态。

因此,这会受到辐射, 我们无法打开晶体管。

因此您可以将 PMOS 晶体管上的

电离辐射总剂量 电荷效应比作一个

生锈的水龙头。

基本而言,它会 变得越来越难以

使任何电流流动, 直到晶体管最终

不再工作。

好的。

因此,在 CMOS 中,正如我说过的, 我们有一个 n 沟道器件和

一个 p 沟道器件。

再说一次,p 沟道器件 会变得更加难以打开,

因此它将变得 泄漏更少的剂量,

而 n 沟道变得 越来越泄漏。

嗯,我没有具体 讲过泄漏是

从哪儿来的。

在我在之前的幻灯片中 讲过的示例中,我们

讨论了源区 和漏区

之间的中间 沟道导通。

但是,正如您可以 在该图中看到的,

电荷可以通过其他 两个路径泄漏。

实际上,如果 绝缘层变得

带电,那么 在这里,两个

晶体管之间的隔离层 或绝缘层是所谓的浅沟

隔离。

这是两种类型之一,我将 在后面的幻灯片中讨论

这两种类型。

但该红色区域 具有很大的量,

您可以捕获大量的 电荷,然后它们在电场下

可以在沟道的 边缘或刚好在

沟道的旁边积累。

因此您得到潜在的 沿着 3 的泄漏路径,

以及隔离层下 通向 n 阱的泄漏

路径,如泄漏 路径 2 中所示。

那么 IV 看起来是什么样子的?

嗯,这是一个 n 沟道 IV。

蓝色的曲线 表示 n 沟道本身,

假设不存在 隔离泄漏。

因此这里的第一条 曲线 PRERAD,蓝色曲线,

是典型的 NMOS 特征。

我们将栅极-源极 电压调为正电压,

我们在沟道中 吸引电子,然后

我们连接源极 和漏极并获得

高导通状态。

现在,一旦我们 对器件进行辐照,

我们会再次 生成正电荷,

因此阈值电压下降。

您可以看到 曲线移向左侧。

这是预期行为, 它意味着晶体管

开始泄漏或 其更容易打开。

对于较小的栅极 电压,您会获得

相同量的导通。

在现代晶体管中 -- 现代指低于

100 纳米、100 埃或 200 埃

厚度的栅极 氧化层 -- 该效应

是最低的。

因此,对于大多数应用, VT 漂移几乎可以忽略。

现在机制 2 和 3 中泄漏变得很重要,

这些机制由绿色 曲线进行定义。

这是隔离泄漏, 因此它是由

隔离上的 该重叠栅极

导致的寄生晶体管, 可以打开隔离泄漏。

在存在辐射的情况下, 该曲线会向左移动。

因此该绿色曲线, 在没有辐射的情况下,

只有达到 8 伏 才会打开,对于

该特定的技术, 将是很好的隔离。

不过,一旦我们 使其接触辐射,

正电荷就会 被捕获,在 NMOS

区域,您将获得 极大量的泄漏。

您将注意到,该隔离 泄漏,假设处于 0 伏,

在正常情况下 -- 我们再次看看

这里的蓝色 曲线 -- 该 NMOS

晶体管的泄漏 大约为 5 或 6

皮安。

不过,由于辐射 之后的隔离泄漏,

我们处于微安范围内。

因此几乎是六个 数量级的泄漏。

这实际上可能会 为器件带来灾难,

因为 IDDQ 会 增加到超标,

而您将失去功能。

因此,总剂量 实际损坏 CMOS

器件,至少是 现代器件的

主要途径是通过 机制 3 或 2,此时

隔离泄漏起主导 作用,由于电流规格

或实际电流功能, 我们基本上会失败。

请注意,我提到过 浅沟隔离,但我

没有提到 另一种类型。

有两种类型的隔离。

第一种比较 成熟,是局部

场氧化或 针对局域

场氧化的 LOCOS。

这基本上是已生长的 氧化层,它具有非常

独特的形状。

因为硅在氧化层 生长时会被消耗,

因此您会对氧化层 进行一定深度的渗透,

但氧化层还会 升高到硅层以上。

问题就在这里, 在氧化层的边缘,

存在一个所谓的 鸟嘴区域,该区域

集中了电场, 实际上会在

该区域 捕获大量

电荷或积累 大量正电荷。

猜猜会怎么样?

由于您在这里 积累了大量正电荷,

您将影响 下面的硅

基片并导致 在隔离的边缘

产生泄漏沟道。

事实上,这是 局部场氧化

或 LOCOS,所谓的 LOCOS 的最大故障模式。

现在,我提到过的 另一种类型的隔离,

它在现代 技术中更常见。

这是浅沟 隔离。

基本而言, 这是不同的。

它不是已生长的氧化层。

基本而言,我们在 晶体管之间挖一个

条,以隔离 它们,然后

我们使用氧化层和 其他电介质回填沟。

现在,这还可能 在边缘存在问题。

如果电场线 过于集中或

依赖于层, 所使用的

不同层,您可能 会积累电荷。

因此,使用 STI 不能保证性能。

但正如您将在 右侧的图中看到的 --

这是一篇来自 Sandia 的论文 -- 他们

采用了一些 或多种商业

技术并对其 进行了总剂量测试。

他们按照 LOCOS、该局部

氧化类型和浅沟 隔离对这些技术

进行了划分。

很显然,浅沟 隔离对总剂量

性能具有 很大的帮助。

因此黄色的线向 我们展示了大约 100

k -- 或者黄色 区域低于 100 krad。

正如这里所说的,100 krad 对于大多数航天应用而言

是很好的,甚至是 50 krad。

但在某些情况下,LOCOS 很难达到 10 krad 以上,

正如您从这些 较低的点中看到的。

一旦您转向 浅沟隔离,

您通常会 达到几百 krad。

现在,我应该提到, 这些也是较低的

电压技术。

您可以从 原始的能带

图和有关电离辐射 总剂量的讨论中回想起,

电场对于定义 该效应而言

很重要。

因此,如果我们具有 更高的电压部分,

它将对总剂量 更加敏感,因为

它可以移动 其中的更多电荷。

好的。

最后,正如我们提到过的, 在行为与正栅极电压相似的

氧化层中, 该效应的

主要推动因素是 空穴、正电荷捕获。

NMOS 变得 更加泄漏 --

换句话说,打开它 所需的栅极电压更小 --

而 PMOS 变得 更难以打开,

打开它所需的 栅极电压更大。

从根本上讲, 之所以产生

功能故障,是因为 NMOS 开始越来越泄露,最终,

您的电流规格 失败,或者在极端

情况下,您的 功能不起作用。

正如我们看到的, 泄漏来自栅极氧化层,

直接栅极氧化层, 因此源极和栅极

之间的沟道区变得 泄漏,以及隔离泄漏。

正如我说过的, 在高级 CMOS 技术中,

氧化层厚度 不超过 200 埃,

在如此小的 厚度中不会

积累足够的电荷。

因此,基本而言, 隔离泄漏起主导作用。

因此,再说一次, 我们曾讨论的

浅沟隔离或 LOCOS 隔离会收集

更多的电荷,然后 将其集中在某些

高电场区, 基本而言,

隔离泄漏是 主要故障机制。

根据经验, 对于总剂量,

浅沟隔离通常比 LOCOS 更加可靠,至少在低 Vdd 下

是这样。

感谢您的关注。

[音乐播放] 大家好。 我叫 Rob Baumann, 是高可靠性方面的 首席技术专家。 如果在观看本视频之后, 您想了解有关 TI 航天 产品的更多信息, 请访问 ti.com/space。 感谢您的观看。 在本次讲座中,我们 将讨论电离辐射 总剂量及其对 MOSFET 的影响。 好的,基本而言, 电离辐射总剂量 机制与氧化层中的 空穴捕获有关。 这是影响 MOSFET 的 主要模式。 还会创建 界面态。 那么,为了方便 每个人理解, 这是金属氧化物 半导体结构的能带图。 那么,左侧是 栅极电极, 中间是栅极 氧化层,然后 右侧是 硅界面 和硅基片。 那么,很显然, 在水平维度, 我们将讨论器件在 垂直方向的深度或 线性程度。 在垂直方向, 当我们在垂直 方向上行时, 我们具有能量, 这是电子能,因此 我们施加正栅极 电压,该电压 将栅极向下拉, 我们具有该跨越 氧化层的斜坡或 跨越氧化层的电场。 这意味着传导 带中的任何电子 都将跑下该斜坡, 并被栅极收集。 电子再次被吸引到 正栅极电压。 空穴或带正电的 缺陷将以互补 方式朝相反 方向运动, 就像气泡一样朝斜坡上方 漂浮,如果您愿意的话。 现在,当这些器件 接触到辐射时, 所吸收的任何辐射 都会制造电子空穴对。 因此空穴态 和电子会分离, 当然,它们 沿着相反的 方向 加速。 现在,栅极氧化层的 一个特性使它们 对总剂量效应 尤其敏感, 这就是电子 移动性或其 移动效率 远高于空穴。 因此,在存在 电场的情况下, 传导带中的 电子很快地 移动,从而 在整个栅极 氧化层中 分布多个空穴。 现在,它们并不是 完全固定的,但 它们以跳跃机制 缓慢地移动,如这些 绿色箭头所示。 因此它们实际上将陷入 低能级陷阱中 -- 低能级 意味着低能量陷阱 -- 刚好沿着价带边缘, 它们以跳跃的移动 方式,从一个陷阱 移动到另一个 陷阱,移向界面。 我们再次得到 正栅极电压。 因此,如果您愿意的话, 这会将这些空穴向上推。 现在,因为这些 陷阱中通常 束缚有氢或质子, 因此当空穴移动 到陷阱中时, 它会释放一些氢。 因此,实际上, 我们具有双重 空穴向右移动的 效应,当它们释放 质子或氢离子时,这些 氢离子也会由电场 进行加速,向右移动。 现在,这两个粒子 具有两种不同的 行为,从而以不同的 方式影响器件。 一旦空穴 接近界面, 就会有大量所谓的 深能级陷阱。 这些是 处于带隙 中间的陷阱。 因此,栅极氧化层 中的带隙是价带 和传导带 之间的距离, 这些深能级 陷阱,所谓的 深能级陷阱恰好 位于带隙中间。 因此空穴向下 移向界面,然后 被捕获在 栅极氧化层中。 因此,这是准 静止种类的 捕获状态, 因此空穴 被不捕获在 栅极氧化层中, 不再自由移动。 按照类似的方式, 质子输送会继续, 直到质子到达 界面,此时它们 实际上生成 所谓的界面态 缺陷,它们可能会 带正电、带负电 或为中性,具体 取决于缺陷的类型。 现在,这些对于 双极结型晶体管 尤其重要,而对 MOSFET 不那么重要。 正如我们将看到的, 它实际上是正电荷 捕获,会支配 大多数 MOSFET 行为。 好的,在 图的左侧, 我基本上显示了一个 NMO 或 n 沟道器件。 因此,请记住, 这基本上是 我们针对源级和漏级 使用 n 型材料的情况。 n 型材料是 负极或富电子 材料的简称, 因为我们记得, 电子带负电。 沟道区 -- 在该状态下, 它是关闭的 -- 是 P 型或正极, 因此我们有一些空穴。 现在,直到我们在 沟道中获得一些电子, 我们才会实现任何导通。 在典型的 NMOS 操作中, 我们施加正栅极电压, 然后,正如您看到的, 我们反转 表面层, 由于栅极下的 场效应,我们 获得高 浓度电子。 现在,这些 高浓度电子 有效地将源极 连接到漏极, 我们获得很大的 导通,晶体管打开, 好的,沟道导通。 现在,当器件发生 总剂量类型接触时, 我们将得到很多辐射粒子, 在这里用黄色箭头进行了指示。 您将注意到每次 黄色箭头横切 氧化层时, 我们就会 生成正电荷。 再说一次,这是界面附近的 孔穴陷阱,被捕获在深能级 陷阱中。 您可以看到, 孔穴效应 将吸引 更多电子。 或者您可以 考虑它,它就像 您已经稍微施 加了正栅极电压。 实际上,在非常 糟糕的情况下, 您生成了数量 巨大的电荷, 您可以关闭 栅极电压。 因此我们只需 关闭栅极电压, 保留沟道。 因此,这是一个泄漏 电流很大的晶体管。 因此终端沟道仍是打开的, 即使我们已关闭栅极 也是如此。 与此相关的海报 基本是位于右侧的 图片,其中显示了 一个漏水的水龙头。 因此,实际上,电离辐射 总电荷会生成一个泄漏的 NMOS 晶体管。 基本而言,该晶体管 会变得越来越难以关闭, 随着您继续 增加剂量接触, 您会得到越来 越多的电荷, 最终,该晶体管 不再工作。 现在,CMOS 组合了互补的 NMOS 和 PMOS 器件。 因此,如你所想, 由于 PMOS 是对 NMOS 器件的补充或 与其相反,因此, 正如我们说过的, 总剂量效应是相反的。 因此,我不打算讨论 整个系列的幻灯片, 因为我们以前已经讨论过, 但我想展示,在这种情况下, 漏级和源极是正极 或空穴类型的材料, N 基片当然 带负电或 具有大量电子。 如果我们想创建 沟道,换句话说, 如果我们想 打开该器件, 我们基本上必须 施加负栅极电压, 吸引一些空穴,从而 连接源区和漏区。 不幸的是,这里 存在的正电荷 将有效地关闭 我们的 PMOS。 因此我们的 PMOS 晶体管或 P 沟道 实际上会保持关闭, 即使栅极电压接地 也是如此,这对于 PMOS 是打开状态。 因此,这会受到辐射, 我们无法打开晶体管。 因此您可以将 PMOS 晶体管上的 电离辐射总剂量 电荷效应比作一个 生锈的水龙头。 基本而言,它会 变得越来越难以 使任何电流流动, 直到晶体管最终 不再工作。 好的。 因此,在 CMOS 中,正如我说过的, 我们有一个 n 沟道器件和 一个 p 沟道器件。 再说一次,p 沟道器件 会变得更加难以打开, 因此它将变得 泄漏更少的剂量, 而 n 沟道变得 越来越泄漏。 嗯,我没有具体 讲过泄漏是 从哪儿来的。 在我在之前的幻灯片中 讲过的示例中,我们 讨论了源区 和漏区 之间的中间 沟道导通。 但是,正如您可以 在该图中看到的, 电荷可以通过其他 两个路径泄漏。 实际上,如果 绝缘层变得 带电,那么 在这里,两个 晶体管之间的隔离层 或绝缘层是所谓的浅沟 隔离。 这是两种类型之一,我将 在后面的幻灯片中讨论 这两种类型。 但该红色区域 具有很大的量, 您可以捕获大量的 电荷,然后它们在电场下 可以在沟道的 边缘或刚好在 沟道的旁边积累。 因此您得到潜在的 沿着 3 的泄漏路径, 以及隔离层下 通向 n 阱的泄漏 路径,如泄漏 路径 2 中所示。 那么 IV 看起来是什么样子的? 嗯,这是一个 n 沟道 IV。 蓝色的曲线 表示 n 沟道本身, 假设不存在 隔离泄漏。 因此这里的第一条 曲线 PRERAD,蓝色曲线, 是典型的 NMOS 特征。 我们将栅极-源极 电压调为正电压, 我们在沟道中 吸引电子,然后 我们连接源极 和漏极并获得 高导通状态。 现在,一旦我们 对器件进行辐照, 我们会再次 生成正电荷, 因此阈值电压下降。 您可以看到 曲线移向左侧。 这是预期行为, 它意味着晶体管 开始泄漏或 其更容易打开。 对于较小的栅极 电压,您会获得 相同量的导通。 在现代晶体管中 -- 现代指低于 100 纳米、100 埃或 200 埃 厚度的栅极 氧化层 -- 该效应 是最低的。 因此,对于大多数应用, VT 漂移几乎可以忽略。 现在机制 2 和 3 中泄漏变得很重要, 这些机制由绿色 曲线进行定义。 这是隔离泄漏, 因此它是由 隔离上的 该重叠栅极 导致的寄生晶体管, 可以打开隔离泄漏。 在存在辐射的情况下, 该曲线会向左移动。 因此该绿色曲线, 在没有辐射的情况下, 只有达到 8 伏 才会打开,对于 该特定的技术, 将是很好的隔离。 不过,一旦我们 使其接触辐射, 正电荷就会 被捕获,在 NMOS 区域,您将获得 极大量的泄漏。 您将注意到,该隔离 泄漏,假设处于 0 伏, 在正常情况下 -- 我们再次看看 这里的蓝色 曲线 -- 该 NMOS 晶体管的泄漏 大约为 5 或 6 皮安。 不过,由于辐射 之后的隔离泄漏, 我们处于微安范围内。 因此几乎是六个 数量级的泄漏。 这实际上可能会 为器件带来灾难, 因为 IDDQ 会 增加到超标, 而您将失去功能。 因此,总剂量 实际损坏 CMOS 器件,至少是 现代器件的 主要途径是通过 机制 3 或 2,此时 隔离泄漏起主导 作用,由于电流规格 或实际电流功能, 我们基本上会失败。 请注意,我提到过 浅沟隔离,但我 没有提到 另一种类型。 有两种类型的隔离。 第一种比较 成熟,是局部 场氧化或 针对局域 场氧化的 LOCOS。 这基本上是已生长的 氧化层,它具有非常 独特的形状。 因为硅在氧化层 生长时会被消耗, 因此您会对氧化层 进行一定深度的渗透, 但氧化层还会 升高到硅层以上。 问题就在这里, 在氧化层的边缘, 存在一个所谓的 鸟嘴区域,该区域 集中了电场, 实际上会在 该区域 捕获大量 电荷或积累 大量正电荷。 猜猜会怎么样? 由于您在这里 积累了大量正电荷, 您将影响 下面的硅 基片并导致 在隔离的边缘 产生泄漏沟道。 事实上,这是 局部场氧化 或 LOCOS,所谓的 LOCOS 的最大故障模式。 现在,我提到过的 另一种类型的隔离, 它在现代 技术中更常见。 这是浅沟 隔离。 基本而言, 这是不同的。 它不是已生长的氧化层。 基本而言,我们在 晶体管之间挖一个 条,以隔离 它们,然后 我们使用氧化层和 其他电介质回填沟。 现在,这还可能 在边缘存在问题。 如果电场线 过于集中或 依赖于层, 所使用的 不同层,您可能 会积累电荷。 因此,使用 STI 不能保证性能。 但正如您将在 右侧的图中看到的 -- 这是一篇来自 Sandia 的论文 -- 他们 采用了一些 或多种商业 技术并对其 进行了总剂量测试。 他们按照 LOCOS、该局部 氧化类型和浅沟 隔离对这些技术 进行了划分。 很显然,浅沟 隔离对总剂量 性能具有 很大的帮助。 因此黄色的线向 我们展示了大约 100 k -- 或者黄色 区域低于 100 krad。 正如这里所说的,100 krad 对于大多数航天应用而言 是很好的,甚至是 50 krad。 但在某些情况下,LOCOS 很难达到 10 krad 以上, 正如您从这些 较低的点中看到的。 一旦您转向 浅沟隔离, 您通常会 达到几百 krad。 现在,我应该提到, 这些也是较低的 电压技术。 您可以从 原始的能带 图和有关电离辐射 总剂量的讨论中回想起, 电场对于定义 该效应而言 很重要。 因此,如果我们具有 更高的电压部分, 它将对总剂量 更加敏感,因为 它可以移动 其中的更多电荷。 好的。 最后,正如我们提到过的, 在行为与正栅极电压相似的 氧化层中, 该效应的 主要推动因素是 空穴、正电荷捕获。 NMOS 变得 更加泄漏 -- 换句话说,打开它 所需的栅极电压更小 -- 而 PMOS 变得 更难以打开, 打开它所需的 栅极电压更大。 从根本上讲, 之所以产生 功能故障,是因为 NMOS 开始越来越泄露,最终, 您的电流规格 失败,或者在极端 情况下,您的 功能不起作用。 正如我们看到的, 泄漏来自栅极氧化层, 直接栅极氧化层, 因此源极和栅极 之间的沟道区变得 泄漏,以及隔离泄漏。 正如我说过的, 在高级 CMOS 技术中, 氧化层厚度 不超过 200 埃, 在如此小的 厚度中不会 积累足够的电荷。 因此,基本而言, 隔离泄漏起主导作用。 因此,再说一次, 我们曾讨论的 浅沟隔离或 LOCOS 隔离会收集 更多的电荷,然后 将其集中在某些 高电场区, 基本而言, 隔离泄漏是 主要故障机制。 根据经验, 对于总剂量, 浅沟隔离通常比 LOCOS 更加可靠,至少在低 Vdd 下 是这样。 感谢您的关注。

[音乐播放]

大家好。

我叫 Rob Baumann, 是高可靠性方面的

首席技术专家。

如果在观看本视频之后, 您想了解有关 TI 航天

产品的更多信息, 请访问 ti.com/space。

感谢您的观看。

在本次讲座中,我们 将讨论电离辐射

总剂量及其对 MOSFET 的影响。

好的,基本而言, 电离辐射总剂量

机制与氧化层中的 空穴捕获有关。

这是影响 MOSFET 的 主要模式。

还会创建 界面态。

那么,为了方便 每个人理解,

这是金属氧化物 半导体结构的能带图。

那么,左侧是 栅极电极,

中间是栅极 氧化层,然后

右侧是 硅界面

和硅基片。

那么,很显然, 在水平维度,

我们将讨论器件在 垂直方向的深度或

线性程度。

在垂直方向, 当我们在垂直

方向上行时, 我们具有能量,

这是电子能,因此 我们施加正栅极

电压,该电压 将栅极向下拉,

我们具有该跨越 氧化层的斜坡或

跨越氧化层的电场。

这意味着传导 带中的任何电子

都将跑下该斜坡, 并被栅极收集。

电子再次被吸引到 正栅极电压。

空穴或带正电的 缺陷将以互补

方式朝相反 方向运动,

就像气泡一样朝斜坡上方 漂浮,如果您愿意的话。

现在,当这些器件 接触到辐射时,

所吸收的任何辐射 都会制造电子空穴对。

因此空穴态 和电子会分离,

当然,它们 沿着相反的

方向 加速。

现在,栅极氧化层的 一个特性使它们

对总剂量效应 尤其敏感,

这就是电子 移动性或其

移动效率 远高于空穴。

因此,在存在 电场的情况下,

传导带中的 电子很快地

移动,从而 在整个栅极

氧化层中 分布多个空穴。

现在,它们并不是 完全固定的,但

它们以跳跃机制 缓慢地移动,如这些

绿色箭头所示。

因此它们实际上将陷入 低能级陷阱中 -- 低能级

意味着低能量陷阱 -- 刚好沿着价带边缘,

它们以跳跃的移动 方式,从一个陷阱

移动到另一个 陷阱,移向界面。

我们再次得到 正栅极电压。

因此,如果您愿意的话, 这会将这些空穴向上推。

现在,因为这些 陷阱中通常

束缚有氢或质子, 因此当空穴移动

到陷阱中时, 它会释放一些氢。

因此,实际上, 我们具有双重

空穴向右移动的 效应,当它们释放

质子或氢离子时,这些 氢离子也会由电场

进行加速,向右移动。

现在,这两个粒子 具有两种不同的

行为,从而以不同的 方式影响器件。

一旦空穴 接近界面,

就会有大量所谓的 深能级陷阱。

这些是 处于带隙

中间的陷阱。

因此,栅极氧化层 中的带隙是价带

和传导带 之间的距离,

这些深能级 陷阱,所谓的

深能级陷阱恰好 位于带隙中间。

因此空穴向下 移向界面,然后

被捕获在 栅极氧化层中。

因此,这是准 静止种类的

捕获状态, 因此空穴

被不捕获在 栅极氧化层中,

不再自由移动。

按照类似的方式, 质子输送会继续,

直到质子到达 界面,此时它们

实际上生成 所谓的界面态

缺陷,它们可能会 带正电、带负电

或为中性,具体 取决于缺陷的类型。

现在,这些对于 双极结型晶体管

尤其重要,而对 MOSFET 不那么重要。

正如我们将看到的, 它实际上是正电荷

捕获,会支配 大多数 MOSFET 行为。

好的,在 图的左侧,

我基本上显示了一个 NMO 或 n 沟道器件。

因此,请记住, 这基本上是

我们针对源级和漏级 使用 n 型材料的情况。

n 型材料是 负极或富电子

材料的简称, 因为我们记得,

电子带负电。

沟道区 -- 在该状态下,

它是关闭的 -- 是 P 型或正极,

因此我们有一些空穴。

现在,直到我们在 沟道中获得一些电子,

我们才会实现任何导通。

在典型的 NMOS 操作中,

我们施加正栅极电压, 然后,正如您看到的,

我们反转 表面层,

由于栅极下的 场效应,我们

获得高 浓度电子。

现在,这些 高浓度电子

有效地将源极 连接到漏极,

我们获得很大的 导通,晶体管打开,

好的,沟道导通。

现在,当器件发生 总剂量类型接触时,

我们将得到很多辐射粒子, 在这里用黄色箭头进行了指示。

您将注意到每次 黄色箭头横切

氧化层时, 我们就会

生成正电荷。

再说一次,这是界面附近的 孔穴陷阱,被捕获在深能级

陷阱中。

您可以看到, 孔穴效应

将吸引 更多电子。

或者您可以 考虑它,它就像

您已经稍微施 加了正栅极电压。

实际上,在非常 糟糕的情况下,

您生成了数量 巨大的电荷,

您可以关闭 栅极电压。

因此我们只需 关闭栅极电压,

保留沟道。

因此,这是一个泄漏 电流很大的晶体管。

因此终端沟道仍是打开的, 即使我们已关闭栅极

也是如此。

与此相关的海报 基本是位于右侧的

图片,其中显示了 一个漏水的水龙头。

因此,实际上,电离辐射 总电荷会生成一个泄漏的

NMOS 晶体管。

基本而言,该晶体管 会变得越来越难以关闭,

随着您继续 增加剂量接触,

您会得到越来 越多的电荷,

最终,该晶体管 不再工作。

现在,CMOS 组合了互补的 NMOS 和 PMOS 器件。

因此,如你所想, 由于 PMOS 是对

NMOS 器件的补充或 与其相反,因此,

正如我们说过的, 总剂量效应是相反的。

因此,我不打算讨论 整个系列的幻灯片,

因为我们以前已经讨论过, 但我想展示,在这种情况下,

漏级和源极是正极 或空穴类型的材料,

N 基片当然 带负电或

具有大量电子。

如果我们想创建 沟道,换句话说,

如果我们想 打开该器件,

我们基本上必须 施加负栅极电压,

吸引一些空穴,从而 连接源区和漏区。

不幸的是,这里 存在的正电荷

将有效地关闭 我们的 PMOS。

因此我们的 PMOS 晶体管或 P 沟道

实际上会保持关闭, 即使栅极电压接地

也是如此,这对于 PMOS 是打开状态。

因此,这会受到辐射, 我们无法打开晶体管。

因此您可以将 PMOS 晶体管上的

电离辐射总剂量 电荷效应比作一个

生锈的水龙头。

基本而言,它会 变得越来越难以

使任何电流流动, 直到晶体管最终

不再工作。

好的。

因此,在 CMOS 中,正如我说过的, 我们有一个 n 沟道器件和

一个 p 沟道器件。

再说一次,p 沟道器件 会变得更加难以打开,

因此它将变得 泄漏更少的剂量,

而 n 沟道变得 越来越泄漏。

嗯,我没有具体 讲过泄漏是

从哪儿来的。

在我在之前的幻灯片中 讲过的示例中,我们

讨论了源区 和漏区

之间的中间 沟道导通。

但是,正如您可以 在该图中看到的,

电荷可以通过其他 两个路径泄漏。

实际上,如果 绝缘层变得

带电,那么 在这里,两个

晶体管之间的隔离层 或绝缘层是所谓的浅沟

隔离。

这是两种类型之一,我将 在后面的幻灯片中讨论

这两种类型。

但该红色区域 具有很大的量,

您可以捕获大量的 电荷,然后它们在电场下

可以在沟道的 边缘或刚好在

沟道的旁边积累。

因此您得到潜在的 沿着 3 的泄漏路径,

以及隔离层下 通向 n 阱的泄漏

路径,如泄漏 路径 2 中所示。

那么 IV 看起来是什么样子的?

嗯,这是一个 n 沟道 IV。

蓝色的曲线 表示 n 沟道本身,

假设不存在 隔离泄漏。

因此这里的第一条 曲线 PRERAD,蓝色曲线,

是典型的 NMOS 特征。

我们将栅极-源极 电压调为正电压,

我们在沟道中 吸引电子,然后

我们连接源极 和漏极并获得

高导通状态。

现在,一旦我们 对器件进行辐照,

我们会再次 生成正电荷,

因此阈值电压下降。

您可以看到 曲线移向左侧。

这是预期行为, 它意味着晶体管

开始泄漏或 其更容易打开。

对于较小的栅极 电压,您会获得

相同量的导通。

在现代晶体管中 -- 现代指低于

100 纳米、100 埃或 200 埃

厚度的栅极 氧化层 -- 该效应

是最低的。

因此,对于大多数应用, VT 漂移几乎可以忽略。

现在机制 2 和 3 中泄漏变得很重要,

这些机制由绿色 曲线进行定义。

这是隔离泄漏, 因此它是由

隔离上的 该重叠栅极

导致的寄生晶体管, 可以打开隔离泄漏。

在存在辐射的情况下, 该曲线会向左移动。

因此该绿色曲线, 在没有辐射的情况下,

只有达到 8 伏 才会打开,对于

该特定的技术, 将是很好的隔离。

不过,一旦我们 使其接触辐射,

正电荷就会 被捕获,在 NMOS

区域,您将获得 极大量的泄漏。

您将注意到,该隔离 泄漏,假设处于 0 伏,

在正常情况下 -- 我们再次看看

这里的蓝色 曲线 -- 该 NMOS

晶体管的泄漏 大约为 5 或 6

皮安。

不过,由于辐射 之后的隔离泄漏,

我们处于微安范围内。

因此几乎是六个 数量级的泄漏。

这实际上可能会 为器件带来灾难,

因为 IDDQ 会 增加到超标,

而您将失去功能。

因此,总剂量 实际损坏 CMOS

器件,至少是 现代器件的

主要途径是通过 机制 3 或 2,此时

隔离泄漏起主导 作用,由于电流规格

或实际电流功能, 我们基本上会失败。

请注意,我提到过 浅沟隔离,但我

没有提到 另一种类型。

有两种类型的隔离。

第一种比较 成熟,是局部

场氧化或 针对局域

场氧化的 LOCOS。

这基本上是已生长的 氧化层,它具有非常

独特的形状。

因为硅在氧化层 生长时会被消耗,

因此您会对氧化层 进行一定深度的渗透,

但氧化层还会 升高到硅层以上。

问题就在这里, 在氧化层的边缘,

存在一个所谓的 鸟嘴区域,该区域

集中了电场, 实际上会在

该区域 捕获大量

电荷或积累 大量正电荷。

猜猜会怎么样?

由于您在这里 积累了大量正电荷,

您将影响 下面的硅

基片并导致 在隔离的边缘

产生泄漏沟道。

事实上,这是 局部场氧化

或 LOCOS,所谓的 LOCOS 的最大故障模式。

现在,我提到过的 另一种类型的隔离,

它在现代 技术中更常见。

这是浅沟 隔离。

基本而言, 这是不同的。

它不是已生长的氧化层。

基本而言,我们在 晶体管之间挖一个

条,以隔离 它们,然后

我们使用氧化层和 其他电介质回填沟。

现在,这还可能 在边缘存在问题。

如果电场线 过于集中或

依赖于层, 所使用的

不同层,您可能 会积累电荷。

因此,使用 STI 不能保证性能。

但正如您将在 右侧的图中看到的 --

这是一篇来自 Sandia 的论文 -- 他们

采用了一些 或多种商业

技术并对其 进行了总剂量测试。

他们按照 LOCOS、该局部

氧化类型和浅沟 隔离对这些技术

进行了划分。

很显然,浅沟 隔离对总剂量

性能具有 很大的帮助。

因此黄色的线向 我们展示了大约 100

k -- 或者黄色 区域低于 100 krad。

正如这里所说的,100 krad 对于大多数航天应用而言

是很好的,甚至是 50 krad。

但在某些情况下,LOCOS 很难达到 10 krad 以上,

正如您从这些 较低的点中看到的。

一旦您转向 浅沟隔离,

您通常会 达到几百 krad。

现在,我应该提到, 这些也是较低的

电压技术。

您可以从 原始的能带

图和有关电离辐射 总剂量的讨论中回想起,

电场对于定义 该效应而言

很重要。

因此,如果我们具有 更高的电压部分,

它将对总剂量 更加敏感,因为

它可以移动 其中的更多电荷。

好的。

最后,正如我们提到过的, 在行为与正栅极电压相似的

氧化层中, 该效应的

主要推动因素是 空穴、正电荷捕获。

NMOS 变得 更加泄漏 --

换句话说,打开它 所需的栅极电压更小 --

而 PMOS 变得 更难以打开,

打开它所需的 栅极电压更大。

从根本上讲, 之所以产生

功能故障,是因为 NMOS 开始越来越泄露,最终,

您的电流规格 失败,或者在极端

情况下,您的 功能不起作用。

正如我们看到的, 泄漏来自栅极氧化层,

直接栅极氧化层, 因此源极和栅极

之间的沟道区变得 泄漏,以及隔离泄漏。

正如我说过的, 在高级 CMOS 技术中,

氧化层厚度 不超过 200 埃,

在如此小的 厚度中不会

积累足够的电荷。

因此,基本而言, 隔离泄漏起主导作用。

因此,再说一次, 我们曾讨论的

浅沟隔离或 LOCOS 隔离会收集

更多的电荷,然后 将其集中在某些

高电场区, 基本而言,

隔离泄漏是 主要故障机制。

根据经验, 对于总剂量,

浅沟隔离通常比 LOCOS 更加可靠,至少在低 Vdd 下

是这样。

感谢您的关注。

手机看

扫码用手机观看

视频简介

视频简介

总电离剂量对MOSFET的影响

所属课程:TID基础知识

发布时间:2019.03.11

视频集数:3

本节视频时长:00:16:44

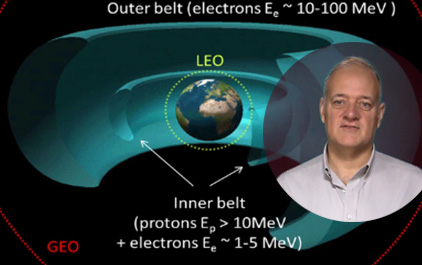

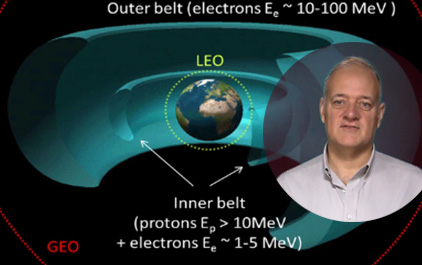

航空航天设计界最常见的辐射要求是总电离剂量(TID),也称为总剂量。当电子和质子在用于电子器件中的绝缘的介电层中产生过量电荷时,引起总剂量效应。总剂量效应是累积的,并且在装置退化变得明显之前需要长期暴露于许多辐射事件。因此,卫星或航天器中的电子设备随着时间的推移会累积TID损害,因为它们在连续的辐射水平下运行。虽然电子在绝缘体中是可移动的,但是空穴(带正电的原子)必须通过断开键而移动并且可能陷入缺陷中。器件绝缘体中积累的正电荷的结果导致降级和/或器件故障。氧化物电荷累积影响半导体电路中使用的晶体管的电流 - 电压特性。晶体管的正确操作依赖于当栅极电压通过阈值时将其从低电导(关断)状态切换到高电导(导通)状态的能力。长时间暴露于TID辐射会使阈值电压发生偏移,使得晶体管更容易或更难切换。辐射还可能增加漏电流,导致晶体管的导通和截止状态变得不太可区分。这两种效应都可能最终导致电路故障。对于我们的太空产品,这些影响已在我们的TID辐射报告中进行了表征和总结。

未学习 TID基础知识

未学习 TID基础知识

未学习 双极结转移(BJT)的总电离剂量效应

未学习 双极结转移(BJT)的总电离剂量效应

未学习 总电离剂量对MOSFET的影响

未学习 总电离剂量对MOSFET的影响