电源管理

最新课程

- 如何利用高速比较器优化系统设计

- TPS546D24S 和 TPSM8S6C24 中的扩展安全功能

- TI 高精度实验室 - 仪表放大器

- 高侧开关深入研讨

- TI 高精度实验室 - 微控制器 (MCU)

- TI 高精度实验室 - CPU内核

- 三种直流/直流控制模式的实际比较

- 电源多路复用器深度培训

- TI Edge AI Studio:用于边缘 AI 设计的免费软件开发工具

- Edge AI Studio 概述

热门课程

工业及汽车系统的低EMI电源变换器设计(四)通过优化PCB layout 有效降低EMI

欢迎收看工业及汽车系统的

低 EMI 电源变换器设计第四讲

通过优化 PCB layout

有效降低 EMI

上一讲中我们有提到如何有效降低 EMI

在这一讲中我们将重点讨论

如何通过优化 PCB layout

来减小 EMI

这里给出三个关键的步骤

第一个

我们首先要定位到

哪些节点是高的 di/dt

然后我们要尽量地

减少 di/dt 环路的面积

最后就是要把一些敏感的信号保护起来

让它们远离噪声源

这是一个经典的 buck 电路

首先我们来看看噪声源在什么地方

当上管导通时

电流会从输入电容的正端经过上管流经电感

经过输出电容或者负载回到输入电容

也就是图中所显示的红色的路径

当上管关闭下管导通时

由于电感的电流不能突变

电流继续流经电感输出电容和负载

经过下管

流回到电感

流回到电感

如图中粉色路径所示

我们知道这两条路径都是大的电流

但是真正大的 di/dt 的环路

并不在这两条路径当中

而是由图中虚线所示

因为这两个环路当中

这一部分红色和粉色是重叠的

它们电流并没有特别大的变化

而粉色的这条路径当中

当上管导通和上管不导通的时候

它的电流分别是

从有电流到没有电流的一个突变

所以这个环路才是真正的大的 di/dt

认识到这个环路才是

真正产生大的 di/dt 的环路

那么我们的电容就不能这么放了

而应该是像下图所示

使得我们这个虚线的这个环路的面积足够小

从而更有效地减小 di/dt 的环路面积

同时我们要让

输入电容和上管下管放在同一层上

避免用过孔连接

因为过孔在高频的电流上也会

表现出比较大的电感的特性

同时我们要把信号地和电源地分开

为了大家对这个理论有个更直观的了解

我们做了以下实验

这是一颗集成了上管和下管的同步 DCDC

在第一个例子当中

我们让输入电容尽量地靠近 IC

也就是说我们要让

这个高的 di/dt 的环路保持尽量地小

我们来观测三个参数

第一个是开关节点的峰值电压

第二个是输出电压的纹波

还有就是对这一个板子进行一个传导的测试

我们看到峰值电压为 16.2V

V2 的峰值为 64mV

同时我们看到传导的最高值大约为 45dB

对于同一个板子

我们做的第二个实验是

让本来很靠近 IC 的这个电容

放得比较远

其它东西都没有变

我们重新测试刚刚所测的那三个参数

SW 电压从刚刚的16.2V

变到现在的 18.1V

V2 的纹波电压

从刚刚的 64mV 变到 140mV

而传导测试的结果则

从刚刚的 45dB 变到现在的 50dB

所以大家很清楚地看到

输入电容与 IC 构成的环路面积

将直接的影响到我们电路参数的性能

也直接的影响到了传导 EMI 测试的结果

有很多时候虽然我们知道

我们要尽量地把输入电容靠近 IC

但是如果 PINOUT 不给力

恐怕也很难做到

所以 IC 的 PINOUT 设计

对于我们 PCB 的优化非常重要

我们来看这一个例子,这是 LN43602

输入和地在 IC 的右上角

输入电容可以比较方便地与它们靠得很近

同时开关节点放在左上角

可以比较方便地形成一个小的环路

同时 BOOT 电容就在 SW 的旁边

比较方便 BOOT 电容的连接

同时我们看到 FB 是

反馈环路当中比较敏感的点

它是运放的输入端,也是一个高阻点

所以它被安排到远离 SW

也就是说,它被安排到远离开关节点

这样能够很好地实现保护

这是另外一个例子

大家可以看到输入电容与 IC 的输入

和地之间也比较方便地可以靠得很近

从而实现大的 di/dt 环路的最小化

这是一个 PCB 优化的非常好的例子

我们来看一看

首先输入电容和 IC 尽可能地靠近

实现输入环路面积的最小化

黄色框框上面是电感

大家可以注意到

电感的 SW 端和输出端中间的铜箔

被挖掉了一块

其主要的目的是为了减小 SW 点

到输出点的寄生电容

主要是为了减少 SW 对输出的耦合

反馈电阻非常靠近反馈节点

并且远离开关节点

底层全部铺铜

以便更好地屏蔽和磁场的抵消

我们经常会说

底板全部铺铜

为了做到最好的屏蔽

那究竟为什么会有这个原理呢

我们来看一下

这里有一个例子

图中有两个 PCB 板都是双层板

上面我们讨论了

通过减小关键环路面积来减小 EMI

现在我们来讨论

如何利用铺地的方法来减小 EMI

我们都知道 PCB layout

常常利用铺地来实现屏蔽

其实一块完整的金属不仅可以实现屏蔽

同时也可以提供最短的电流返回路径

以实现环路面积的最小化

我们来看看这个例子

这里有两块 PCB 都是双层板

顶层的信号线如绿线所示

在左边的 PCB 板中

底层是一块完整的金属

而在右边的 PCB 板中

底层的金属并不完整

有一个以信号线垂直的切口

我们先来看看左边的板子

但信号从左到右流经顶层的信号线

并试图通过底层的金属返回时

它会按照主看最小的原理来选择返回路径

所以返回路径出现在信号线的正下方

以顶层的信号所形成的环路面积是最小的

而且由于两个信号方向相反

电流所形成的磁场

在很大的程度上是互相抵消的

所以这样的布线效果

对 EMI 是非常有利的

而在右边的板子中

当电流在寻找最短的路径时

由于下方的开口

电流只能绕行到最近的通路

如图所示

这样无意中就形成了一个较大的电流环路

因此 EMI 的性能就远不如左边的板子了

所以我们在铺地时最好使用一块完整的地

如果一定要切开

以尽量的保证上层信号线所对应的地方

没有断开

以达到最优的 EMI 效果

这一讲就讲到这, 谢谢

-

未学习 1.1 碳化硅和氮化镓器件的介绍, 应用及优势

未学习 1.1 碳化硅和氮化镓器件的介绍, 应用及优势

-

未学习 1.2 驱动器设计考虑

未学习 1.2 驱动器设计考虑

-

未学习 1.3 开关性能

未学习 1.3 开关性能

-

未学习 1.4 硬开关,软开关案例

未学习 1.4 硬开关,软开关案例

-

未学习 1.5 测量

未学习 1.5 测量

-

未学习 1.6 仿真及总结

未学习 1.6 仿真及总结

-

未学习 1.1 TI PMBus简介课程

未学习 1.1 TI PMBus简介课程

-

未学习 1.2 TI PMBus简介课程(一)

未学习 1.2 TI PMBus简介课程(一)

-

未学习 1.3 TI PMBus简介课程(二)

未学习 1.3 TI PMBus简介课程(二)

-

未学习 1.4 TI PMBus简介课程(三)

未学习 1.4 TI PMBus简介课程(三)

-

未学习 USB Type C介绍

未学习 USB Type C介绍

-

未学习 USB PD介绍

未学习 USB PD介绍

-

未学习 45W单端口AC/DC方案介绍

未学习 45W单端口AC/DC方案介绍

-

未学习 45W双端口AC/DC方案介绍

未学习 45W双端口AC/DC方案介绍

-

未学习 1.1高频降压变化器的局限

未学习 1.1高频降压变化器的局限

-

未学习 1.2串联电容降压变换器的工作模式

未学习 1.2串联电容降压变换器的工作模式

-

未学习 1.3串联电容降压变换器的工作模式续

未学习 1.3串联电容降压变换器的工作模式续

-

未学习 1.4串联电容降压变换器的主要优点

未学习 1.4串联电容降压变换器的主要优点

-

未学习 1.5串联电容降压变换器的测试结果

未学习 1.5串联电容降压变换器的测试结果

-

未学习 1.6串联电容降压变换器的设计要点

未学习 1.6串联电容降压变换器的设计要点

-

未学习 1.7串联电容降压变换器的PCB

未学习 1.7串联电容降压变换器的PCB

-

未学习 1.1反激式变压器的概论

未学习 1.1反激式变压器的概论

-

未学习 1.2反激式变压器的磁心损耗

未学习 1.2反激式变压器的磁心损耗

-

未学习 1.3反激式变压器的铜损

未学习 1.3反激式变压器的铜损

-

未学习 1.4反激式变压器的漏感和嵌位电压

未学习 1.4反激式变压器的漏感和嵌位电压

-

未学习 1.5减小反激式变压器的EMI性能

未学习 1.5减小反激式变压器的EMI性能

-

未学习 双向DC-DC 变换器拓扑的对比与设计(1) – 应用概览

未学习 双向DC-DC 变换器拓扑的对比与设计(1) – 应用概览

-

未学习 双向DC-DC 变换器拓扑的对比与设计(2) – 拓扑比较

未学习 双向DC-DC 变换器拓扑的对比与设计(2) – 拓扑比较

-

未学习 双向DC-DC 变换器拓扑的对比与设计(3) – UCD3138控制方案

未学习 双向DC-DC 变换器拓扑的对比与设计(3) – UCD3138控制方案

-

未学习 双向DC-DC 变换器拓扑的对比与设计(4) – 测试结果的比较

未学习 双向DC-DC 变换器拓扑的对比与设计(4) – 测试结果的比较

-

未学习 双向DC-DC 变换器拓扑的对比与设计(5) – 性能及总结

未学习 双向DC-DC 变换器拓扑的对比与设计(5) – 性能及总结

-

未学习 电源系统设计工具

未学习 电源系统设计工具

-

未学习 工业及汽车系统的低EMI电源变换器设计(一)课程概览

未学习 工业及汽车系统的低EMI电源变换器设计(一)课程概览

-

未学习 工业及汽车系统的低EMI电源变换器设计(二)工业及汽车运用DCDC的主要特点

未学习 工业及汽车系统的低EMI电源变换器设计(二)工业及汽车运用DCDC的主要特点

-

未学习 工业及汽车系统的低EMI电源变换器设计(三)降低开关电源EMI干扰的方法

未学习 工业及汽车系统的低EMI电源变换器设计(三)降低开关电源EMI干扰的方法

-

未学习 工业及汽车系统的低EMI电源变换器设计(四)通过优化PCB layout 有效降低EMI

未学习 工业及汽车系统的低EMI电源变换器设计(四)通过优化PCB layout 有效降低EMI

-

未学习 工业及汽车系统的低EMI电源变换器设计(五)通过控制开关点的Slew Rate有效降低EMI

未学习 工业及汽车系统的低EMI电源变换器设计(五)通过控制开关点的Slew Rate有效降低EMI

-

未学习 工业及汽车系统的低EMI电源变换器设计(六)通过频率抖动有效降低EMI

未学习 工业及汽车系统的低EMI电源变换器设计(六)通过频率抖动有效降低EMI

-

未学习 工业及汽车系统的低EMI电源变换器设计(七)通过增加EMI 滤波器有效降低EMI

未学习 工业及汽车系统的低EMI电源变换器设计(七)通过增加EMI 滤波器有效降低EMI

-

未学习 工业及汽车系统的低EMI电源变换器设计(八)— EMI 优化技巧小结

未学习 工业及汽车系统的低EMI电源变换器设计(八)— EMI 优化技巧小结

-

未学习 1.1 开关模式电源转换器补偿简单易行 — 补偿的原因和目的

未学习 1.1 开关模式电源转换器补偿简单易行 — 补偿的原因和目的

-

未学习 1.2 开关模式电源转换器补偿简单易行 —零点和极点

未学习 1.2 开关模式电源转换器补偿简单易行 —零点和极点

-

未学习 1.3 开关模式电源转换器补偿简单易行 —功率级第一部分

未学习 1.3 开关模式电源转换器补偿简单易行 —功率级第一部分

-

未学习 1.4 开关模式电源转换器补偿简单易行 —功率级第二部分

未学习 1.4 开关模式电源转换器补偿简单易行 —功率级第二部分

-

未学习 1.5 开关模式电源转换器补偿简单易行 —反馈回路介绍

未学习 1.5 开关模式电源转换器补偿简单易行 —反馈回路介绍

-

未学习 1.6 开关模式电源转换器补偿简单易行 —补偿实例

未学习 1.6 开关模式电源转换器补偿简单易行 —补偿实例

-

未学习 1.7 开关模式电源转换器补偿简单易行 —实际应用限制和常见问题第一部分

未学习 1.7 开关模式电源转换器补偿简单易行 —实际应用限制和常见问题第一部分

-

未学习 1.8 开关模式电源转换器补偿简单易行 —实际应用限制和常见问题第二部分

未学习 1.8 开关模式电源转换器补偿简单易行 —实际应用限制和常见问题第二部分

-

未学习 1.1 升降压变换器的应用,实现方式和拓扑

未学习 1.1 升降压变换器的应用,实现方式和拓扑

-

未学习 1.2 LM5175控制的升降压变换器工作原理

未学习 1.2 LM5175控制的升降压变换器工作原理

-

未学习 1.3 设计举例

未学习 1.3 设计举例

-

未学习 1.4 PCB板布局介绍

未学习 1.4 PCB板布局介绍

-

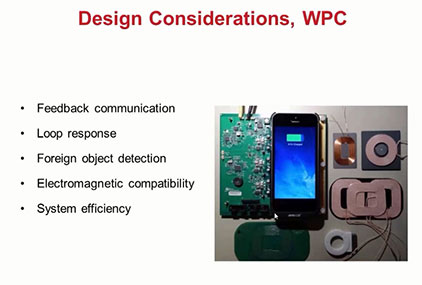

未学习 无线传输功率(1)

未学习 无线传输功率(1)

-

未学习 无线传输功率(2)

未学习 无线传输功率(2)

-

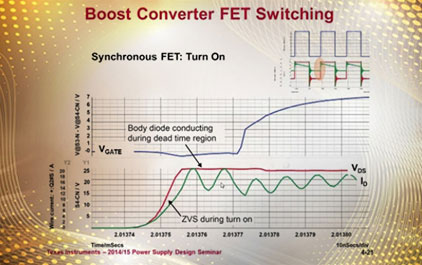

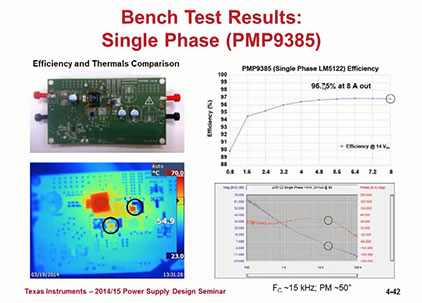

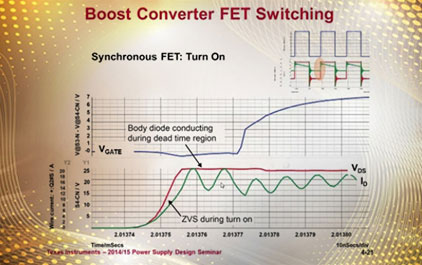

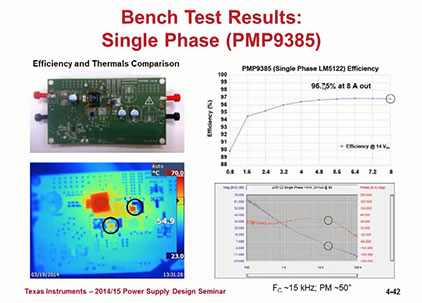

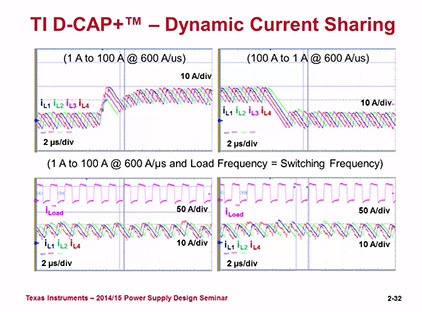

未学习 多相同步升压型变换器(1)

未学习 多相同步升压型变换器(1)

-

未学习 多相同步升压型变换器(2)

未学习 多相同步升压型变换器(2)

-

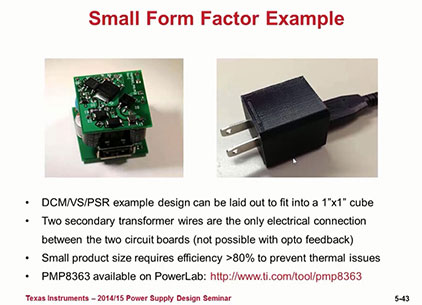

未学习 小功率的AC/DC变换器的控制难题(1)

未学习 小功率的AC/DC变换器的控制难题(1)

-

未学习 小功率的AC/DC变换器的控制难题(2)

未学习 小功率的AC/DC变换器的控制难题(2)

-

未学习 德州仪器电源新产品

未学习 德州仪器电源新产品

-

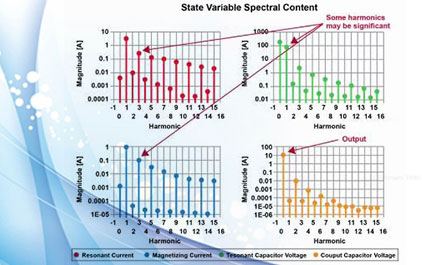

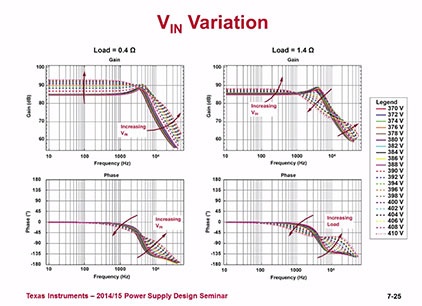

未学习 LLC 变换器小信号模型分析(上)

未学习 LLC 变换器小信号模型分析(上)

-

未学习 LLC 变换器小信号模型分析(下)

未学习 LLC 变换器小信号模型分析(下)

-

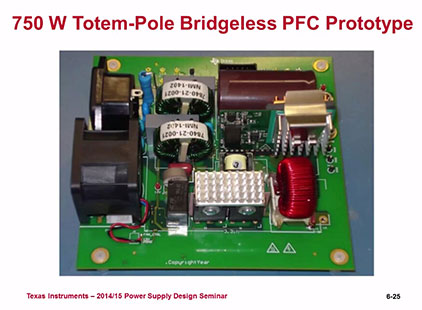

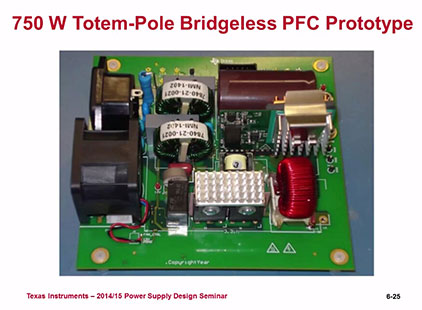

未学习 基于氮化镓的图腾柱无桥 PFC(CCM)(上)

未学习 基于氮化镓的图腾柱无桥 PFC(CCM)(上)

-

未学习 基于氮化镓的图腾柱无桥 PFC(CCM)(下)

未学习 基于氮化镓的图腾柱无桥 PFC(CCM)(下)

-

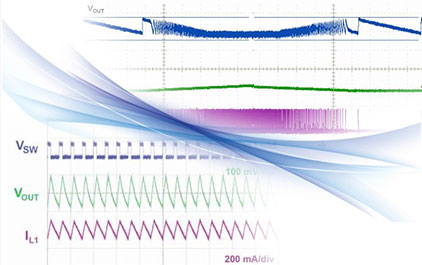

未学习 变频降压型变换器的控制策略(上)

未学习 变频降压型变换器的控制策略(上)

-

未学习 变频降压型变换器的控制策略(下)

未学习 变频降压型变换器的控制策略(下)

-

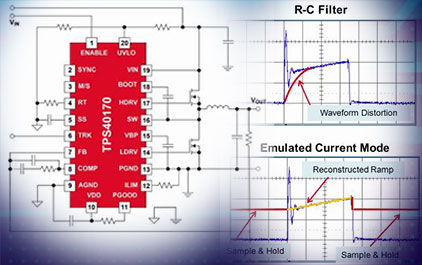

未学习 定频降压型变换器的控制策略(上)

未学习 定频降压型变换器的控制策略(上)

-

未学习 定频降压型变换器的控制策略(下)

未学习 定频降压型变换器的控制策略(下)