MOSFET

最新课程

- TI 高精度实验室 - 数据转换器:使用精密ADC测量RTD

- 如何利用高速比较器优化系统设计

- TPS546D24S 和 TPSM8S6C24 中的扩展安全功能

- 高侧开关深入研讨

- TI 高精度实验室 - 微控制器 (MCU)

- TI 高精度实验室 - CPU内核

- 三种直流/直流控制模式的实际比较

- 电源多路复用器深度培训

- TI Edge AI Studio:用于边缘 AI 设计的免费软件开发工具

- Edge AI Studio 概述

热门课程

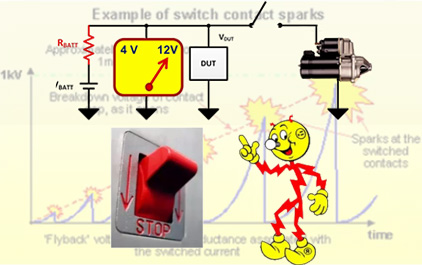

4.5.1振铃及其成因

运放电路的稳定性

用过运放的人都知道

不合理的设计会造成运放的自激振荡

一般教科书是按照

鸡生蛋蛋孵鸡的原理来解释自激振荡的

鸡生蛋蛋生孵鸡的原理来解释自激振荡的

那么无论是反相放大还是同相放大

引入的总是负反馈

实际运放的寄生的低通环节会导致相移

每阶低通相移最大90度

当存在三阶以上的滤波器的时候

就一定存在某个频率分量

恰好相移是180度

这就是负反馈变成正反馈,就是蛋可以生鸡

如果该频率对应的增益还能大于1

也就是平均一只鸡的产蛋率大于一的话

那么自激振荡就产生了

由此我们得出这样的运放稳定条件

要么让反馈相移达不到180度

鸡根本就没有办法下蛋

要么降低增益,平均一只鸡下不了一个蛋

以上理论呢,并不完美

例如呢,它没有办法解释单位增益稳定运放

和比较器振荡这两个现象

那么单位增益稳定运放

是这么回事,只有这种运放才能做缓冲器用途

其它运放非要放大倍数达到一定程度才是稳定的

而电压比较器呢,本质是运放但它不存在正反馈

但仍然会发生振荡

我们有必要呢从更微观的角度去认识

振荡是如何发生的,接下来我们将分几小节来讲述

振荡的成因以及消除振荡的方法

本课内容呢位于附录,运放电路的稳定性

振铃,1振铃

我们经常能够听到一个词,振铃

那么振铃是如何产生的,它与振荡有什么关系呢

如图所示的电路可以仿真出不同程度的振铃效果

三个运放都被接成了同相输入

采用输入是一样的信号

三个运放的反馈支路呢分别加上了 RC 延迟

根据低通滤波器的计算呢

OP1 的反馈延迟最大, OP3 的最小

瞬时现象仿真

发生了振荡

我们对振荡进行局部放大可以看出

延迟环节越严重,振铃现象越严重

那么振铃是由负反馈环节的延迟产生的

运放这种电子元件的本质是忠实的将

UP-UN 放大 A 倍,开环增益倍上万倍

那么如果反馈环节没有延迟

那么输出电压将是类似于 VF3

红色这样的波形

由于压摆率限制

慢慢上升到,但是不会过充不会振铃

它的稳定值

但是如果反馈环节有延迟

当我的输出电压明明已经达到 UP

而 UN 的电压

由于延迟它还没有达到,那么对运放来说

它依然会去增大输出电压,以使得 UN 接近 UP

于是这样一来呢

UO 就产生过冲,然后后来它又发现又大了它又

把它往小调,振铃就是这么产生的

我们将 OP1 的反馈环节的电容继续增大

增大到 20nF

增大反馈延迟我们发现

VF1 的输出更剧烈的

振荡了接近于振荡

但它还不是振荡

我们不考虑运放本身的性质

负反馈延迟呢,主要来源于两个地方

一个是

运放的电容性负载

另外一个呢,是运放的反相输入端的寄生电容

电容性负载

位于 A.2

我们在调试运放电路

特别是高速运放的时候,有可能有过这样的经历

电路一切正常,但是当我把示波器的探头

接在运放输出端的时候

示波器显示的波形是振荡的

那么这一现象的原因呢

是电容性负载带来的反馈延迟

示波器探头会引入电容性负载

如图所示

运放一定存在输出阻抗 RO

也就是内阻

那么 C2 ,负载电容

是由于各种原因

接上去的电容有可能真实负载就是电容

也有可能是示波器探头这种意外引入的

那么

这个延迟造成了振荡怎么处理呢

我们可以采用有源探头

它引入电容非常小

或者我们还可以采用变通的办法

也就是说

在输出

探头先接一个电阻

再去接到

运放的输出

瞬时现象仿真

由于电容器负载已经被串联的电阻

屏蔽了,所以呢串电阻的情况下没有振铃

而直接接电容,也就接示波器探头的地方发生了振铃

反相输入端的寄生电容

位于 A.3

我们再教 PCB 布线规范的时候

芯片可靠去耦和敷设地铜的道理,很多人听说过

但是对于运放反相输入端引脚下面,不要敷铜

是为什么

大部分是不知道的

为什么同相输入端就没有这个顾虑呢

我们来仿真,电路接成同相比例放大电路

OP1 和 OP2 的区别呢

只有反相输入端,电容

我们故意寄生两个电容,寄生电容的大小不一样

显然呢反馈回来的 RF 和 C

这是形成一个低通,造成了延迟

通过仿真可以看出呢

PCB 布线不良,也就是说

反相输入端引脚下面的地铜带来额外的

电容会增大反馈延迟,进而带来振铃

1nF 的时候有振铃

100pF 的时候还没有

我们下面讨论一下,同相输入端引入额外

电容会发生什么

我们给信号源呢加点内阻

然后呢给 OP2 ,就是不会发生振铃的这个

给它的同相端,给它加了一个大电容

结果我们仿真发现

OPR 虽然引入了额外的同相输入端电容

但是振铃呢并没有发生

红色的

是同相端引入的,没有电容

反相端还是会振

本课小结

振铃产生的原因

好,振铃产生呢是由于

输出电压反馈回反相比较端的时候有延迟

以至于运放,运放的作用是什么

是让反相输入端电压去等于同相端

那么明明输出电压已经增大到相等了

但是由于反馈延迟,它认为还没有等

那只有继续增大

等到继续增大的命令到了以后

它实际上已经过头了

那么周而复始地就发生了振铃

反馈延迟越大

过程就会越多

它涨多了又发现不对劲了又变小

变小又变大,这就是振铃

负载电容也会造成反馈延迟

由于

运放总是有输出阻抗的

输出阻抗 RO 和电容性负载

也构成一个低通滤波器

反馈回反相输入端

所以呢负载电容也会造成

延迟

那么消除负载电容延迟的办法呢

就必须给这支电容串电阻

破坏掉它的低通条件

那么

有电阻的时候,振铃消失

没有电阻的时候,振荡

运放的反相输入端电容也会造成延迟

反馈电阻 RF

和运放反相输入端底下的寄生电容也是构成低通

造成延迟

振荡

而运放同相端呢

同相端的电容跟反馈没有关系

它产生的效果也就是把你的输入信号

它压摆率降低了,有一个低通输入信号低通了

没那么陡峭变化而已

但它不会造成振铃

我们可以看到,反相端有电容会振同相端是不会振的

好,这节课就到这里

-

未学习 1.1.1电压源

未学习 1.1.1电压源

-

未学习 1.1.2电流源

未学习 1.1.2电流源

-

未学习 1.2.1电阻与电容

未学习 1.2.1电阻与电容

-

未学习 1.2.2电感

未学习 1.2.2电感

-

未学习 1.3阻抗与滤波器

未学习 1.3阻抗与滤波器

-

未学习 1.4实际电容与电源滤波

未学习 1.4实际电容与电源滤波

-

未学习 1.5热阻与散热

未学习 1.5热阻与散热

-

未学习 2.1电路搭建与瞬时现象仿真

未学习 2.1电路搭建与瞬时现象仿真

-

未学习 2.2其他有用的工具

未学习 2.2其他有用的工具

-

未学习 3.1.1二极管的性质

未学习 3.1.1二极管的性质

-

未学习 3.1.2二极管的动态特性

未学习 3.1.2二极管的动态特性

-

未学习 3.1.3二极管的分类

未学习 3.1.3二极管的分类

-

未学习 3.2.1NPN型三极管与恒流源放电电路

未学习 3.2.1NPN型三极管与恒流源放电电路

-

未学习 3.2.2PNP型三极管与恒流源充电电路

未学习 3.2.2PNP型三极管与恒流源充电电路

-

未学习 3.3.1共射放大电路一般性质

未学习 3.3.1共射放大电路一般性质

-

未学习 3.3.2放大电路的直流偏移

未学习 3.3.2放大电路的直流偏移

-

未学习 3.3.3共射放大电路的失真

未学习 3.3.3共射放大电路的失真

-

未学习 3.3.4共射放大电路的阻抗与密勒效应

未学习 3.3.4共射放大电路的阻抗与密勒效应

-

未学习 3.3.5共射放大电路的设计

未学习 3.3.5共射放大电路的设计

-

未学习 3.3.6.1共射放大电路增大放大倍数

未学习 3.3.6.1共射放大电路增大放大倍数

-

未学习 3.3.6.2选频放大电路

未学习 3.3.6.2选频放大电路

-

未学习 3.3.6.3高频滤波与高频增强

未学习 3.3.6.3高频滤波与高频增强

-

未学习 3.4差分放大电路

未学习 3.4差分放大电路

-

未学习 3.5.1共集放大电路基本特性

未学习 3.5.1共集放大电路基本特性

-

未学习 3.5.2甲类功率放大电路

未学习 3.5.2甲类功率放大电路

-

未学习 3.5.3乙类功率放大电路

未学习 3.5.3乙类功率放大电路

-

未学习 3.5.4甲乙类功率放大电路

未学习 3.5.4甲乙类功率放大电路

-

未学习 3.5.5共射共集组合放大电路

未学习 3.5.5共射共集组合放大电路

-

未学习 3.6.1共基放大电路基本特性

未学习 3.6.1共基放大电路基本特性

-

未学习 3.6.2共基共射放大电路

未学习 3.6.2共基共射放大电路

-

未学习 3.7场效应管概述

未学习 3.7场效应管概述

-

未学习 4.1.1反相比例运算电路

未学习 4.1.1反相比例运算电路

-

未学习 4.1.2同相比例运算电路

未学习 4.1.2同相比例运算电路

-

未学习 4.1.3加法和减法运算电路

未学习 4.1.3加法和减法运算电路

-

未学习 4.1.4直流偏置电路

未学习 4.1.4直流偏置电路

-

未学习 4.1.5积分和微分运算电路

未学习 4.1.5积分和微分运算电路

-

未学习 4.1.6PID运算放大电路

未学习 4.1.6PID运算放大电路

-

未学习 4.2.1轨至轨与运放供电

未学习 4.2.1轨至轨与运放供电

-

未学习 4.2.2运放的带宽与压摆率

未学习 4.2.2运放的带宽与压摆率

-

未学习 4.2.3输入阻抗与偏置电流

未学习 4.2.3输入阻抗与偏置电流

-

未学习 4.2.4零漂移放大器与电流反馈放大器

未学习 4.2.4零漂移放大器与电流反馈放大器

-

未学习 4.3.1差分放大器

未学习 4.3.1差分放大器

-

未学习 4.3.2仪表放大器

未学习 4.3.2仪表放大器

-

未学习 4.3.3.1电流检测方法

未学习 4.3.3.1电流检测方法

-

未学习 4.3.3.2电流检测放大器

未学习 4.3.3.2电流检测放大器

-

未学习 4.3.4可变增益放大器与压频转换器

未学习 4.3.4可变增益放大器与压频转换器

-

未学习 4.3.5隔离放大器与音频功率放大器

未学习 4.3.5隔离放大器与音频功率放大器

-

未学习 4.4.1简单有源滤波器

未学习 4.4.1简单有源滤波器

-

未学习 4.4.2有源滤波器设计软件

未学习 4.4.2有源滤波器设计软件

-

未学习 4.4.3高频馈通与运放带宽

未学习 4.4.3高频馈通与运放带宽

-

未学习 4.5.1振铃及其成因

未学习 4.5.1振铃及其成因

-

未学习 4.5.2开环增益与相移

未学习 4.5.2开环增益与相移

-

未学习 4.5.3相位补偿

未学习 4.5.3相位补偿

-

未学习 4.5.4比较器与正反馈

未学习 4.5.4比较器与正反馈

-

未学习 4.6.1噪声的基本概念

未学习 4.6.1噪声的基本概念

-

未学习 4.6.2噪声的有效值计算

未学习 4.6.2噪声的有效值计算

-

未学习 4.6.3噪声计算软件

未学习 4.6.3噪声计算软件

-

未学习 电力MOSFET开关概述及工作原理

未学习 电力MOSFET开关概述及工作原理

-

未学习 MOSFET的导通电阻

未学习 MOSFET的导通电阻

-

未学习 MOSFET的主要参数

未学习 MOSFET的主要参数

-

未学习 MOSFET的开关时间

未学习 MOSFET的开关时间

-

未学习 MOSFET的损耗分析

未学习 MOSFET的损耗分析

-

未学习 MOSFET的驱动

未学习 MOSFET的驱动

-

未学习 MOSFET栅极驱动的振荡现象

未学习 MOSFET栅极驱动的振荡现象

-

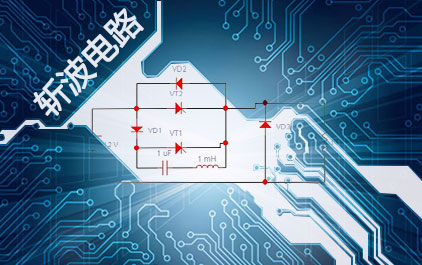

未学习 斩波电路(一) —— 概述和降压斩波电路原理

未学习 斩波电路(一) —— 概述和降压斩波电路原理

-

未学习 斩波电路(二) —— 降压斩波电路仿真

未学习 斩波电路(二) —— 降压斩波电路仿真

-

未学习 斩波电路(三) —— 电荷泵电路

未学习 斩波电路(三) —— 电荷泵电路

-

未学习 斩波电路(四) —— 升压斩波电路原理

未学习 斩波电路(四) —— 升压斩波电路原理

-

未学习 斩波电路(五) —— 升压斩波电路仿真

未学习 斩波电路(五) —— 升压斩波电路仿真

-

未学习 斩波电路(六) —— 升降压斩波电路

未学习 斩波电路(六) —— 升降压斩波电路

-

未学习 斩波电路(七) —— Cuk, Speic, Zeta斩波电路

未学习 斩波电路(七) —— Cuk, Speic, Zeta斩波电路

-

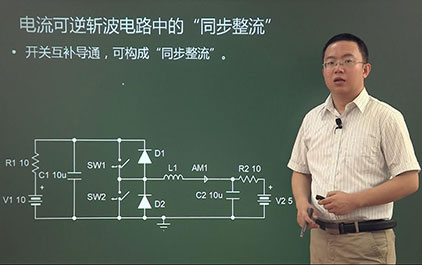

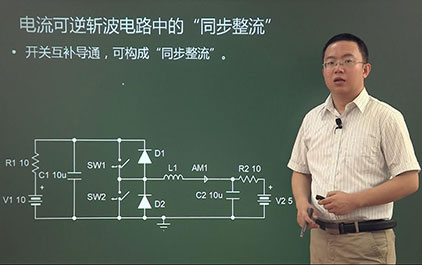

未学习 电流可逆斩波电路(一)

未学习 电流可逆斩波电路(一)

-

未学习 电流可逆斩波电路(二)

未学习 电流可逆斩波电路(二)

-

未学习 5.3单相整流电路

未学习 5.3单相整流电路

-

未学习 逆变电路(一)

未学习 逆变电路(一)

-

未学习 逆变电路(二)

未学习 逆变电路(二)

-

未学习 隔离驱动(一)

未学习 隔离驱动(一)

-

未学习 隔离驱动(二)

未学习 隔离驱动(二)

-

未学习 隔离驱动(三)

未学习 隔离驱动(三)