电机驱动

最新课程

- TI 高精度实验室 - 数据转换器:使用精密ADC测量RTD

- 如何利用高速比较器优化系统设计

- TPS546D24S 和 TPSM8S6C24 中的扩展安全功能

- 高侧开关深入研讨

- TI 高精度实验室 - 微控制器 (MCU)

- TI 高精度实验室 - CPU内核

- 三种直流/直流控制模式的实际比较

- 电源多路复用器深度培训

- TI Edge AI Studio:用于边缘 AI 设计的免费软件开发工具

- Edge AI Studio 概述

热门课程

C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

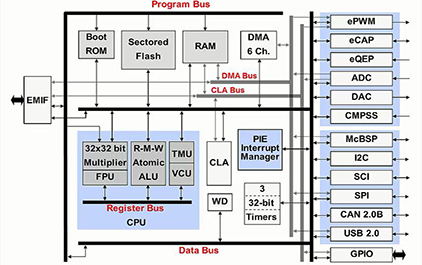

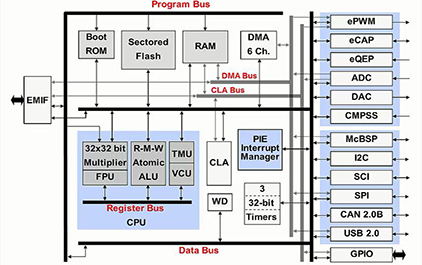

接下来 我们看看外部存储器接口EMIF口

C2000系列里面的子系列

它能支持EMIF接口 老的比如F281

F28335 F2823X等 新的比如F2837XD

和37XS

我们今天主要讲的是C2837xD的EMIF接口

EMIF接口它的主要作用是

提供一个接口 将CPU EMA

和CIA

等接到外部的存储器设备上

F2837XD 有两个EMFI接口 EMIF1和EMIF2

其中EMIF1是CPU1和CPU2共享的

EMIF2只能被CPU1所用

EMIF1它是一个16位或32位的接口

能被CPU1、CPU1的DMA、CPU2、CPU2的DMA

四个总线所访问

而EMIF2只能被CPU1和CPU1 CLA1访问

这个地方要注意了

也就是说 EMIF2能被CPU1和CPU1的CLA1所访问

CLA1我们知道是协处理器单元

它的目的是说 我是可以和CPU1并列运行的

能够增大我芯片的处理能力

而假如说我们的CLA能通过EMIF口访问外部的存储器设备的话

数据从外部导入到我的芯片内部的话

就不需要CPU参与了

更能够将CPU和CLA分别独立运行

进一步提高芯片的处理能力

因此 EMIF1和EMIF2 这两个EMIOF口最主要的区别有两点

第一EMIF1能被CPU1和CPU2 两个CPU所访问

EMIF2只能被CPU1访问

第二点 EMIF1能被CPU1和DMA1两种总线访问

EMIF2只能被CPU1和CLA1两种总线访问

那F2837X的EMIF接口都支持同步的SDRAM和异步的SRAM Nor Flash的

存储器设备

同步RAM和异步RAM的特点不同

接口也不同

那么接下来看看它们是如何接线的

我们看这个图中 首先看下面这块

这块这个信号管脚pin脚是被同步和异步所共享的

这个地方包含写入使能 主地址引脚

字节地址引脚 数据总线和地址总线

不管同步异步 都需要这几个信号

上面这两块分别是同步的SDRAM 和异步RAM的接口的控制性

针对同步里面主要包含片选 列地址 行地址

以及它的时钟信号 时钟使能等这些控制信号

针对异步的它主要有片选 输出使能

等待输入 以及读写控制

因此 假如说 我的EMIF接口

接的是外部的同步RAM的话 那它主要用的上面五根线

和下面五根线

假如针对异步的话 主要是用中间这四根线

和下面的这五根线

我们来看看EMFI1和EMFI2的配置

前面说了 EMIF1最大的数据宽度是32位

EMIF2最大的数据宽度是16位

EMIF1的最大地址线宽度是22位

也就是说 它能支持4兆的地址寻址空间

而EMIF2它只有12位的

它只能支持4K的地址寻址空间

针对同步的 它都能支持一个CS0片选

针对异步的 EMIF1能支持3个片选

EMIF2只能支持1个片选

我们看看针对同步SDRAM接口的话

2837X的EMIF接口能支持1组 2组和四组banks的RAM

这主要是由管脚EMBA 这两个1和0

这两个管脚控制

同时SDRAMD 支持两个或三个时钟周期的延迟

而且它具有自刷性和掉电模式

其中 自刷性可以允许SDRAM可以在低功耗的模式下

保存内容

不需要MCU的时钟信号 就可以刷新存储的数据

因此它的功耗更低

那么针对异步RAM的话

它能支持叫慢存储器件输入的一个等待

而且这个等待时间是可以通过编程设定的

同时 我编程的读写周期里面

包括设置保持选通等等整个系统时钟周期

都可以通过编程集成器来控制

针对异步RAM的话

它的数据总线的宽度是根据程序来设置

也就是它的数据总线宽度是可编程的

那么主要有关键字 asynchronous

假如是0的话 就是8位的

假如是1 就是16位

假如是2 就是32位的

就是不管是针对同步的RAM还是异步的RAM的话

我们的EMIF接口配置相当灵活

使用起来比较方便

具体可以参考手册上的各个集成器的说明

我们再看EMIF接口的性能

我们说EMIF接口 它的性能主要体现在访问速度上

也就是我去访问外部存储器的话

它的访问速度到底有多快

针对同步和异步的RAM 它的访问速度不一样的

举个例子 假如我们的F2837X工作在200兆赫兹的话

针对同步RAM DRAM的话 它的读是14个CPU周期

它的写的话是9个时钟周期

因此 它的吞吐量是14.3

和22.3兆

针对异步RAM的话 读是9个系统周期

写是5个系统周期

其实上面也说了

针对我们的异步RAM的话 它的读写 等待啊

等这些周期这些都是可以编程设置的

举个例子 如果它的读写设置周期是

141的话 也就是说4是一个CPU周期

选通是4个CPU周期 保持是一个系统周期的话

然后增加两个周期总线启动

一个周期速度延迟到CPU的延迟的话

总共是9个CPU周期

因此我们可以看到

针对同步和异步RAM

它的访问时间 速度以及吞吐量是不一样的

-

未学习 C2837x入门指南(一) — 概述

未学习 C2837x入门指南(一) — 概述

-

未学习 C2837x入门指南(二) — 芯片架构

未学习 C2837x入门指南(二) — 芯片架构

-

未学习 C2837x入门指南(三) — 开发环境

未学习 C2837x入门指南(三) — 开发环境

-

未学习 C2837x入门指南(四) — 外设寄存器操作

未学习 C2837x入门指南(四) — 外设寄存器操作

-

未学习 C2837x入门指南(五) — 复位和中断

未学习 C2837x入门指南(五) — 复位和中断

-

未学习 C2837x入门指南(六) — 系统初始化

未学习 C2837x入门指南(六) — 系统初始化

-

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

未学习 C2837x入门指南(七) — 模拟子系统 ADC DAC CMP SDFM(上)

-

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

未学习 C2837x入门指南(八) — 模拟子系统 ADC DAC CMP SDFM(下)

-

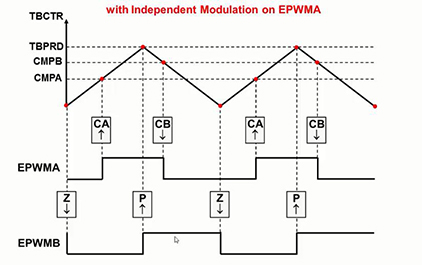

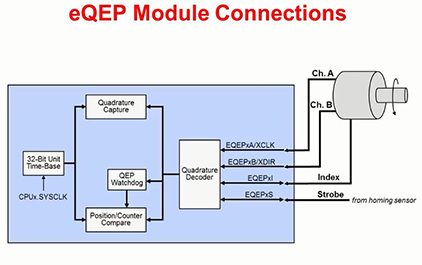

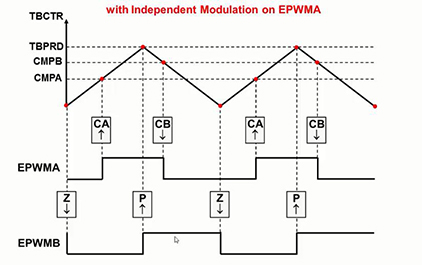

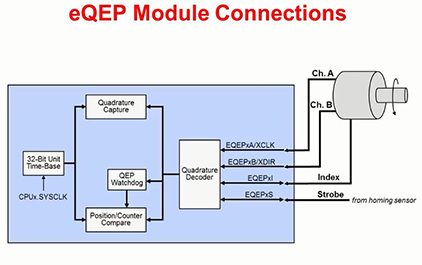

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

未学习 C2837x入门指南(九) — 控制类外设PWM CAP QEP(上)

-

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

未学习 C2837x入门指南(十) — 控制类外设PWM CAP QEP(中)

-

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

未学习 C2837x入门指南(十一) — 控制类外设PWM CAP QEP(下)

-

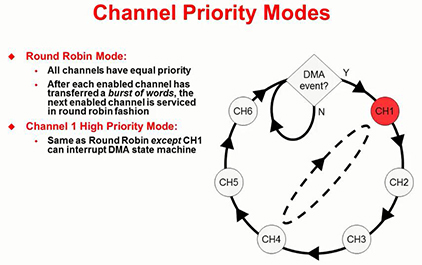

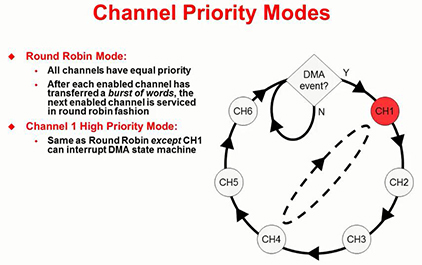

未学习 C2837x入门指南(十二) — DMA模块(上)

未学习 C2837x入门指南(十二) — DMA模块(上)

-

未学习 C2837x入门指南(十三) — DMA模块(下)

未学习 C2837x入门指南(十三) — DMA模块(下)

-

未学习 C2837x入门指南(十四) — CLA模块

未学习 C2837x入门指南(十四) — CLA模块

-

未学习 C2837x入门指南(十五)—系统设计之调试仿真

未学习 C2837x入门指南(十五)—系统设计之调试仿真

-

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

未学习 C2837x入门指南(十六)—系统设计之EMIF外接存储器接口

-

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

未学习 C2837x入门指南(十七)—系统设计之Flash编程和配置

-

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

未学习 C2837x入门指南(十八)—系统设计之DCSM双代码安全模块

-

未学习 C2837x入门指南(十九)—双内核之间的通信

未学习 C2837x入门指南(十九)—双内核之间的通信

-

未学习 C2837x入门指南(二十)—通信系统之SPI

未学习 C2837x入门指南(二十)—通信系统之SPI

-

未学习 C2837x入门指南(二十一)—通信系统之SCI

未学习 C2837x入门指南(二十一)—通信系统之SCI

-

未学习 C2837x入门指南(二十二)—通信系统之McBSP

未学习 C2837x入门指南(二十二)—通信系统之McBSP

-

未学习 C2837x入门指南(二十三)—通信系统之IIC

未学习 C2837x入门指南(二十三)—通信系统之IIC

-

未学习 C2837x入门指南(二十四)—通信系统之USB

未学习 C2837x入门指南(二十四)—通信系统之USB

-

未学习 C2837x入门指南(二十五)—通信系统之CAN

未学习 C2837x入门指南(二十五)—通信系统之CAN

-

未学习 C2837x入门指南(二十六)—开发工具汇总

未学习 C2837x入门指南(二十六)—开发工具汇总

-

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

未学习 C2837x入门指南(二十七)—C2000开发所需软件工具(一)

-

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)

未学习 C2837x入门指南(二十八)—C2000开发所需软件工具(二)